Изобретение относится к специализированным средствам вычислительной техники и предназначено для моделирования процесса решения задач на ЭВМ.

Цель изобретения - расширение функциональных возможностей за счет моделирования процесса решения задач, имеющих различные степени сложности, на ЭВМ с несколькими процессорами.

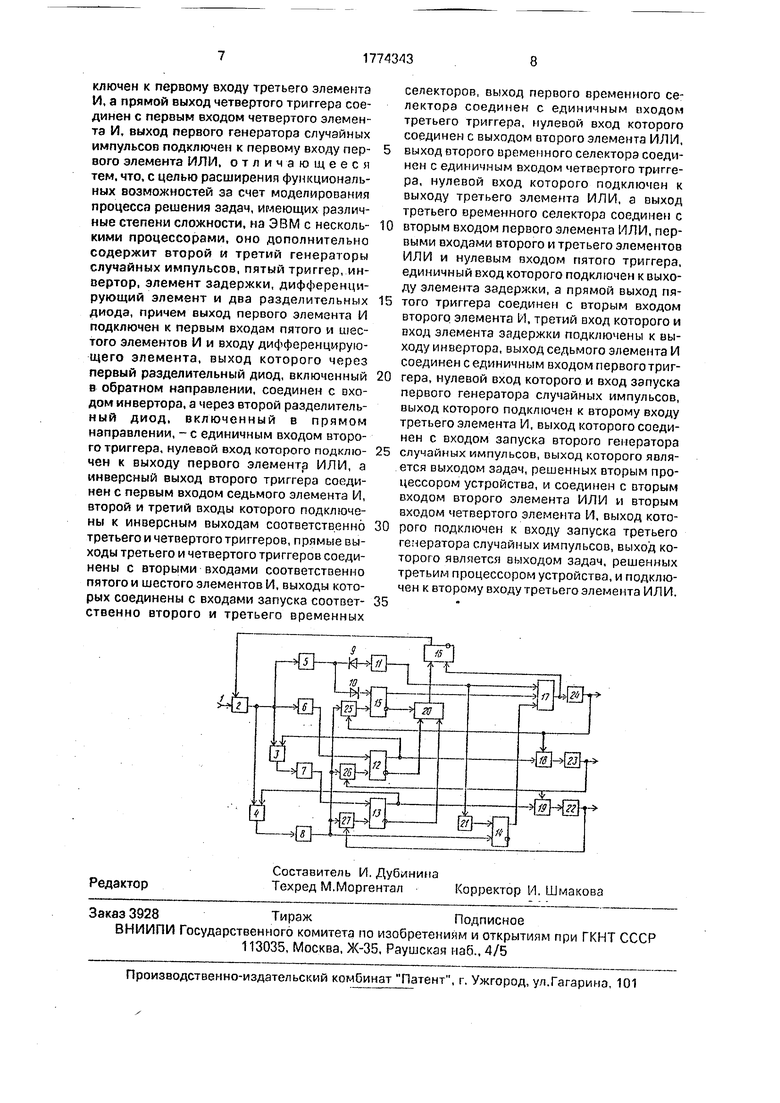

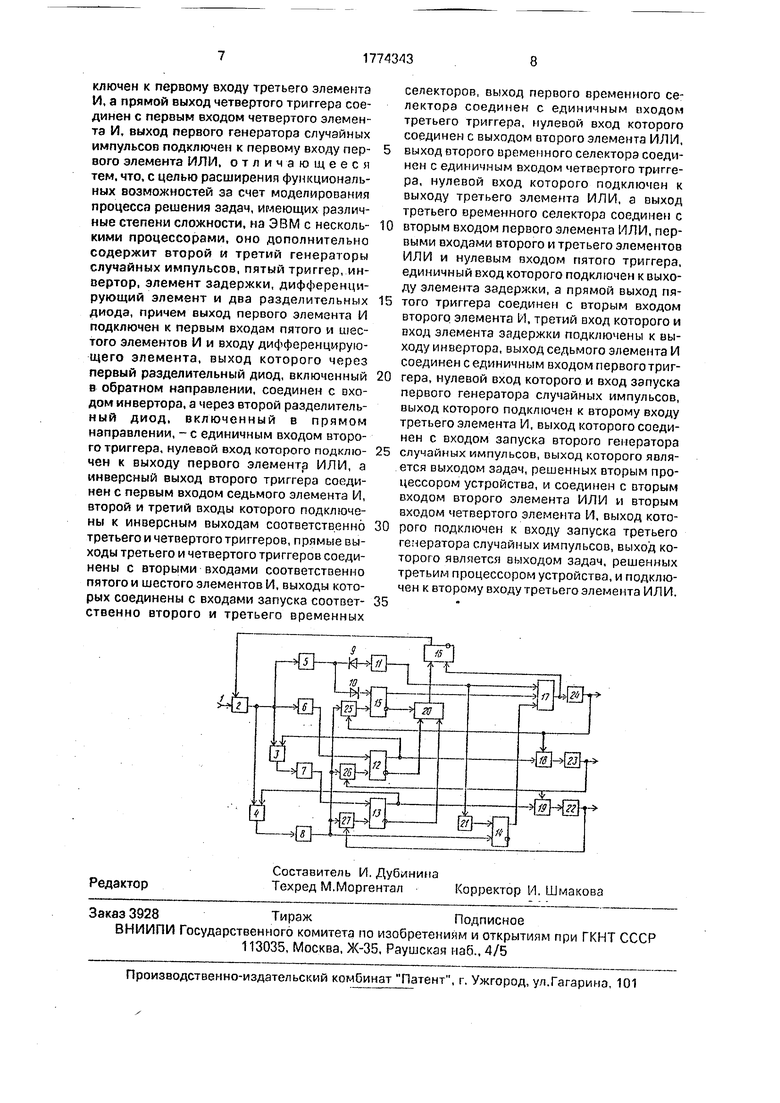

На чертеже представлена структурная схема устройства.

Устройство содержит оход 1 заявок, первый 2, пятый 3 и шестой 4 элементы И, дифференцирующий элемент 5, первый 6. второй 7 и третий 8 временные селектооы,

первый 9 и второй 10 разделительные диоды, инвертор 11, третий 12, четвертый 13, пятый 14, второй 15 и первый 16 триггеры, второй 17, третий 18, четвертый 19 и седьмой 20 элементы И, элемент 21 задержки, первый 22, второй 23 и третий 24 генераторы случайных импульсов, первый 25, второй 26 и третий 27 элементы ИЛИ.

Потоки задач на решение, поступающие на вход устройства, представляют собой случайные импульсные последовательности длительности, интервалы между которыми и длительности которых распределены по определенным (разным или одним и тем же) законам возникновения требований на про VI

СО

.N

W

ведение вычислительных работ в исследуемой системе.

Генераторы 22-24 моделируют работу процессоров. Временной интервал от момента запуска каждого генератора до появления импульса на его выходе случаен и распределен по принятому закону моделирования. Закон распределения случайных импульсов на выходах каждого генератора один и тот же, так как они моделируют однотипные процессоры.

Дифференцирующий элемент 5 преобразует импульсный сигнал определенной длительности в два коротких разнополяр- ных импульса. Положительный импульс соответствует Фронту, а отрицательный - срезу входного сигнала.

Время задержки элемента 21 задержки равно длительности коротких импульсов, появляющихся на выходе дифференцирующего элемента 5.

Время селекции временных селекторов 6-8 одинаково, так как оно соответствует объему памяти однотипных процессоров. При наличии на входе каждого временного селектора импульса длительностью больше или равной времени селекции (т гс) на его выходе появляется короткий импульс.

Алгоритм работы устройства следую-, щий. Поступающую в устройство задачу на решение (заявка на обслуживание) загружают последовательно в процессоры. Об окончании загрузки части заявки в процессор сигнализирует импульс, появляющийся на выходе соответствующего временного селектора. При появлении этого импульса начинается загрузка следующей части заявки в следующий процессор. Выбор времени селекции каждого временного селектора зависит от объема памяти процессоров моделируемой системы, поэ тому появление импульса на выходе временного селектора имитирует переполнение соответствующего процессора. При полной загрузке заявки в устройство начинается ее обслуживание, которое происходит последовательно в тех процессорах, которые оказались загружены. Результаты обслуживания заявки (решения задачи) на каждом этапе (в каждом процессоре) поступают на соответствующие выходы устройства. Если обьема памяти процессоров не хватает для полной загрузки заявки, ее обслуживание не осуществляется, а заявка теряется. Заявка, поступившая в период обслуживания предыдущей заявки, теряется.

Устройство может работать в следующих режимах работы: поступившая заявка не превышает объема всех процессоров, поступившая заявка превышает объем всех процессоров.

Устройство работает следующим образом.

В исходном состоянии во всех режимах

работы триггеры 15, 12 и 13 находятся в состоянии, при котором на их инверсных выходах имеются высокие потенциалы, в результате чего элемент И 20 открыт. Нэ прямых выходах триггеров 15. 12 и 13 имеется низкий потенциал, в результате чего элементы И 3, 4, 17-19 закрыты. Триггер 14 находится в состоянии, при котором элемент И 17 открыт по соответствующему входу. Триггер 16 находится в состоянии, при котором элемент И 2 открыт по соответствующему входу.

Режим 1: на вход устройства поступает задача, объем которой не превышает объема всех процессоров.

На вход 1 устройства поступает импульс длительностью т, причем т п Тс, где гс - время селекции каждого временного селектора, п - количество временных селекторов

в устройстве (процессоров в моделируемой системе), которое на чертеже равно трем. В качестве примера рассмотрим случай, когда гс т 2 гс, т.е. случай, когда поступившая задача занимает объем двух процессоров.

Импульс через открытый элемент И 2 поступает на вход временного селектора 6 и на вход дифференцирующего элемента 5, на выходе которого появляется короткий положительный импульс, который проходит

через диод 10 и, поступая на единичный вход триггера 15, опрокидывает его, так что элемент И 17 открывается по двум входам, а элемент И 20 закрывается. Через время гс после начала поступления входного импульса на выходе временного селектора 6 появляется импульс, который, поступая на единичный вход триггера 12, опрокидывает его, в результате чего закрывается элемент И 20, открываются элементы И 18. 3. После

этого входной импульс с выхода элемента И 2 через открытый элемент И 3 поступает на вход временного селектора 7. Таким образом имитируются полная загрузка первого процессора и начало загрузки второго процессора. В момент окончания поступления входного импульса на выходе дифференцирующего элемента 5 появляется короткий импульс отрицательной полярности, который через диод 9, инвертор 11, элемент И 17

поступает на вход запуска генератора 24 Случайных импульсов (имитируется начало работы первого процессора). Одновременно импульс с выхода элемента И 17 поступает на нулевой вход триггера 16,

опрокидывая его так, что элемент И 2 закрывается. Одновременно импульс с выхода инвертора 11 поступает на вход элемента 21 задержки. Через время, равное длительности этого короткого импульса, достаточное для того, чтобы импульс с выхода инвертора 11 прошел через элемент И 17, на выходе элемента 21 задержки появляется импульс, который поступает на вход триггера 14 и удерживает его в предыдущем состоянии. В момент окончания работы первого процессора на выходе генератора 24 появляется импульс, который поступает на выход устройства. Одновременно импульс с выхода генератора 24 через элемент ИЛ И 25 посту- пает на нулевой вход триггера 15, опрокидывая его, в результате чего элемент И 20 открывается по входу, а элемент И 17 закрывается. Одновременно импульс с выхода генератора 24, пройдя через открытый элемент И 18, запускает генератор 23 (имитируется начало работы второго процессора). По окончании работы второго процессора на выходе генератора 23 появляется импульс, который поступает на вы- ход устройства. Одновременно импульс с выхода генератора 23 поступает на вход элемента И 19, но так как этот элемент закрыт, импульс через него не проходит. Таким образом, данная задача была решена с использованием двух процессоров. Одновременно импульс с выхода генератора 23 через элемент ИЛ И 20 поступает на нулевой вход триггера 12, опрокидывая его, в результате чего элементы И 18 и 3 закрывают- ся, а на всех трех входах элемента И 20 имеется единичный уровень, который, поступая на единичный вход триггера 16, опрокидывает его. Таким образом, элемент И 2 открывается по второму входу, а схема приводится в исходное состояние.

Режим 2: на вход устройства поступает задача, объем которой превышает объем всех процессоров.

На вход 1 поступает импульс длительно- стью , причем г 3 гс . Этот импульс через открытый элемент И 2 поступает на элементы И 3 и 4, на входы временного селектора 6 и дифференцирующего элемента 5, на выходе которого появляется корот- кий импульс, который, пройдя через диод 10, опрокидывает триггер 15. Таким образом, элемент И 20 закрывается, а элемент И 17 открывается. Через время тс после начала поступления импульса опрокидывается триггер 12, в результате чего элемент И 20 закрывается, а элементы И 3 и 18 открываются (имитируется загрузка второго процессора). Через время 2 гс после начала

поступления входного сигнала на выходе временного селектора 7 появляется импульс, который опрокидывает триггер 13, в результате чего закрывается по третьему входу элемент И 20, а элементы И 4 и 19 открываются. Через время 3 гс после начала поступления входного сигнала на выходе временного селектора 8 появляется импульс, который опрокидывает триггер 14, в результате чего закрывается по третьему входу элемент И 17. Одновременно импульс с выхода временного селектора 8 через элементы ИЛИ 25-27 поступает на нулевые входы триггеров 15. 12 и 13 соответственно, опрокидывая их, в результате чего на входах элемента И 20 появляется единичный уровень, удерживающий триггер 16 в прежнем положении, при котором высоким потенциалом с его выхода элемент И 2 остается открытым. 8 момент окончания поступления входного сигнала на выходе дифференцирующего элемента 5 появляется короткий отрицательный импульс, который проходит через диод 9 и инвертор 11, где он инвертируется в положительный импульс и поступает на вход элемента 21 задержки и на вход элемента И 17. который закрыт по другому входу. Таким образом, заявка к обслуживанию (задача на решение) не принимается. Через время задержки, равное длительности короткого импульса на выходе инвертора 11 и достаточное для того, чтобы этот короткий импульс перестал действовать на первый выход элемента И 17, импульс на выходе элемента 21 задержки опрокидывает триггер 14, в результате чего закрывается элемент И 17, а схема приводится в исходное состояние.

Таким образом, если в результате загрузки поступившей задачи в процессоры окажется, что объема этих процессоров не хватает для полной загрузки, задача к решению не принимается.

Формула изобретения Устройство для моделирования процесса решения задач на ЭВМ, содержащее первый элемент И, первый вход которого является входом устройства, второй вход первого элемента И соединен с прямым выходом первого триггера, с второго по седьмой элементы И, три временных селектора, второй, третий и четвертый триггеры, три элемента ИЛИ, первый генератор случайных импульсов, выход которого является аыходом задач, решенных первым процессором устройства, выход первого элемента И соединен с входом запуска первого временного селектора, прямой выход второго триггера соединен с первым входом второго элемента И, прямой выход третьего триггера подключей к первому входу третьего элемента И, а прямой выход четвертого триггера соединен с первым входом четвертого элемента И. выход первого генератора случайных импульсов подключен к первому входу пер- вого элемента ИЛИ, отличающееся тем. что, с целью расширения функциональных возможностей за счет моделирования процесса решения задач, имеющих различные степени сложности, на ЭВМ с несколь- кими процессорами, оно дополнительно содержит второй и третий генераторы случайных импульсов, пятый триггер, ин- оертор, элемент задержки, дифференцирующий элемент и два разделительных диода, причем выход первого элемента И подключен к первым входам пятого и шестого элементов И и входу дифференцирующего элемента, выход которого через первый разделительный диод, включенный в обратном направлении, соединен с входом инвертора, а через второй разделитель- ный диод, включенный в прямом направлении, - с единичным входом второго триггера, нулевой вход которого подклю- чен к выходу первого элемента ИЛИ, а инверсный выход второго триггера соединен с первым входом седьмого элемента И, второй и третий входы которого подключены к инверсным выходам соответственно третьего и четвертого триггеров, прямые выходы третьего и четвертого триггеров соединены с вторыми входами соответственно пятого и шестого элементов И, выходы которых соединены с входами запуска соотоет- ственно второго и третьего временных

селекторов, выход первого временного селектора соединен с единичным входом третьего триггера, нулевой вход которого соединен с выходом второго элемента ИЛИ, выход второго временного селектора соединен с единичным входом четвертого триггера, нулевой вход которого подключен к выходу третьего элемента ИЛИ, а выход третьего временного селектора соединен с вторым входом первого элемента ИЛИ, первыми входами второго и третьего элементов ИЛИ и нулевым входом пятого триггера, единичный вход которого подключен к выходу элемента задержки, а прямой выход пятого триггера соединен с вторым входом второго элемента И, третий вход которого и вход элемента задержки подключены к выходу инвертора, выход седьмого элемента И соединен с единичным входом первого триггера, нулевой вход которого и вход запуска первого генератора случайных импульсов, выход которого подключен к второму входу третьего элемента И, выход которого соединен с входом запуска второго генератора случайных импульсов, выход которого является выходом задач, решенных вторым процессором устройства, и соединен с вторым входом второго элемента ИЛИ и вторым входом четвертого элемента И, выход которого подключен к входу запуска третьего генератора случайных импульсов, выход которого является выходом задач, решенных третьим процессором устройства, и подключен к второму входу третьего элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования процесса обслуживания приоритетных заявок | 1988 |

|

SU1580394A1 |

| Устройство для моделирования процесса обслуживания заявок | 1990 |

|

SU1742827A1 |

| Устройство для моделирования процесса обслуживания разноприоритетных заявок | 1989 |

|

SU1624452A1 |

| Устройство для моделирования систем массового обслуживания | 1989 |

|

SU1683029A1 |

| Устройство для моделирования процесса обслуживания заявок | 1986 |

|

SU1383390A1 |

| СЕЛЕКТОР ИМПУЛЬСОВ | 2006 |

|

RU2309532C1 |

| Устройство для моделирования процесса решения задач на ЭВМ | 1985 |

|

SU1292002A1 |

| СЕЛЕКТОР ИМПУЛЬСОВ | 2006 |

|

RU2325756C1 |

| СЕЛЕКТОР ИМПУЛЬСОВ | 2000 |

|

RU2168854C1 |

| Устройство для моделирования процесса решения задач на электронно-вычислительных машинах | 1984 |

|

SU1218394A1 |

Изобретение относится к специализированным средствам вычислительной техники и предназначено для моделирования процесса решения задач на ЭВМ. Цель изобретения - расширение функциональных возможностей за счет моделирования процесса решения задач, имеющих различные степени сложности, на ЭВМ с несколькими процессорами. Устройство содержит семь элементов И, три временных селектора, дифференцирующий элемент, два разделительных диода, инвертор, пять триггеров, элемент задержки, три элемента ИЛИ и три генератора случайных импульсов. Устройство обеспечивает следующий алгоритм работы. Поступающую на решение задачу поэтапно загружают в процессоры ЭВМ. После загрузки задачи начинается последовательный процесс ее решения. Каждый процессор обрабатывает определенный этап задачи, после чего выдает результат для дальнейшей обработки. Если объем памяти всех процессоров оказывается недостаточным для полной загрузки задачи, решение не происходит, а память процессоров освобождается, и ЭВМ готова к приему новой задачи, 1 ил. v Ј

/тЩЕЬт

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для моделирования систем массового обслуживания | 1985 |

|

SU1273942A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для моделирования систем массового обслуживания | 1989 |

|

SU1683029A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-11-07—Публикация

1989-07-11—Подача