строкой ассоциативного накопителя, так и с конъюнкцией выделенных строк.

Целью изобретения является расширение области применения устройства за счет обеспечения возможности одновременного осуществления ассоциативного поиска и фиксации количества несовпадений аргумента поиска как с отдельной выделенной строкой ассоциативного накопителя, так и с конъюнкцией выделенных строк.

Поставленная цель достигается тем, что в ассоциативное запоминающее устройство, содержащее накопитель, блок регистров опроса и маскирования данных, первый и второй регистры фиксации реакций, анализатор многократного совпадения, шифратор, дешифратор адреса, управляющие входы блока регистров опроса и маскирования данных являются управляющими входами устройства, информационными входами группы которого являются информационные входы блока регистров опроса и маскирования данных, выходы с первого по четвертый каждой группы которого подключены соответственно к пятому, четвертому, второму и третьему информационным входам элементов памяти соответствующего столбца накопителя, вторые выходы элементов памяти каждого столбца накопителя объединены и подключены к соответствующим информационным входам второго регистра фиксации реакций, управляющий вход которого является входом чтения устройства, информационными выходами группы которого являются информационные выходы второго регистра фиксации реакций, первые выходы элементов памяти каждой строки накопителя объединены и подключены к соответствующим входам первого регистра фиксации реакций, управляющий вход которого является входом чтения устройства, информационные выходы первой группы первого регистра фиксации реакций являются входами-выходами данных устройства, информационные выходы второй группы первого регистра фиксации реакций соединены с соответствующими входами данных анализатора многократного совпадения, управляющий входтсоторого соединен с управляющим входом шифратора и является входом задания режима устройства, выход состояния анализатора многократного совпадения является выходом состояния устройства, информационные выходы анализатора многократного совпадения соединены с соответствующими информационными входами шифратора, выходы которого соединены с информационными входами дешифратора и являются адресными входами-выходами устройства,

входом выборки которого является управляющий вход дешифратора, введен блок маскирования, к информационным входам первой группы которого подключены выходы дешифратора адреса, информационные входы второй группы блока маскирования являются входами-выходами данных устройства, управляющим входом которого является управляющий вход блока

0 маскирования, выходы которого подключены к объединенным первым входам элементов памяти соответствующих строк накопителя.

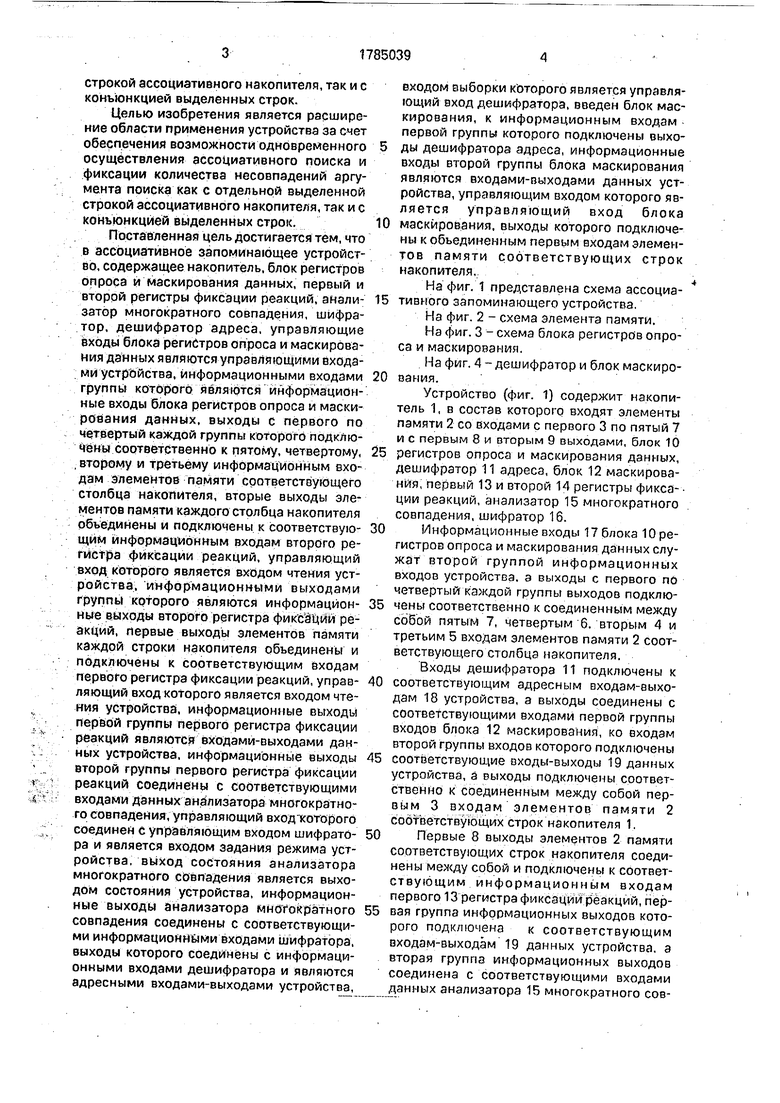

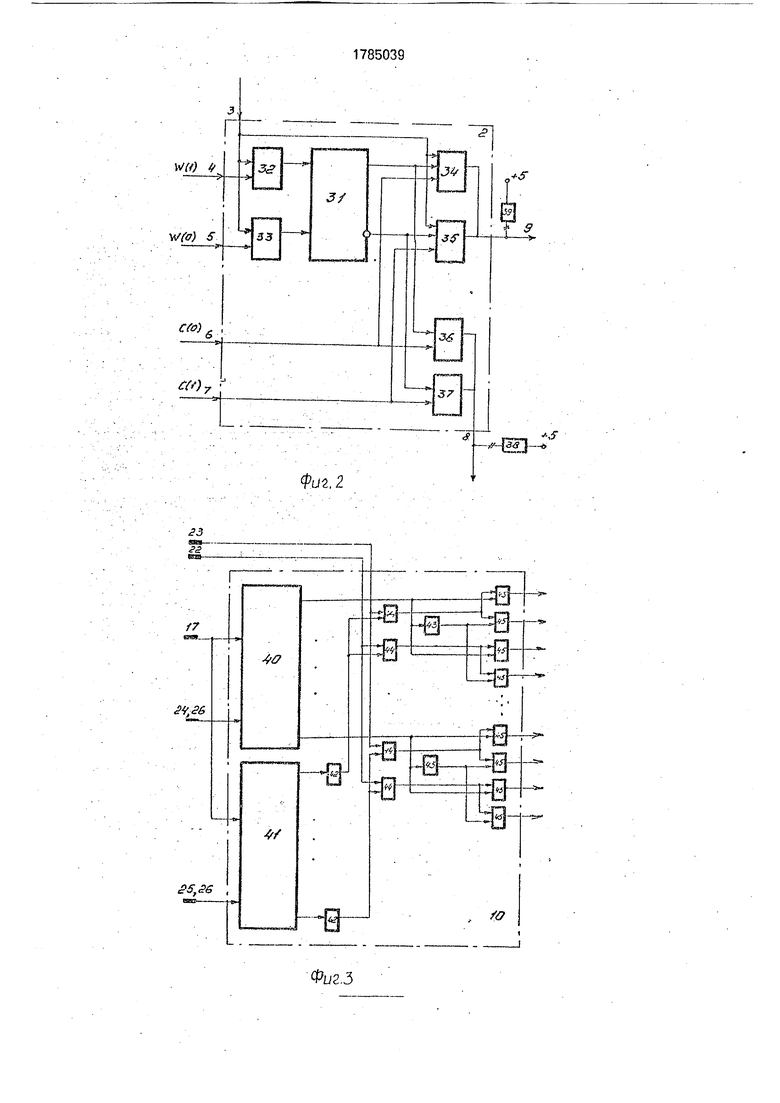

На фиг. 1 представлена схема ассоциа5 тивиого запоминающего устройства.

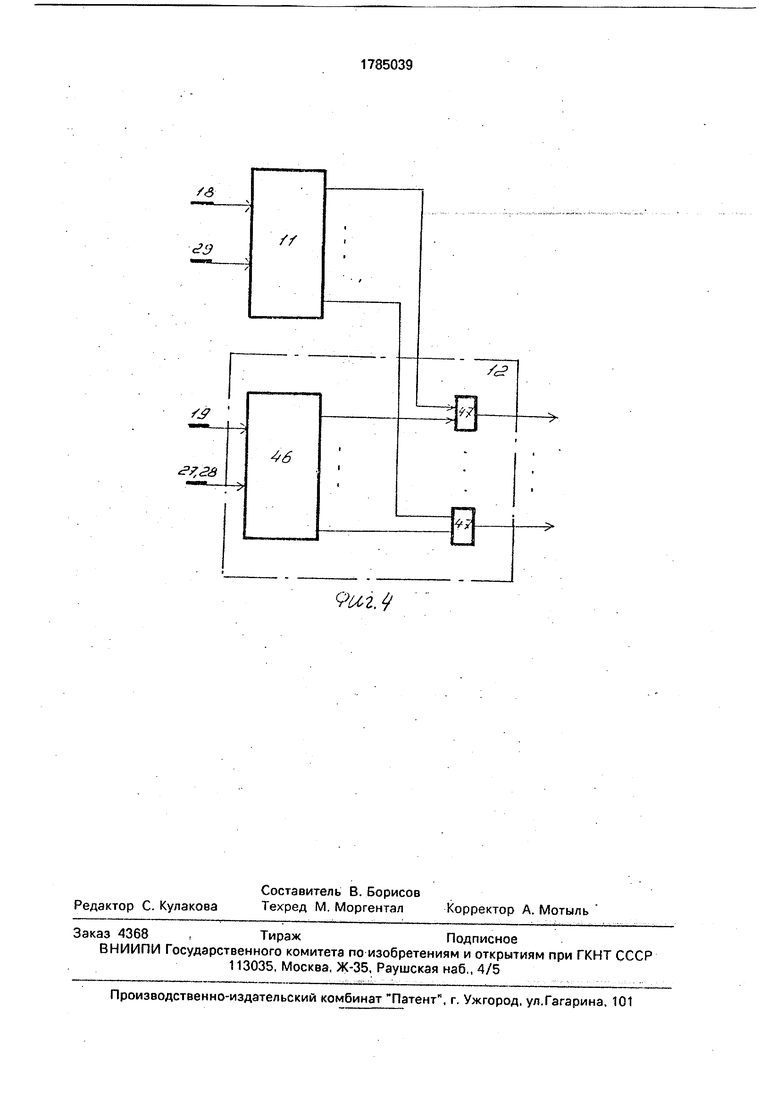

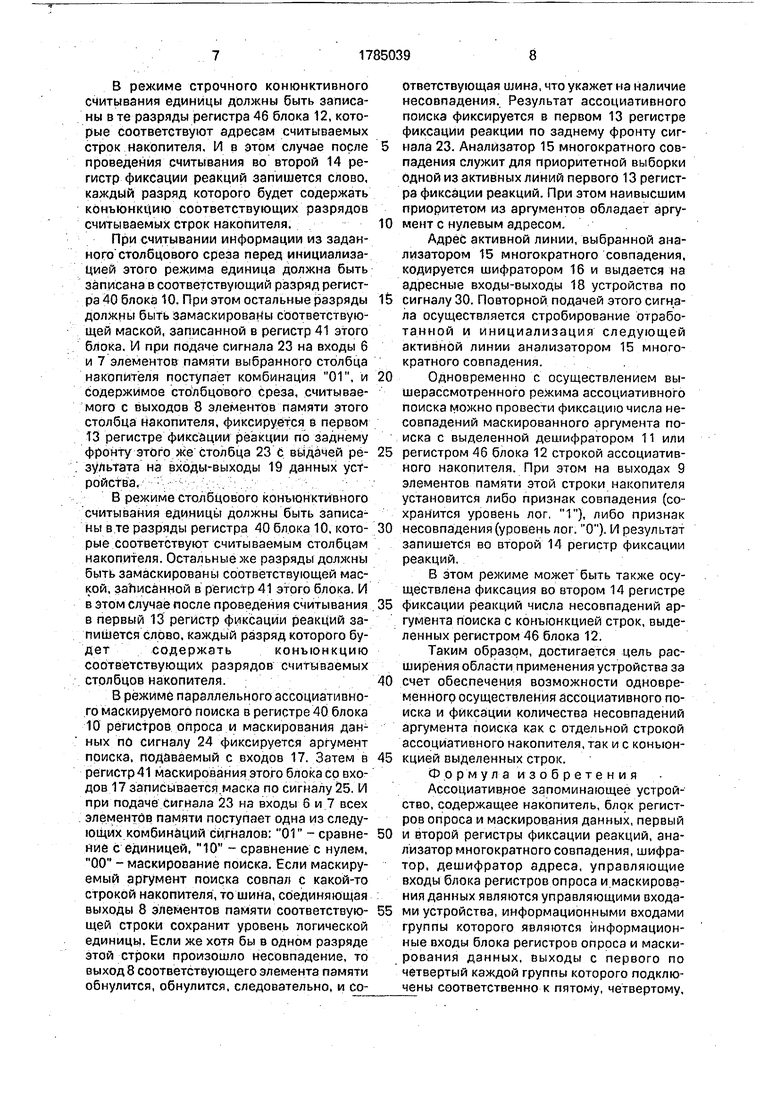

На фиг. 2 - схема элемента памяти. На фиг. 3 - схема блока регистров опроса и маскирования.

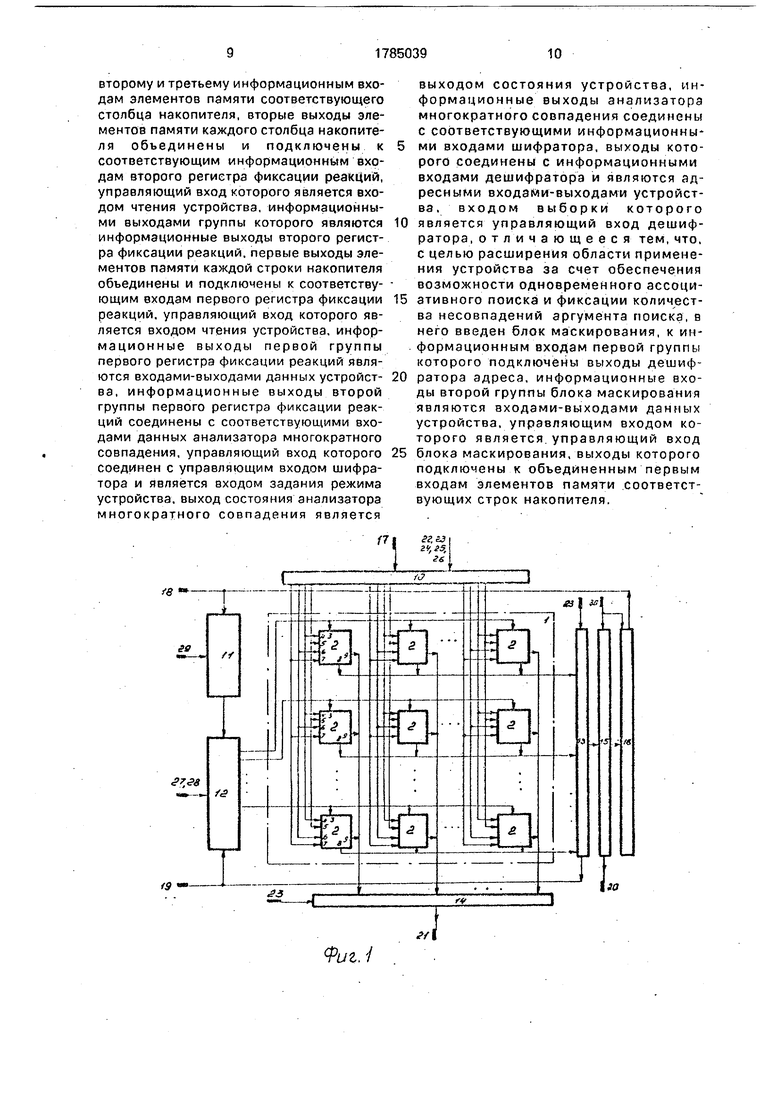

На фиг. 4 - дешифратор и блок маскиро0 вания.

Устройство (фиг. 1) содержит накопитель 1, в состав которого входят элементы памяти 2 со входами с первого 3 по пятый 7 и с первым 8 и вторым 9 выходами, блок 10

5 регистров опроса и маскирования данных, дешифратор 11 адреса, блок 12 маскирования, первый 13 и второй 14 регистры фикса- цми реакций, анализатор 15 многократного совпадения, шифратор 16.

0 Информационные входы 17 блока 10 регистров опроса и маскирования данных служат второй группой информационных входов устройства, а выходы с первого по четвертый каждой группы выходов подклю5 чены соответственно к соединенным между собой пятым 7, четвертым 6. вторым 4 и третьим 5 входам элементов памяти 2 соответствующего столбца накопителя.

Входы дешифратора 11 подключены к

0 соответствующим адресным входам-выходам 18 устройства, а выходы соединены с соответствующими входами первой группы входов блока 12 маскирования, ко входам второй группы входов которого подключены

5 соответствующие входы-выходы 19 данных устройства, а выходы подключены соответственно к соединенным между собой первым 3 входам элементов памяти 2 соответствующих строк накопителя 1.

0 Первые 8 выходы элементов 2 памяти соответствующих строк накопителя соединены между собой и подключены к соответствующим информационным входам первого 13 регистра фиксации реакций, пер5 вая группа информационных выходов которого подключена к соответствующим входам-выходам 19 данных устройства, а вторая группа информационных выходов соединена с соответствующими входами данных анализатора 15 многократного совпадения, выход 20 состояния которого служит выходом состояния устройства, указывающими на наличие некоторого числа совпадений в результате проведения пардл- лельного ассоциативного поиска в накопи- теле 1, а информационные выходы присоединены к соответствующим Информационным входам шифратора, выходы которого подключены к адресной шине 18 устройства, -..

Вторые 9 выходы элементов памяти 2 соответствующих столбцов накопителя соединены между собой и подключены к соответствующим информационным входам второго 14 регистра фиксации реакций, вы- ходы которого служат группой 21 информационных выходов устройства.«--

На устройство подаются следующие управляющие сигналы:

22- сигнал записи в накопитель; .

23- сигнал опроса и считывания из накопителя;- -

24- сигнал записи в регистр оп р оса блока 10; -

25- сигнал записи в регистр маскиро- вания блока 10;

26- сигнал сброса в О регистров опроса и маскирования блока 10;

27- сигнал записи в регистр блока 12;

28- сигнал сброса в О регистра блока 12;

29- сигнал выборки дешифратора 11 адреса;

30- сигнал стробирования отработанной и выборки следующей активной линии блоком 15, а также выдачи шифратором 16

на адресную шину 18 устройства адреса следующей активной линии.

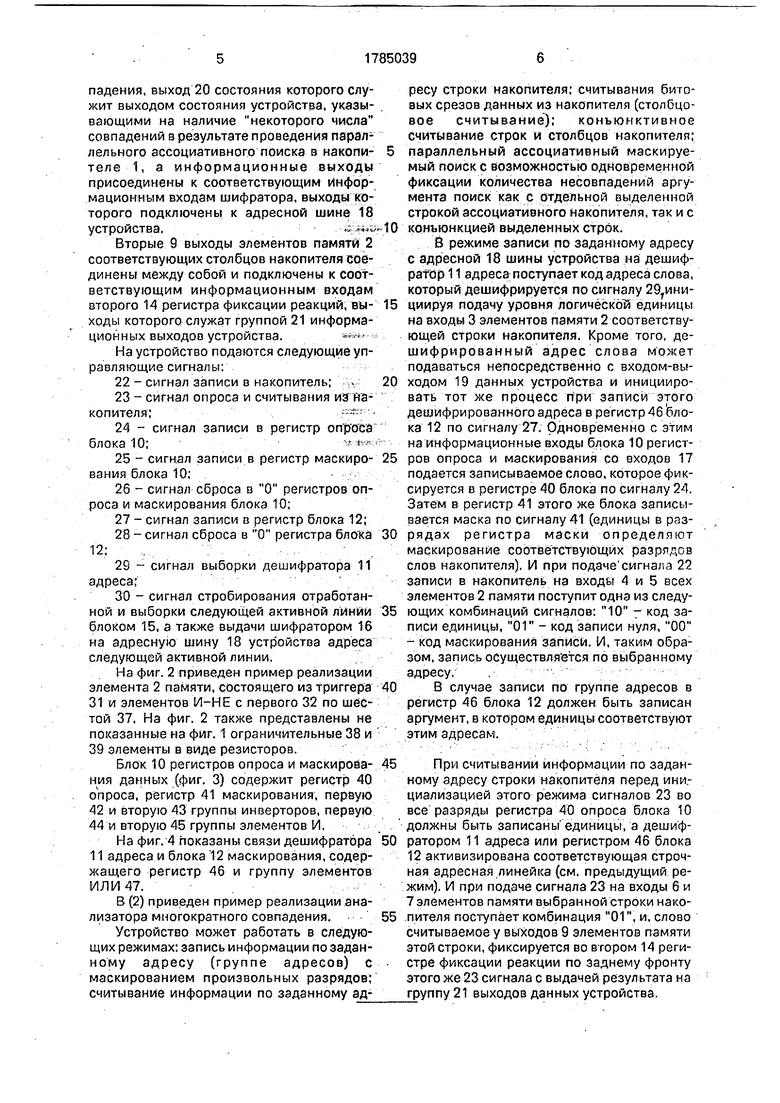

На фиг. 2 приведен пример реализации элемента 2 памяти, состоящего из триггера 31 и элементов И-НЕ с первого 32 по шестой 37. На фиг. 2 также представлены не показанные на фиг. 1 ограничительные 38 и 39 элементы в виде резисторов.

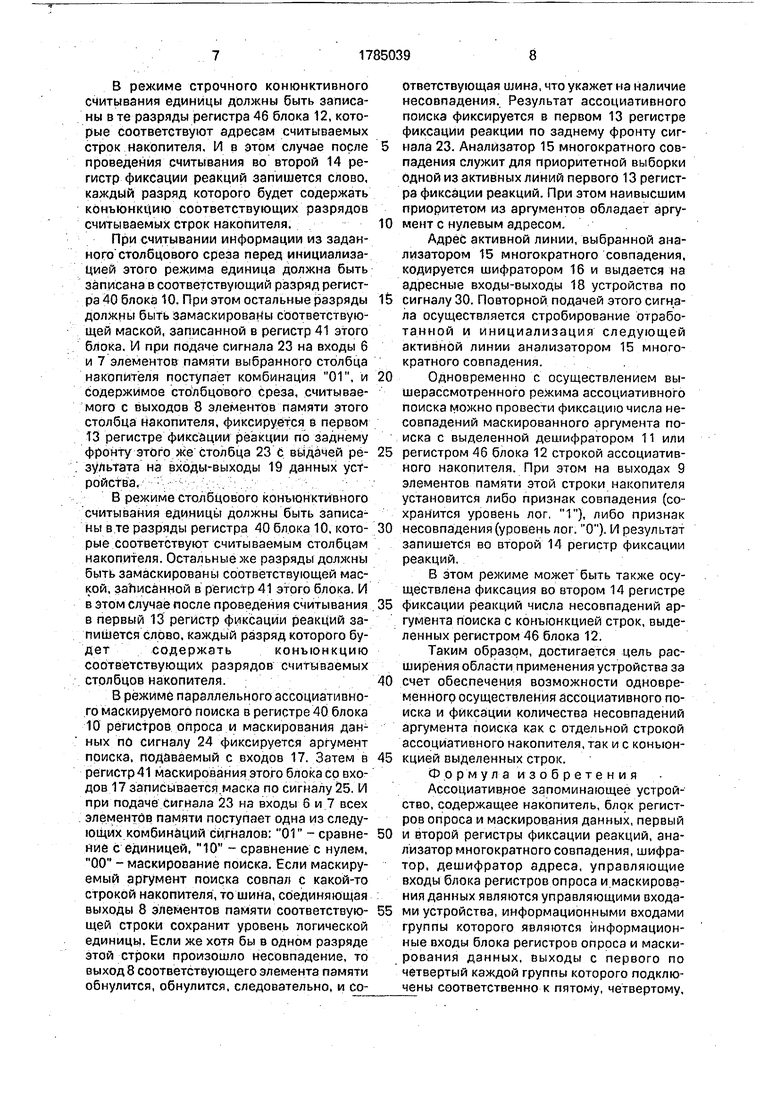

Блок 10 регистров опроса и маскирова- ния данных (фиг. 3) содержит регистр 40 опроса, регистр 41 маскирования, первую 42 и вторую 43 группы инверторов, первую 44 и вторую 45 группы элементов И,

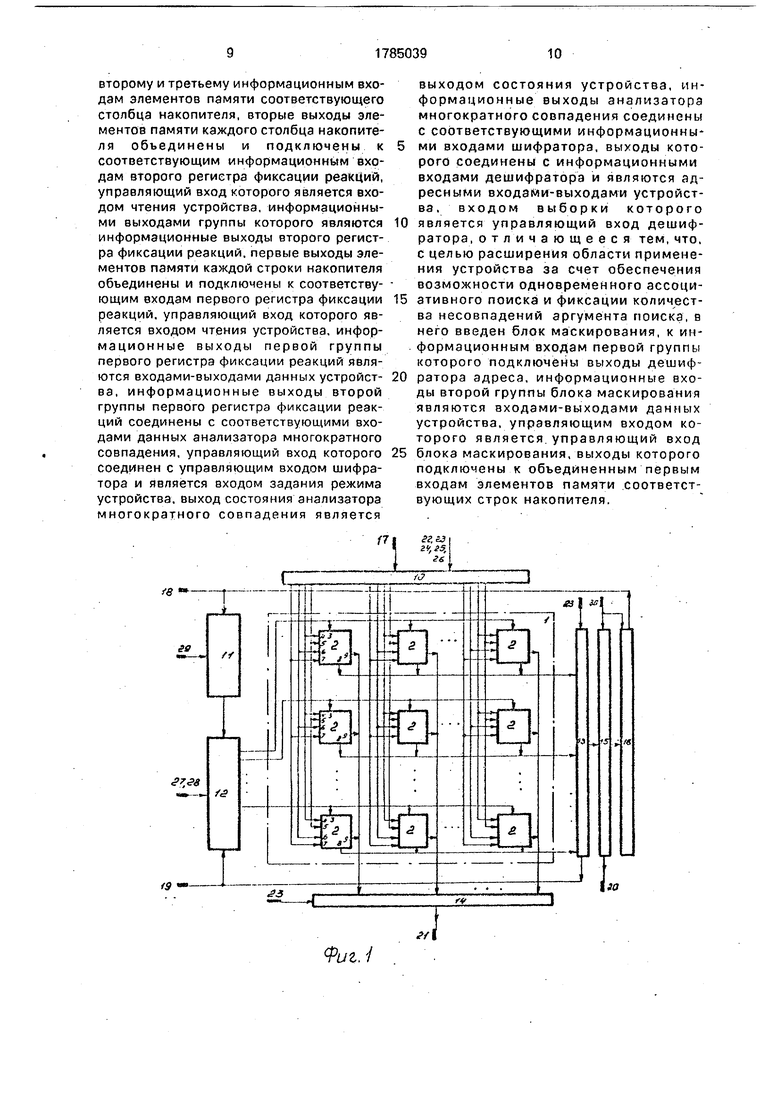

На фиг. 4 показаны связи дешифратора 11 адреса и блока 12 маскирования, содержащего регистр 46 и группу элементов ИЛ И 47.

В (2) приведен пример реализации анализатора многократного совпадения.

Устройство может работать в следующих режимах; запись информации по заданному адресу (группе адресов) с маскированием произвольных разрядов; считывание информации по заданному адресу строки накопителя; считывания битовых срезов данных из накопителя (столбцовое считывание); конъюнктивное считывание строк и столбцов накопителя; параллельный ассоциативный маскируемый поиск с возможностью одновременной фиксации количества несовпадений аргумента поиск как с отдельной выделенной строкой ассоциативного накопителя, так и с конъюнкцией выделенных строк.

В режиме записи по заданному адресу с адресной 18 шины устройства на дешифратор 11 адреса поступает код адреса слова, который дешифрируется по сигналу 29гини- циируя подачу уровня логической единицы на входы 3 элементов памяти 2 соответствующей строки накопителя. Кроме того, дешифрированный адрес слова может подаваться непосредственно с входом-выходом 19 данных устройства и инициировать тот же процесс при записи этого дешифрированного адреса в регистр 46 блока 12 по сигналу 27. Одновременно с этим на информационные входы блока 10 регистров опроса и маскирования со входов 17 подается записываемое слово, которое фиксируется в регистре 40 блока по сигналу 24. Затем в регистр 41 этого же блока записывается маска по сигналу 41 (единицы в разрядах регистра маски определяют маскирование соответствующих разрядов слов накопителя). И при подаче сигнала 22 записи в накопитель на входы 4 и 5 всех элементов 2 памяти поступит одна из следующих комбинаций сигналов: 10 - код записи единицы, О Г - код записи нуля, 00 - код маскирования записи. И, таким образом, запись осуществляется по выбранному адресу.

В случае записи по группе адресов в регистр 46 блока 12 должен быть записан аргумент, в котором единицы соответствуют этим адресам.

При считывании информации по заданному адресу Строки накопителя перед инициализацией этого режима сигналов 23 во все разряды регистра 40 опроса блока 10 должны быть записаны единицы, а дешифратором 11 адреса или регистром 46 блока 12 активизирована соответствующая строчная адресная линейка (см. предыдущий режим). И при подаче сигнала 23 на входы 6 и 7 элементов памяти выбранной строки накопителя поступает комбинация 01, и, слово считываемое у выходов 9 элементов памяти этой строки, фиксируется во втором 14 регистре фиксации реакции по заднему фронту этого же 23 сигнала с выдачей результата на группу 21 выходов данных устройства.

В режиме строчного конюнктивного считывания единицы должны быть записаны в те разряды регистра 46 блока 12, которые соответствуют адресам считываемых строк накопителя, И в этом случае после проведения считывания во второй 14 регистр фиксации реакций запишется слово, каждый разряд которого будет содержать конъюнкцию соответствующих разрядов считываемых строк накопителя.

При считывании информации из заданного столбцового среза перед инициализацией этого режима единица должна быть записана в соответствующий разряд регистра 40 блока 10. При этом остальные разряды должны быть замаскированы соответствующей маской, записанной в регистр 41 этого блока. И при подйче сигнала 23 на входы 6 и 7 элементов памяти выбранного столбца накопителя поступает комбинация 01, и содержимое столбцового среза, считываемого с выходов 8 элементов памяти этого столбца накопителя, фиксируется в первом 13 регистре фиксаций реакции по заднему фронту этого же столбца 23 С выдачей результата на входы-выходы 19 данных устройства.

В режиме столбцового конъюнктивного считывания единицы должны быть записаны в те разряды регистра 40 блока 10. которые соответствуют считываемым столбцам накопителя. Остальные же разряды должны быть замаскированы соответствующей маской, записанной в регистр 41 этого блока. И в этом случае после проведения считывания в первый 13 регистр фиксации реакций запишется слово, каждый разряд которого будетсодержатьконъюнкциюсоответствующих разрядов считываемых столбцов накопителя.

В режиме параллельного ассоциативного маскируемого поиска в регистре 40 блока 10 регистров опроса и маскирования данных по сигналу 24 фиксируется аргумент поиска, подаваемый с входов 17. Затем в регистр41 маскирования этого блока со входов 17 записывается маска по сигналу 25. И при подаче сигнала 23 на входы 6 и 7 всех элементов памяти поступает одна из следующих комбинаций сигналов: 01 - сравнение с единицей,10 - сравнение с нулем, 00 - маскирование поиска. Если маскируемый аргумент поиска совпал с какой-то строкой накопителя, то шина, соединяющая выходы 8 элементов памяти соответствующей строки сохранит уровень логической единицы. Если же хотя бы в одном разряде этой строки произошло несовпадение, то выход 8 соответствующего элемента памяти обнулится, обнулится. следовательно, и соответствующая шина, что укажет на наличие несовпадения. Результат ассоциативного поиска фиксируется в первом 13 регистре фиксации реакции по заднему фронту сигнала 23. Анализатор 15 многократного совпадения служит для приоритетной выборки одной из активных линий первого 13 регистра фиксации реакций. При этом наивысшим приоритетом из аргументов обладает аргу0 мент с нулевым адресом.

Адрес активной линии, выбранной анализатором 15 многократного совпадения, кодируется шифратором 16 и выдается на адресные входы-выходы 18 устройства по

6 сигналу 30. Повторной подачей этого сигнала осуществляется стробирование отработанной и инициализация следующей активной линии анализатором 15 многократного совпадения.

0 Одновременно с осуществлением вышерассмотренного режима ассоциативного поиска можно провести фиксацию числа несовпадений маскированного аргумента поиска с выделенной дешифратором 11 или

5 регистром 46 блока 12 строкой ассоциативного накопителя. При этом на выходах 9 элементов памяти этой строки накопителя установится либо признак совпадения (сохранится уровень лог. 1), либо признак

0 несовпадения (уровень лог. О). И результат запишется во второй 14 регистр фиксации реакций.

В этом режиме может быть также осуществлена фиксация во втором 14 регистре

5 фиксации реакций числа несовпадений аргумента поиска с конъюнкцией строк, выделенных регистром 46 блока 12.

Таким образом, достигается цель расширения области применения устройства за

0 счет обеспечения возможности одновременного осуществления ассоциативного поиска и фиксации количества несовпадений аргумента поиска как с отдельной строкой ассоциативного накопителя, так и с коныон5 кцией выделенных строк.

Формула изобретения Ассоциативное запоминающее устройство, содержащее накопитель, блок регистров опроса и маскирования данных, первый

0 и второй регистры фиксации реакций, анализатор многократного совпадения, шифратор, дешифратор адреса, управляющие входы блока регистров опроса и маскирования данных являются управляющими входа5 ми устройства, информационными входами группы которого являются информационные входы блока регистров опроса и маскирования данных, выходы с первого по четвертый каждой группы которого подключены соответственно к пятому, четвертому.

второму и третьему информационным входам элементов памяти соответствующего столбца накопителя, вторые выходы элементов памяти каждого столбца накопителя объединены и подключены к соответствующим информационным входам второго регистра фиксации реакций, управляющий вход которого является входом чтения устройства, информационными выходами группы которого являются информационные выходы второго регистра фиксации реакций, первые выходы элементов памяти каждой строки накопителя объединены и подключены к соответству- ющим входам первого регистра фиксации реакций, управляющий вход которого является входом чтения устройства, информационные выходы первой группы первого регистра фиксации реакций являются входами-выходами данных устройст- ва, информационные выходы второй группы первого регистра фиксации реакций соединены с соответствующими входами данных анализатора многократного совпадения, управляющий вход которого соединен с управляющим входом шифратора и является входом задания режима устройства, выход состояния анализатора многократного совпадения является

выходом состояния устройства, информационные выходы анализатора многократного совпадения соединены с соответствующими информационными входами шифратора, выходы которого соединены с информационными входами дешифратора и являются адресными входами-выходами устройства, входом выборки которого является управляющий вход дешифратора, отличающееся тем, что, с целью расширения области применения устройства за счет обеспечений возможности одновременного ассоциативного поиска и фиксации количества несовпадений аргумента поиска, в него введен блок маскирования, к информационным входам первой группы которого подключены выходы дешифратора адреса, информационные входы второй группы блока маскирования являются входами-выходами данных устройства, управляющим входом которого является управляющий вход блока маскирования, выходы которого подключены к объединенным первым входам элементов памяти соответствующих строк накопителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное запоминающее устройство | 1990 |

|

SU1793475A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1718274A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1992 |

|

RU2025796C1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2045787C1 |

| Ассоциативное запоминающее устройство | 1991 |

|

SU1833917A1 |

| Ассоциативное запоминающее устройство | 1991 |

|

SU1837362A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1993 |

|

RU2037892C1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1824650A1 |

| АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА | 1993 |

|

RU2065207C1 |

| АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА | 1992 |

|

RU2025797C1 |

Уиг.1

2f

I

г

&

-л

-шь

е

-

с

95 Sff

/

Ш

Gfr

-tt&&

1

гг

, (#

, 9

(y;j

$ №/

# WM

J

Ј

6Е09Ш

2Э

//

/

яг.за

46

9(лг. 4

Авторы

Даты

1992-12-30—Публикация

1990-10-30—Подача