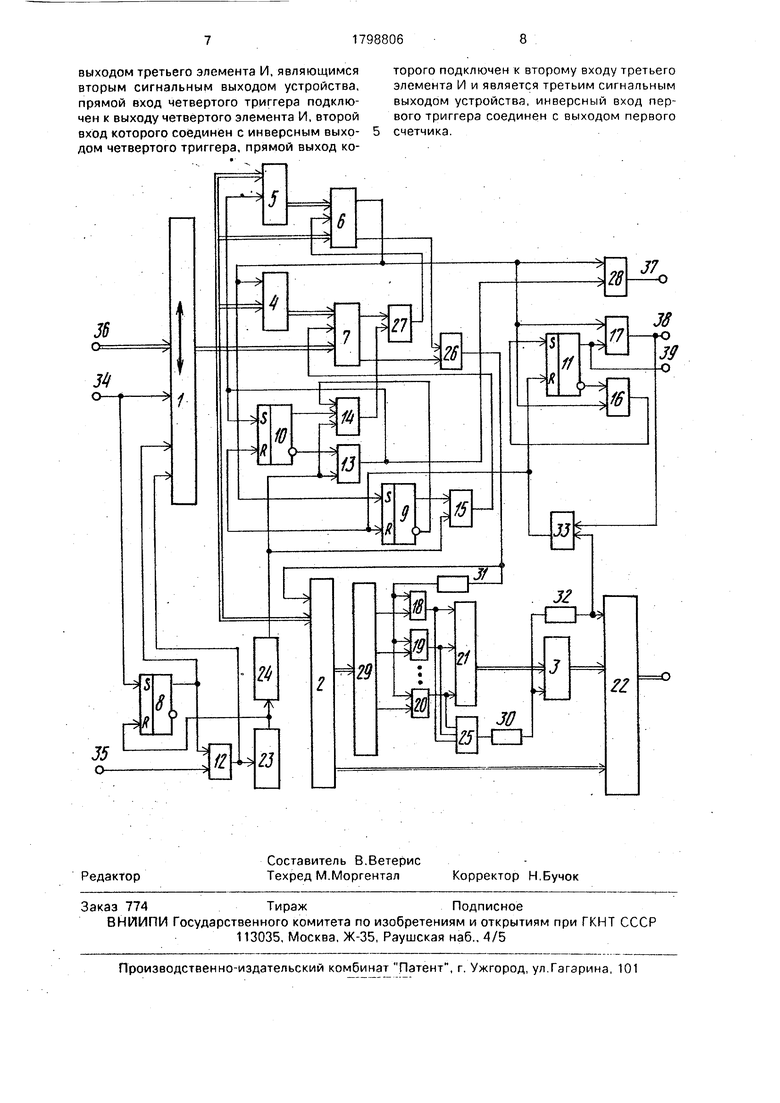

ется элемент 12 И, на другой вход которого с входа 35 поступают тактирующие импульсы сдвига. Эти импульсы проходят элементы 12 И и поступают как на тактирующий вход регистра 1 сдвига, так и на счетный вход счетчика 23, подсчитывающего восемь импульсов, сдвигающих код в регистре 1 в сторону старших разрядов.

Как только код в регистре 1 будет сдвинут на восемь разрядов, на выходе переполнения счетчика 23 появляется импульс, который во-первых, сбрасывает триггер 8 в исходное состояние; переводя тем самым регистр 1 в режим приема кода, и во-вторых, поступает на счетный вход счетчика 24, фиксирующего число принятых в регистр 1 байтов. После этого на вход 36 поступает второй байт кодограммы, который заносится в регистре 1 очередным синхроимпульсом с входа 34. Процесс сдвига кода в регистре 1 повторяется описанным образом.

Этот процесс повторяется до тех пор, пока счетчик 24 не зафиксирует необходимое (заданное) число байтов в регистре 1. Как только это число будет зафиксировано, на выходе переполнения счетчика 24 появляется импульс, фиксирующий факт занесе- кия в регистр 1 полной кодограммы сообщения.

Учитывая, что при передаче сообщения по каналу связи возможны искажения отдельных разрядов что недопустимо при фиксации идентификации признаков объекта, то запись полученного кода должна осуществляться только после тщательной проверки его истинности. .

С этой целью импульс переполнения с выхода счетчика 24 проходит через элемент 13 И, открытый находящимся в исходном состоянии триггером 10, и поступает как на синхронизирующий вход регистра 5, переписывая в него код регистра 1, так и через элемент 28 ИЛИ на выход 27, сигнализируя о повторной передаче кодограммы на вход 36. Кроме того, импульс устанавливает триггер 10 в единичное состояние. С получением сигнала с выхода 37 на вход 36 начинает повторно побайтно передаваться та же кодограмма описанным образом.

Как только на выходе счетчика 24 появ- . ляется импульс, фиксирующий факт завершения кода в регистре 1, он пройдет через элемент 14 И, открытый по другим входам высокими потенциалами с инверсного выхода триггера 9 и прямого выхода триггера 10 и элемента 27 ИЛИ, на синхронизирующий вход компаратора б, на информационные входы которого подаются коды с выходов регистров 1 и 5.

Здесь возможны две ситуации. Если значение кодов регистров 1 и 5 совпали, то компаратор фиксирует это совпадение выдачей импульсов на выходе А, откуда этот

импульс, пройдя элемент ИЛИ 26, поступает на синхронизирующий вход регистра 2 и переправляет содержимое регистра 1 в регистр 2.

Код объекта расшифровывается дешифратором 29, который открывает один из элементов 18-20 И, на другой вход которого поступает импульс, задержанный элементов задержки 31 на время переходных процессов в регистре 2 и дешифраторе 29.

5 Допустим, таким элементом был элемент 18 И. .

Тогда импульс с выхода элемента 31 задержки проходит через элемент 18 на вход считывания фиксированной ячейки памяти

0 блока 21, так и на вход элемента 25 ИЛИ.

В фиксированной ячейке памяти блока 21 хранится адрес, по которому должна быть зарегистрирована кодограмма. Этот адрес поступает на информационный вход

5 регистра 3, куда и заносится синхроимпульсом с выхода элемента задержки 30.

После записи кода адреса в регистре 3 тот же импульс с выхода элемента 30 задержки, задержанный элементом 32 на время

0 занесения кода в регистре 3, поступает на вход записи блока 22 и записывает содержательную часть кодограммы по указанному адресу.

Кроме того, тот же импульс с выхода

5 элемента 32 задержки возвращает триггеры , 9-11 в исходное состояние, а импульс с выхода 40 сигнализирует о готовности к приему очередной кодограммы.

Вторая ситуация характеризуется тем,

0 цто коды в регистрах 1 и 5 из-за ошибок в передаче могут отличаться друг от друга. Тогда сигнал, фиксирующий факт нерэвен- : ства кодов, появляется на выходе компаратора 6. По этому сигналу, во-первых,

5 поступающему на синхровход регистра 4, код с регистра 1 записывается в регистр 4. Во-вторых, триггер 9 устанавливается в единичное состояние и открывает элемент 15 И. В-трётьих, проходя через открытый в

0 исходном состоянии триггера 11 элемент И 16, импульс устанавливает триггер 11 в единичное состояние и открывает тем самым элемент И 17.

И, в-четвертых, импульс с выхода В ком5 паратора 6 проходит через элемент 28 ИЛИ на выход 3.7 в качестве сигнала повторной передачи той же кодограммы.

После получения сигнала с выхода 37 процесс повторной передачи кодограммы осуществляется описанным образом.

Как только счетчик 24 зафиксирует факт повторной записи кодограммы в регистре 1, импульс переполнения его выхода проходит через элемент 15 И, открытый высоким потенциалом с прямого выхода триггера 9 на синхронизирующий вход компаратора 7, на информационные входы которого подаются коды с регистров 1 и 4,

Здесь также возможны две ситуации. Если коды совпали, то. факт их совпадения компаратора 7 фиксирует выдачей импульс по выходу А, откуда этот импульс через элемент 26 ИЛИ поступает на выход 40 и на синхровход регистра 2, переписывая кодограмму сообщения с регистра 2.

Затем описанным образом содержание кодограммы записывается в блок памяти 22V Если же коды не совпали, то компаратор 7 зафиксирует факт их несовпадения выдачей импульса на выход В, откуда последний че- рез элемент 27 ИЛИ поступает на синхровход компаратора 6.

Если компаратор 6 зафиксирует равенство кодов, то с его выхода А импульс через элемент 26 ИЛИ поступает на синхровход регистра 2, на выход 40 и на вход элемента 31 задержки.

Если компаратор 6 зафиксирует неравенство кодов, то это будет означать, что коды всех кодограмм различны и, следова- тельно, канал передачи данных неисправен. В этом случае импульс с выхода В компаратора 6 проходит на выход 38 через элемент 17 И в качестве сигнала Отказ канала, а также сбрасывает все триггеры .9-11 в ис- хрдное состояние.

Формула изобретения .

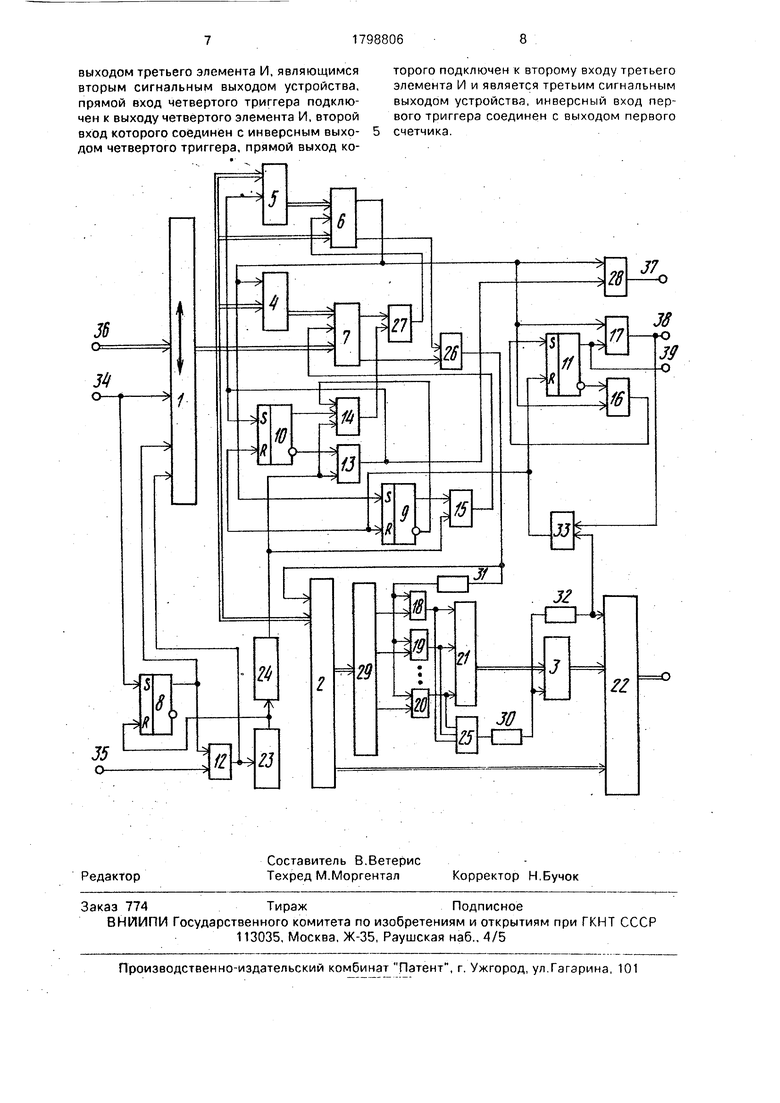

Устройство для распознавания образов, содержащее регистр сдвига, информа- ционный и синхронизирующий входы которого.являются соответственно информационным и синхронизирующим входами устройства, дешифратор, выходы которого соединены с первыми выходами группы элементов И, вторые входы которых под- ключены к выходу первого элемента задержки, а выходы - к входам первого блока памяти и входам первого элемента ИЛИ, выход которого через второй элемент задержки соединен с синхронизирующим вхо- дом первого регистра, информационный вход которого подключен к выходу первого блока памяти, первый триггер, прямой вход которого соединен с синхронизирующим входом устройства, а прямой выход - с уп- равляющим входом регистра сдвига и первым входом первого элемента И, второй вход которого подключен к тактирующему входу устройства, а выход - к тактирующему входу регистра сДвига, и счетному входу

первого счетчика, выход которого соединен со счетным входом второго счетчика, второй, третий, четвертый и пятый элементы ИЛИ, второй элемент И, отличающее с- я тем, что, с целью повышения надежности распознавания путем контроля достоверности полученных данных, в него введены два компаратора, второй, третий и четвертый регистры, второй, третий и четвертый триггеры, третий, четвертый, пятый и шестой элементы И, третий элемент задержки, второй блок памяти, первый информационный вход которого соединен с выходом первого регистра, второй информационный вход - с первым информационным выходом второго регистра, управляющий вход непосредственно - с первым входом второго элемента ИЛИ и через третий элемент задержки - с выходом второго элемента задержки, а выход является информационным выходом устройства, второй информационный выход второго регистра подключен к входу дешифратора, выход регистра сдвига соединен с информационными входами второго, третьего и четвертого регистров и с первыми информационными входами компараторов, вторые информационные входы которых подключены соответственно к выходам третьего и четвертого регистров, первые выходы компараторов подключены к первым входам третьего и четвертого элементов ИЛИ, а вторые выходы - к входам пятого элемента ИЛИ, выход которого соединен с управляющим входом второго регистра и входом первого элемента задержки, управляющий вход третьего регистра подключен к прямому входу второго триггера, выходу второго элемента И и второму входу третьего элемента ИЛИ, вы- . ход которого является первым сигнальным выходом устройства, управляющий вход четвертого регистра соединен с прямым входом третьего триггера, первым выходом первого компаратора и первыми входами третьего и четвертого элемента И, выход второго счетчика подключен к первым входам второго, пятого и шестого элементов И, вторые входы которых соединены соответственно с инверсным и прямым выходами второго триггера и прямым выходом третьего триггера, инверсный выход которого подключен к третьему входу пятого элемента И, выход которого соединен с вторым входом четвертого элемента ИЛИ, выход которого подклю чен к синхронизирующему входу первого компаратора, выход шестого элемента И соединен с синхронизирующим входом второго компаратора, инверсные входы второго, третьего и четвертого триггеров подключены к выходу второго элемента ИЛИ, второй вход которого соединен с

выходом третьего элемента И, являющимся вторым сигнальным выходом устройства, прямой вход четвертого триггера подключен к выходу четвертого элемента И, второй вход которого соединен с инверсным выхо- дом четвертого триггера, прямой выход ко

счетчика,

торого подключен к второму входу третьего элемента И и является третьим сигнальным выходом устройства, инверсный вход первого триггера соединен с выходом первого

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для записи информации в блок памяти | 1990 |

|

SU1730680A1 |

| СИСТЕМА МОДЕЛИРОВАНИЯ ВИРТУАЛЬНОГО СООБЩЕСТВА ПОЛЬЗОВАТЕЛЕЙ | 2014 |

|

RU2559725C1 |

| СИСТЕМА ВЕДЕНИЯ ЭЛЕКТРОННОЙ КАРТОТЕКИ КАДРОВОГО ДЕЛОПРОИЗВОДСТВА | 2006 |

|

RU2323471C1 |

| СИСТЕМА ИНФОРМАЦИОННОГО ОБЕСПЕЧЕНИЯ ЗАКОНОДАТЕЛЬНОГО ПРОЦЕССА ПРЕДСТАВИТЕЛЬНЫХ ОРГАНОВ ВЛАСТИ | 2014 |

|

RU2565525C1 |

| СИСТЕМА ПЕРСОНАЛИЗАЦИИ ПАСПОРТНО-ВИЗОВЫХ ДОКУМЕНТОВ НОВОГО ПОКОЛЕНИЯ | 2010 |

|

RU2432609C1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА ГОСУДАРСТВЕННОГО РЕГИСТРА НАСЕЛЕНИЯ | 2004 |

|

RU2276806C1 |

| ИНФОРМАЦИОННО-СПРАВОЧНАЯ СИСТЕМА ГОСУДАРСТВЕННОГО РЕГИСТРА НАСЕЛЕНИЯ | 2003 |

|

RU2246756C1 |

| СИСТЕМА ЗАЩИТЫ КОНКУРСНЫХ ПРЕДЛОЖЕНИЙ В ГОСУДАРСТВЕННЫХ ЗАКУПКАХ | 2004 |

|

RU2265883C1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА УЧЕТА И КОНТРОЛЯ ВЫДАЧИ ВОЕННОСЛУЖАЩИМ СТРЕЛКОВОГО ОРУЖИЯ | 2011 |

|

RU2450345C1 |

| Устройство для ввода информации | 1990 |

|

SU1709294A1 |

Авторы

Даты

1993-02-28—Публикация

1991-04-23—Подача