Изобретение относится к электротехнике и может быть использовано в схемах релейной защиты электрооборудования с целью контроля исправности токовых цепей дифференциальных защит, а также вывода этих защит из действия при возникновении неисправности в токовых цепях. Цель изобретения - повышение эффективности контроля.

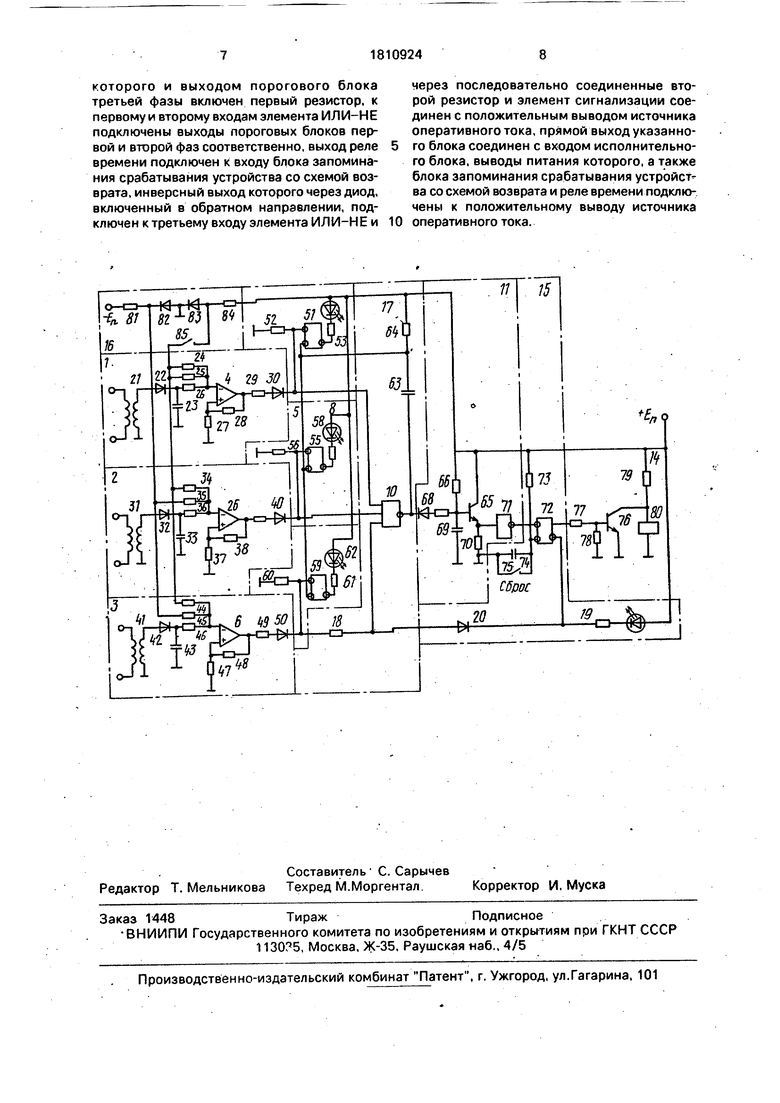

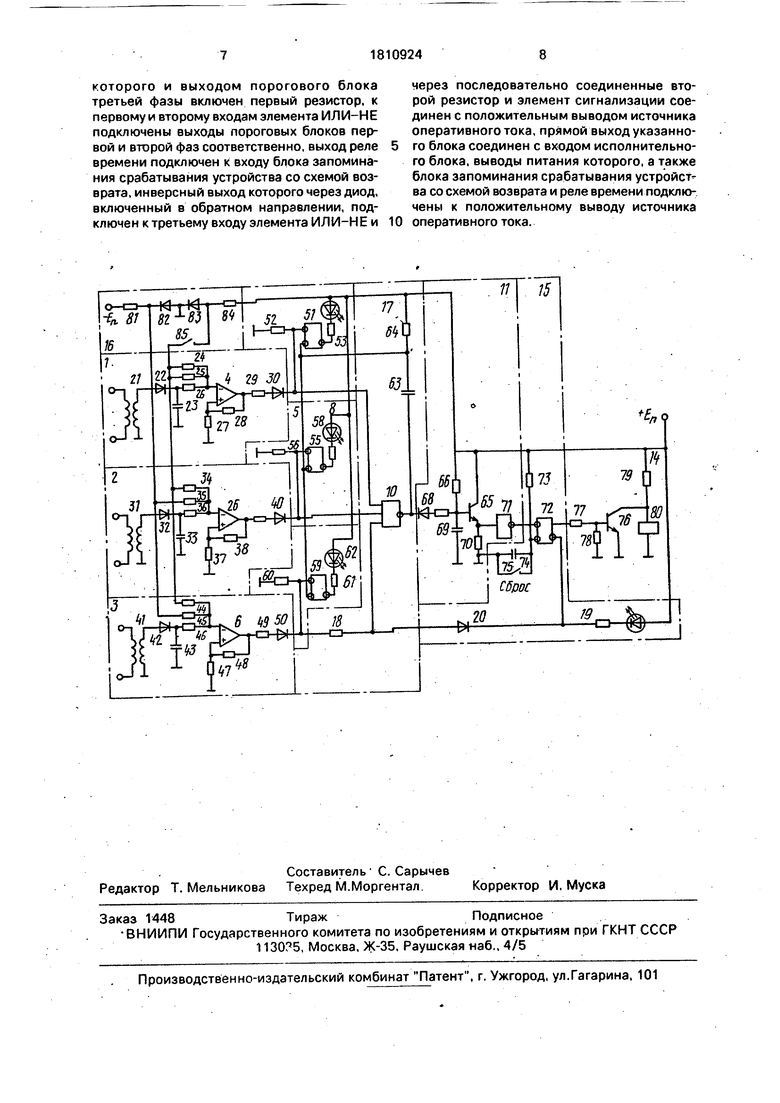

Принципиальная схема устройства приведена на чертеже.

Устройство содержит преобразователи сигнала по числу фаз 1,2,3, пороговые блоки 4,5,6 первой, второй и третьей фазы со схемами запоминания срабатывания на выходе 7,8,9 соответственно, элемент ИЛИ-НЕ 10, реле времени 11, элемент сигнализации 12, источник оперативного тока +Еп 13, исполнительный блок 14, блок 15 запоминания срабатывания устройства со схемой возврата, блок 16 тестового контроля, схема возврата 17, резисторы 18, 19, диод 20. Пороговый блок 4 состоит из согласующего трансформатора 21, диода 22 накопительного конденсатора 23, компаратора, выполненного на операционном усилителе с входами резигторами 24-26 и резисторами

положительной обратной связи 27, 28, ограничительным резистором 29 и диодом 30.

Пороговый блок 5 содержит согласующий трансформатор 31, диод 32, накопительный конденсатор 23. компаратор, выполненный на операционном усилителе с входами резисторами 34-36 и резисторами положительной обратной связи 37, 38, ограничительным резистором 39 и диодом 40.

Пороговый блок 6 состоит из согласующего трансформатора 41, диода 42, накопительного конденсатора 43 компаратора, выполненного на операционном усилителе с входными резисторами 44-46 и резисторами положительной обратной связи 47, 48 ограничительным резистором 49 и диодом 50.

Блок запоминания срабатывания порогового блока 4 первой фазы состоит из RS- триггера 51 с подключенным к S-входу резистором 57 и подключенной к инверсному выходу последовательной цепочкой, состоящей из резистора 53 и светодиода 54.

Блок запоминания срабатывания порогового блока 5 второй фазы состоит из RS- триггера 55 с подключенным к его S-входу резистором 56, а к его инверсному выходу

00

о ю

ю Ь.

последовательной цепочкой/состоящей из резистора 57 и светодиода 58.

Блок запоминания срабатывания порогового блока 6 третьей фазы состоит из RS- триггера 59 подключенным к его S-входу резистором 60, а к его инверсному выходу- последовательной цепочкой, состоящей из резистора 61 и светодиода 62.

Сьем возврата 17 состоит из конденсатора 63 и резистора 64.

Реле времени 11 состоит из транзистора 65 к базе которого подключены резистор 66, последовательно соединенные резистор 67 и диод 68 конденсатор 69, в эмиттерной цепи транзистора 65 включен резистор 70, к которому подключен вход инвертора 71.

Блок запоминания сработанного устройства со схемой возврата 15 состоит из триггера 72 к R-входу которого подключены резистор.73, конденсатор 74 и кнопка Сброс 75.

Исполнительный блок 14 состоит из транзистора 76 с подключенными к его базе резисторами 77, 78 коллектора-резистора 79 и обмотки реле 80.

Блок тестового контроля 16 состоит из последовательно соединенных резистора 81, диода 82, диода 83 и резистора 84, а также кнопки Контроль 85, подключенной к аноду диода 83,

В нормальном режиме работы на контролируемых обмотках выходных органов дифференциальных реле напряжения небаланса мало и, следовательно, напряжение на накопительных конденсаторах 23, 33 или 43-, определяемое амплитудным значением напряжения небаланса (за счет выбора времени заряда конденсатора гораздо меньшим, чем время его разряда), меньше установки пороговых блоков задаваемой с помощью диода 82 и резисторов 25, 35, 45 для пороговых блоков первой, второй и третьей фаз соответственно. При этом сигнал на выходе блоков 1, 2, 3 определяется напряжением положительного ограничения операционных усилителей 4, 5, 6.

Это приводит к формированию на S- входах триггеров 51,55,59 сигналов высокого уровня. Учитывая, что на R-входах этих триггеров после окончания заряда конденсаторов 63,74 присутствует высокий уровень потенциала, триггеры будут находиться в состоянии, которое получили при подаче оперативного питания, т.е. в состоянии низкого уровня по

тенциала по прямому выходу.

Поскольку на все три входа элемента ИЛИ-НЕ 1057 поступаютсигйалы высокого .уровня, на ее выходе будет присутствовать сигнал низкого уровня. Это вызывает в свою очередь открытие диода 68, что обеспечива

0

5

0

5

0

5 0 5

0

5

ет низкий уровень напряжения на конденсаторе 69, напряжение на входе инвертора 71, поступающее с выхода эмиттерного повторителя на транзисторе 65 будет также мало, что вызывает появление на выходе инвертора 71 высокого уровня потенциала. Поскольку на обоих входах триггера 72 присутствуют сигналы высокого уровня, на его выходах сигналы имеют значения, сформированные в момент подачи оперативного питания, т.е. низкий уровень потенциала на прямом выходе и высокий - на инверсном. Эти уровни сигналов обеспечивают закрытое состояние транзистора 76 и, соответственно нахождение реле 80 в сработанном состоянии, а также отсутствие световой сигнализации на светодиоде 12.

Выполнение схемы устройства, при котором его выходное реле в нормальном режиме находится в сработавшем состоянии, обеспечивает контроль за наличием оперативного тока контролируемой дифференциальной защиты, так как предлагаемое устройство получает питание от тех же шинок оперативного тока, что и контролируемая защита.

При возникновении неисправности в токовых цепях дифференциальной защиты возрастает небаланс на обмотке выходного органа соответствующего дифференциального реле этой защиты и срабатывает один из пороговых блоков (4-6). На выходе операционного усилителя сработавшего блока формируется сигнал отрицательной полярности, что приводит к появлению на п-входе соответствующего триггера (51, 55 или 59), а также на соответствующем входе элемента 10, низкого уровня потенциала, поступающего через один из резисторов - 52, 56 или 60 (в зависимости от того, на выходе какого из операционных усилителей 4, 6 или 6 появился сигнал отрицательной полярности). Появление указанных сигналов вызывает переброс соответствующего триггера и установку на его инверсном выходе напряжения низкого уровня и появления световой сигнализации (работает один из светодио- дов 54, 58 или 62), а также появление на выходе элемента ИЛИ-НЕ 10 высокого уровня потенциала. Последнее вызывает разряд конденсатора 63, а также закрытие диода 68 и начало заряда конденсатора 69 от источника питания положительной полярности с постоянной времени, определяемой значениями резистора 66 и конденсатора 69. Напряжение на резисторе 72 будет повторять напряжение на конденсаторе 69 (эмиттерный повторитель на транзисторе 65 введен для исключения влияния инвертора 71 на процесс заряда конденсатора 69). Инвертор 71, выполненный на интегральной микросхеме К511ЛА1, имеет порог переключения около 7,2 В, При достижении значения напряжения на резисторе 70 этого уровня происходит переключение инвертора 71, на выходе которого формируется сигнал низкого уробня, что приводит к срабатыванию триггера 72 и появлению на его прямом выходе высокого, а на инверсном - низкого уровней потенциала. Сигнал с инверсного выхода через диод 20 поступает на третий вход элемента ИЛИ НЕ 10. обеспечивая нахождение этой схемы в состоянии логической единицы по выходу, независимо от состояния пороговых блоков, Это обеспечивает разряженное состояние конденсатора 63 и подготовку возврата триггеров 54, 55, 59 в исходное состояние при нажатии кнопки сброс 75. Одновременно светодиод 12 обеспечивает световую сигнализацию о срабатывании устройства, которая может быть снята также только с помощью кнопки Сброс 75. Сигнал высокого уровня, поступающий с прямого выхода триггера 72 через резистор 77 на базу транзистора 76, вызывает открытие последнего, чем достигается шунтирование обмотки реле 80 и его срабатывание (сработанным состоянием реле в данной схеме считается состояние при обесточенной катушке). Реле, срабатывая, выполняет необходимые переключения во внешних цепях и остается в этом положении, независимо от состояния пороговых органов, до выполнения возврата схемы в исходное состояние с помощью кнопки Сброс 75. Указанное выполнение позволяет осуществлять вывод дифференциальной защиты объекта с одновременным вводом резервной защиты (например, неселективной отсечки), что позволяет сохранить трансформатор в работе и в то же время обеспечить его надежную (с учетом наличия газовой защиты) защиту.

При нажатии кнопки 75 (Сброс) на R- вход триггера 72 подается сигнал низкого уровня, что приводит к перебросу триггера 72 и появлению на его прямом выходе сигнала низкого уровня, а на инверсном выходе - сигнала высокого уровня потенциала. В результате высокого уровня потенциала на инверсном выходе триггера 72 гаснет светодиод 12 и закрывается диод 20. Низкий уровень потенциала на прямом выходе триггера 72 приводит к закрытию транзистора 76 подаче питания на реле 80 и его возврат в исходное положение. Если пороговые блоки устройства 4-6 находятся в несработавшем состоянии, то появление на инверсном выходе триггера 72 сигнала логической единицы обеспечивает переключение элемента 10 в состояние логическиго нуля по выходу,что вызывает кратковременное (за счет заряда конденсатора 63) появление на R-входах триггеров 51. 55. 59 5 сигналов логического нуля и установку этих триггеров в исходное состояние.

Тестовый контроль проводится при нажатии кнопки Контроль 85. При этом на входы первого, второго, третьего пороговых 0 блоков через резисторы 24, 34, 44 соответственно подается сигнал заведомо больший установки, что приводит к их срабатыванию и формированию световой сигнализации с помощью светодиодов 54, 58, 62. Если кноп5 ку удерживать длительное время (более.ус- тавк.и реле времени), то произойдет срабатывание устройства в целом и формирование световой индикации этого состояния с помощью светодиода 12.

0

Формула изобретения Устройство для контроля цепей дифференциальной защиты, содержащее преобразователи сигнала по числу фаз, к выходу

5 первого из которых подключен пороговый блок первой фазы, элемент ИЛИ-НЕ, к выходу которого подключено реле времени, элемент сигнализации, источник оперативного тока и исполнительный блок, отличаю0 щ е е с я тем, что, с целью повышения эффективности контроля, дополнительно введены пороговые блоки второй и третьей фазы со схемами запоминания срабатывания на выходе, схема запоминания срабаты5 вания порогового блока первой фазы, блок запоминания срабатывания устройства со схемой возврата, блок тестового контроля, схема возврата, два резистора, диод, при этом к выходам второго и третьего преобра0 зователей сигнала подключены первые входы пороговых блоков второй и третьей фаз соответственно, к выходу порогового блока первой фазы подключена схема запоминания срабатывания этого блока, выходы схем

5 запоминания объединены и подключены к положительному выводу источника оперативного тока,.к одному из входов блока тестового контроля подключены вторые объединенные входы пороговых блоков фаз,

0 третьи входы которых объединены и подключены к выходу блока тестового контроля, включенного между отрицательным выводом источника оперативного тока и объеди- ненными. выходами схем запоминания

5 срабатывания пороговых блоков, вторые входы которых объединены и подключены к среднему выводу схемы возврата, которая включена между положительным выводом источника оперативного тока и выходом элемента ЙЛИ-НЕ, между третьим входом

которого и выходом порогового блока третьей фазы включен первый резистор, к первому и второму входам элемента ИЛИ-НЕ подключены выходы пороговых блоков первой и второй фаз соответственно, выход реле времени подключен к входу блока запоминания срабатывания устройства со схемой возврата, инверсный выход которого через диод, включенный в обратном направлении, подключен к третьему входу элемента ИЛИ-НЕ и

через последовательно соединенные второй резистор и элемент сигнализации соединен с положительным выводом источника оперативного тока, прямой выход указанного блока соединен с входом исполнительного блока, выводы питания которого, а также блока запоминания срабатывания устройства со схемой возврата и реле времени подключены к положительному выводу источника оперативного тока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для проверки исправности элементов релейной защиты | 1988 |

|

SU1597958A1 |

| РЕЛЕ ВРЕМЕНИ | 2002 |

|

RU2208259C1 |

| Устройство для проверки средств защиты трехфазной сети от перенапряжений | 1986 |

|

SU1411880A1 |

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОЙ СИГНАЛИЗАЦИИ | 2009 |

|

RU2406157C2 |

| Устройство для токовой защиты | 1975 |

|

SU667175A3 |

| УСТРОЙСТВО ИЗБИРАТЕЛЬНОГО КОНТРОЛЯ ЗАМЫКАНИЯ ФАЗЫ НА КОРПУС В МНОГОФАЗНЫХ СЕТЯХ С ИЗОЛИРОВАННОЙ НЕЙТРАЛЬЮ | 2014 |

|

RU2574866C1 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ОТ ЗАМЫКАНИЙ НА ЗЕМЛЮ В СЕТЯХ 3-10 кВ | 2005 |

|

RU2297703C1 |

| Устройство для шунтирования однофазного замыкания и контроля сопротивления замыкания после шунтирования | 1986 |

|

SU1410164A1 |

| Устройство для проверки токовых защит | 1989 |

|

SU1791869A1 |

| Устройство для сигнализации | 1988 |

|

SU1644193A1 |

Сущность изобретения: дополнительное введение пороговых блоков второй и третьей фазы со схемами запоминания на выходе, схемы запоминания срабатывания порогового блока первой фазы, блока пуска реле времени со схемой возврата, блока запоминания срабатывания устройства со схемой возврата, блока уставки, ключа тестового контроля, радиатора и диода позволяет повысить эффективность контроля. 1 ил.

| Устройство контроля цепей дифференциальной защиты УКДЗ | |||

| Прибор с двумя призмами | 1917 |

|

SU27A1 |

Авторы

Даты

1993-04-23—Публикация

1989-04-06—Подача