Url(t) - Vri COS( ЙЛ-1 t + #V1 ). Ur2(t) Vj-2 COS( t H- pr2 )

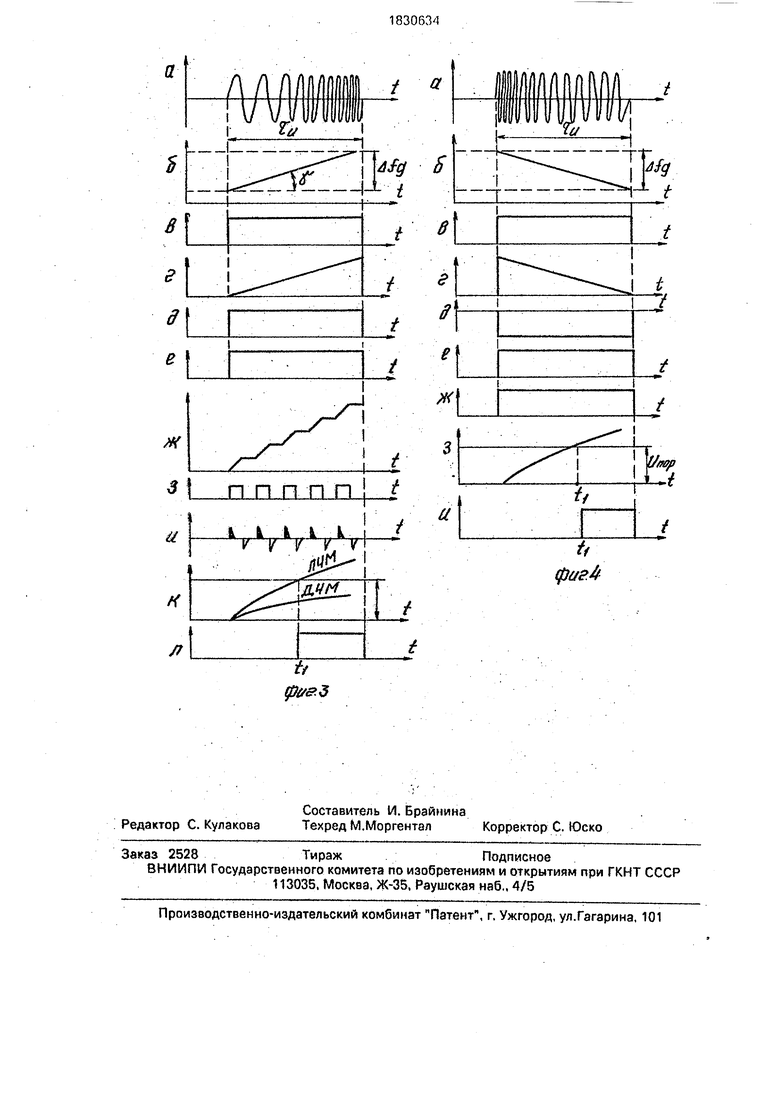

где Vri, Vr2, , , ЈҐ1 - - амплитуды, частоты и начальные фазы напряжений гетеродинов.Причем частоты ли и ftV2 гетеродинов 2 и 3 разнесены на удвоенное значение промежуточной частоты (Ог2 Wri 2oJhp и выбраны симметричными относительно частоты (DC основного канала

- UJfc fflt--UJri

Частота настройки UHI и полоса пропускания Дон усилителей 6,14,16 и 37 проме- жуточной частоты выбраны следующим образом:

Ун1 2с0пр,

Частота настройки оля и полоса пропускания Дод усилителей 13 и 15 промежуточ- ной частоты выбраны следующим образом:

0),

На второй вход смесителя 36 с выхода фазовращателя 35 на 90° подается напряжение.

Ur3(t) Vri -cos( + 90°).

На выходах смесителей 4,36 и 5 образуются следующие напряжения:.

Unpi (t) Vnp1 cos (Улр t +ayt2 -(

Unp2 (t) Vnpi COS (ftMp t + Jtyt2 + pnpl - 9 Unp3 (t) Vnp2 COS (atop t + Jiy t2 +Vnp

0 t $ги

где Vnpi Kl Vc Vfi;

vc vr2.;

KI- коэффициент передачи смесителей,

(t)np (Wi2-ftJfe o c-c«ri -промежуточная частота, .

pnpi - - Vi, np2 - pn

Причем частоты указанных напряжений имеют следующий вид:

woi с + 2 rty t - . +2 яу t ;

Ш02 №2 -ftJt- 2 л:у t - 2 яуt, где первый индекс обозначает канал, по которому принимается сигнал;

- второй индекс обозначает номер гетеродина, участвующего в преобразовании частоты принимаемого сигнала.

Преобразованные по частоте ЛЧМ сигналы Unpi(t). UnpaW и UnpaW попадают в полосу пропускания Дом усилителей б, 14, 37 и 16 промежуточной частоты. Так как в полосу пропускания ДйЈ усилителей 13 и 15 промежуточной частоты напряжения Unpi(t), UnpaW и UnpaW не попадают, то клю

0

0

5

0

)

5

0

п

5

5

чи 19 и 20 не открываются. Ключи 19 и 20 в исходном состоянии всегда закрыты, Напряжение Unpi(t) с выхода усилителя 6 промежуточной частоты поступает на первый вход сумматора 39, Напряжение Unp2(t) с выхода усилителя 37 промежуточной частоты поступает на вход фазовращателя 38 на 90°, на выходе которого образуется напряжение

Unp4 (t) Vnp1 CЈS (r/Jnp t +7fyt2 +pr,p1 -90°+90°) Vnpi ;cos (conpi ).

0 t Ги

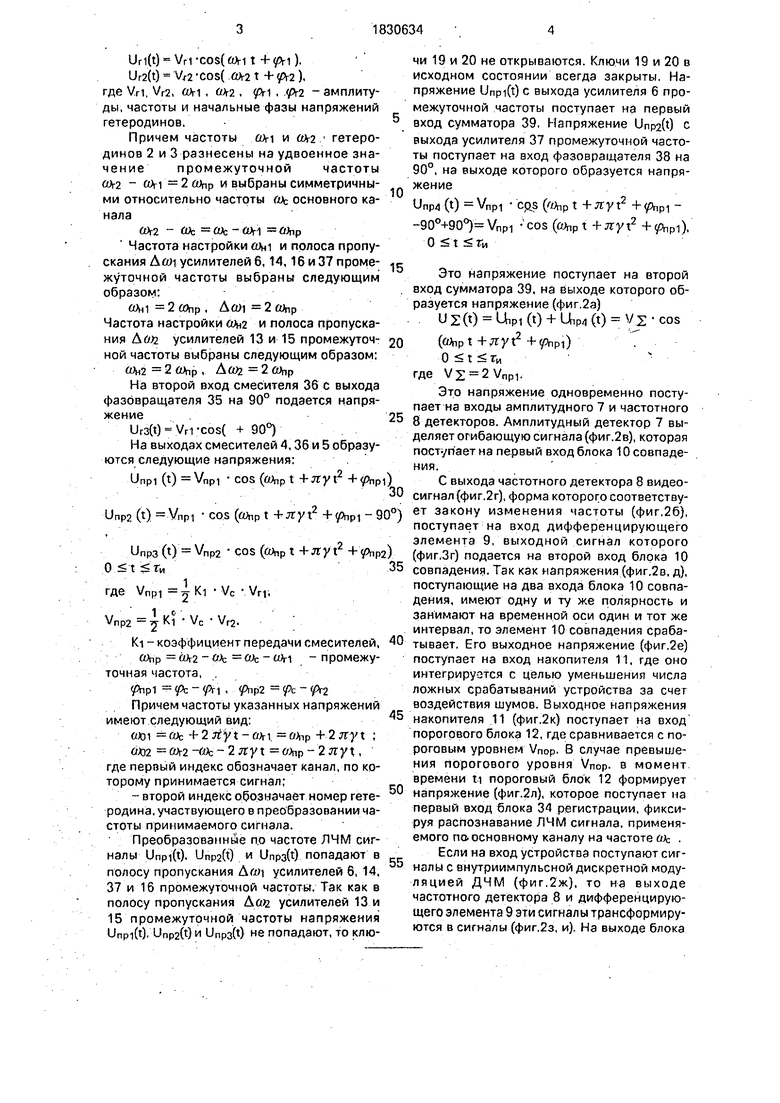

Это напряжение поступает на второй вход сумматора 39, на выходе которого образуется напряжение (фиг.2а)

U2(t) Uipi(t) + U,p4(t) Vi:-cos

(utopt ).

ч

где V2 2Vnpv

Это напряжение одновременно поступает на входы амплитудного 7 и частотного 8 детекторов. Амплитудный детектор 7 выделяет огибающую сигнала (фиг.2в), которая поступает на первый вход блока 10 совпадения.

С выхода частотного детектора 8 видеосигнал (фиг,2г), форма которого соответствует закону изменения частоты (фиг,26), поступает на вход дифференцирующего элемента 9, выходной сигнал которого (фиг.Зг) подается на второй вход блока 10 совпадения. Так как напряжения (фиг.2в, д), поступающие на два входа блока 10 совпадения, имеют одну и ту же полярность и занимают на временной оси один и тот же интервал, то элемент 10 совпадения срабатывает. Его выходное напряжение (фиг.2е) поступает на вход накопителя 11, где оно интегриру-этся с целью уменьшения числа ложных срабатываний устройства за счет воздействия шумов. Выходное напряжения накопителя 11 (фиг.2к) поступает на вход порогового блока 12, где сравнивается с пороговым уровнем Упор. В случае превышения порогового уровня Упор, в момент времени ti пороговый блок 12 формирует напряжение (фиг.2л), которое поступает на первый вход блока 34 регистрации, фиксируя распознавание ЛЧМ сигнала, применяемого по. основному каналу на частоте (ik .

Если на вход устройства поступают сигналы с внутриимпульсной дискретной моду- ляцией ДЧМ (фиг.2ж), то на выходе частотного детектора 8 и дифференцирующего элемента 9 эти сигналы трансформируются в сигналы (фиг.2з, и). На выходе блока

10 совпадения появляются лишь заштрихованные участки сигнала (фиг.2и). Вследствие малости .суммарной площади заштрихованных участков сигнал ДМЧ (фиг.2и) не превышает порогового уровня Vnop в пороговом блоке 12, т.е. устройство не срабатывает.

Описанная работа устройства соответствует случаю приема ЛЧМ сигнала по основному каналу на частоте аь

Если ЛЧМ сигнал принимается по первому зеркальному каналу на частоте Оди

Ua1 (t) V31 COS (Из1 t + Яу t2 + pal)

0 t ти

то в смесителях 4, 37 и 5 он преобразуется в напряжения:

Unps (0 Vnp3 COS ( t + яу t2 )

Unpe (t) Vnp3 cos («np t + лгу t2 + +

Unpy (t) - Vnp( COS (3 t + Jiy t2 + )

где Vnp3 -я Ki V3i Vn.

Vnn/l -

1

/np4 -j Kl V31 Vr2,

Wnp 0h . 3 Mr2 Мз1 $Pnp3 /Ы pf , Pnp4 Рэ1 рг2

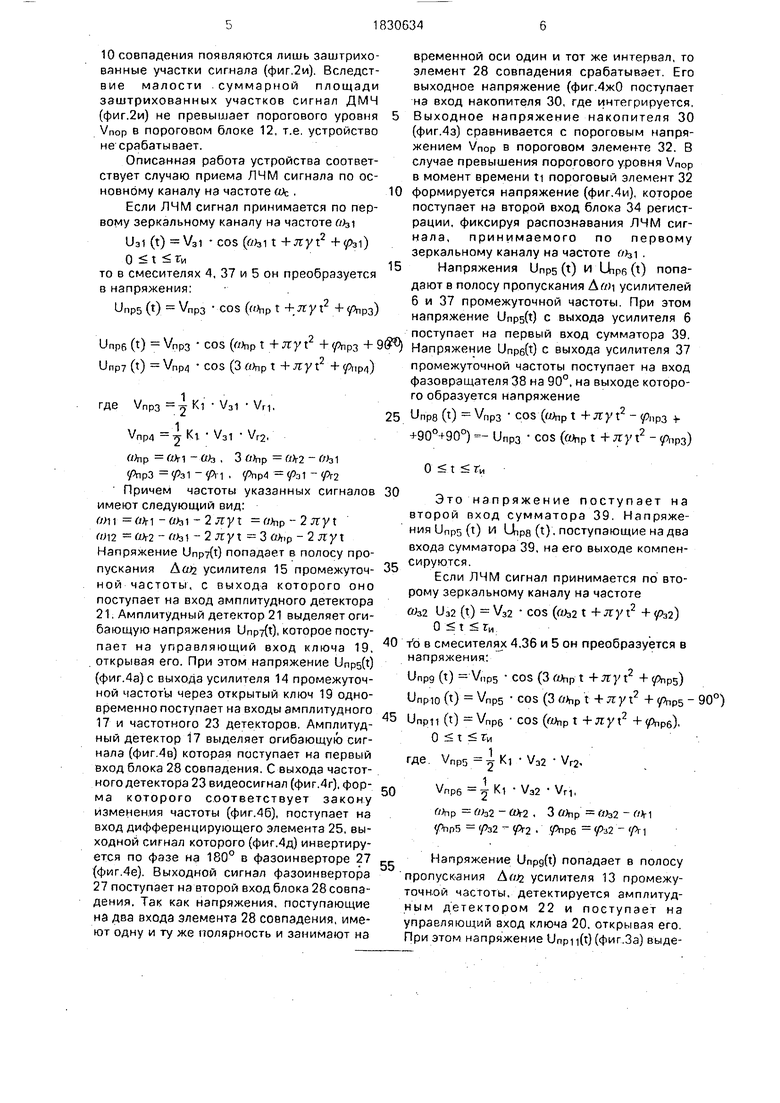

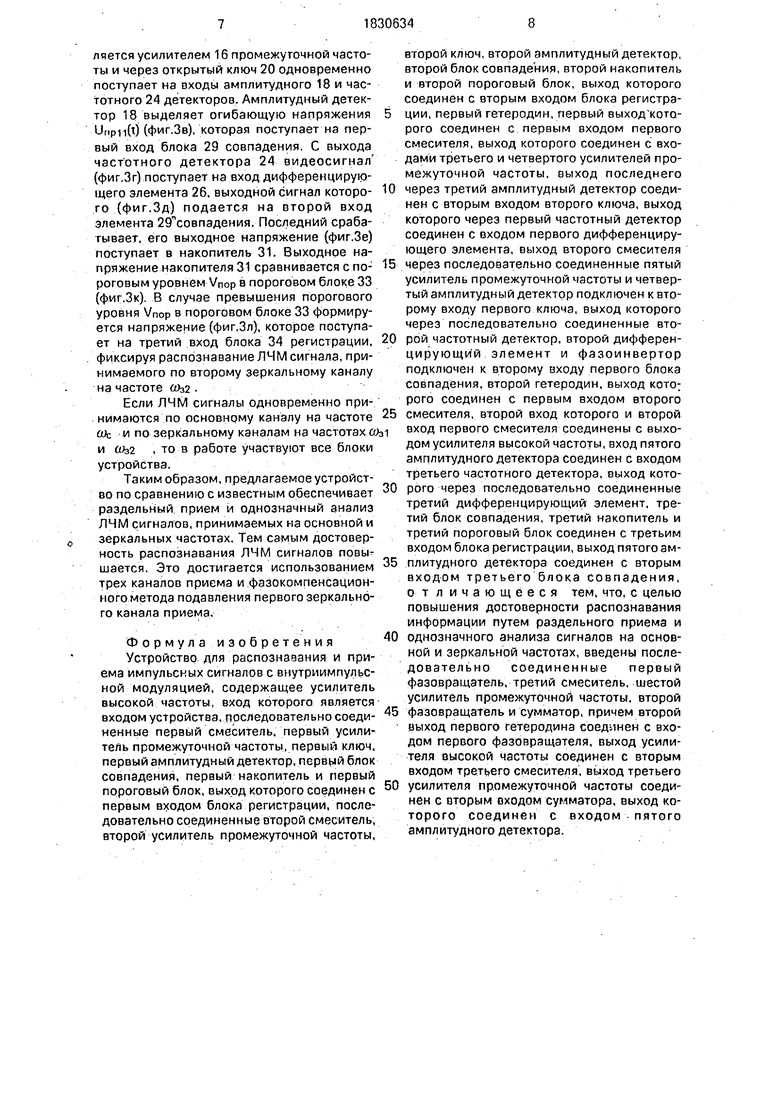

Причем частоты указанных сигналов имеют следующий вид: «и й 1-Wai-2яу: «пр-2яуг (on «r2 - мы - 2 яу t 3 Ohp - 2 яу t Напряжение Unpy(t) попадает в полосу пропускания Аад усилителя 15 промежуточ- ной частоты, с выхода которого оно поступает на вход амплитудного детектора 21. Амплитудный детектор 21 выделяет огибающую напряжения КпртО), которое поступает на управляющий вход ключа 19, открывая его. При этом напряжение Unps(t) (фиг.4а)с выхода усилителя 14 промежуточной частоты через открытый ключ 19 одно

временно поступает на входы амплитудного

17 и частотного 23 детекторов. Амплитудный детектор 17 выделяет огибающую сигнала (фиг.4в) которая поступает на первый вход блока 28 совпадения. С выхода частотного детектора 23 видеосигнал (фиг.4г), фор- ма которого соответствует закону изменения частоты (фиг.4б), поступает на вход дифференцирующего элемента 25, выходной сигнал которого (фиг.4д) инвертируется по фазе на 180° в фазоинверторе 27 (фиг.4е). Выходной сигнал фазоинвертора 27 поступает на второй вход блока 28 совпадения. Так как напряжения, поступающие на два входа элемента 28 совпадения, имеют одну и ту же полярность и занимают на

5

временной оси один и тот же интервал, то элемент 28 совпадения срабатывает. Его выходное напряжение (фиг.4жО поступает на вход накопителя 30, где интегрируется, Выходное напряжение накопителя 30 (фиг.4з) сравнивается с пороговым напряжением Vnop в пороговом элементе 32. В случае превышения порогового уровня Vn0p в момент времени ti пороговый элемент 32 формируется напряжение (фиг.4и), которое поступает на второй вход блока 34 регистрации, фиксируя распознавания ЛЧМ сигнала, принимаемого по первому зеркальному каналу на частоте г/ы .

Напряжения Unps (t) и Uipe (t) попадают в полосу пропускания усилителей 6 и 37 промежуточной частоты. При этом напряжение UnpsW с выхода усилителя 6 поступает на первый вход сумматора 39. Напряжение UnpeW с выхода усилителя 37 промежуточной частоты поступает на вход фазовращателя 38 на 90°, на выходе которого образуется напряжение

5 Unpe (t) Vnp3 cos («top t + яу t2 - рпрз Ґ

+90Q+90°) - UnP3 cos (oihp t + яу t2 - уърз) О t ги

Это напряжение поступает на второй вход сумматора 39. Напряжения Drips (t) и Цфд (t), поступающие на два входа сумматора 39, на его выходе компенсируются.

Если ЛЧМ сигнал принимается по второму зеркальному каналу на частоте

Уз2 U32 (t) V32 COS ((Оэ2 t +Яуг2 + а)

fb в смесителях 4,36 и 5 он преобразуется в напряжения:

Unpg (t) - Vnps COS (3 (Упр t +Яу t2 + пр5)

Unpio (t) Vnp5 cos (3 Mnp t + я у t2 + утпр5 - 90°)

Unpn (t) Vnpe COS (fUnp t +ЯУ t2 ),

0 t ги ,

где. Vnp5 -jKi V32 Vr2,

V32 Vri,

( dhl - (Jtk2 , 3 ftAip ЙЛз2 - f Vl np5 рз2 р2 У прб Уа2 - f

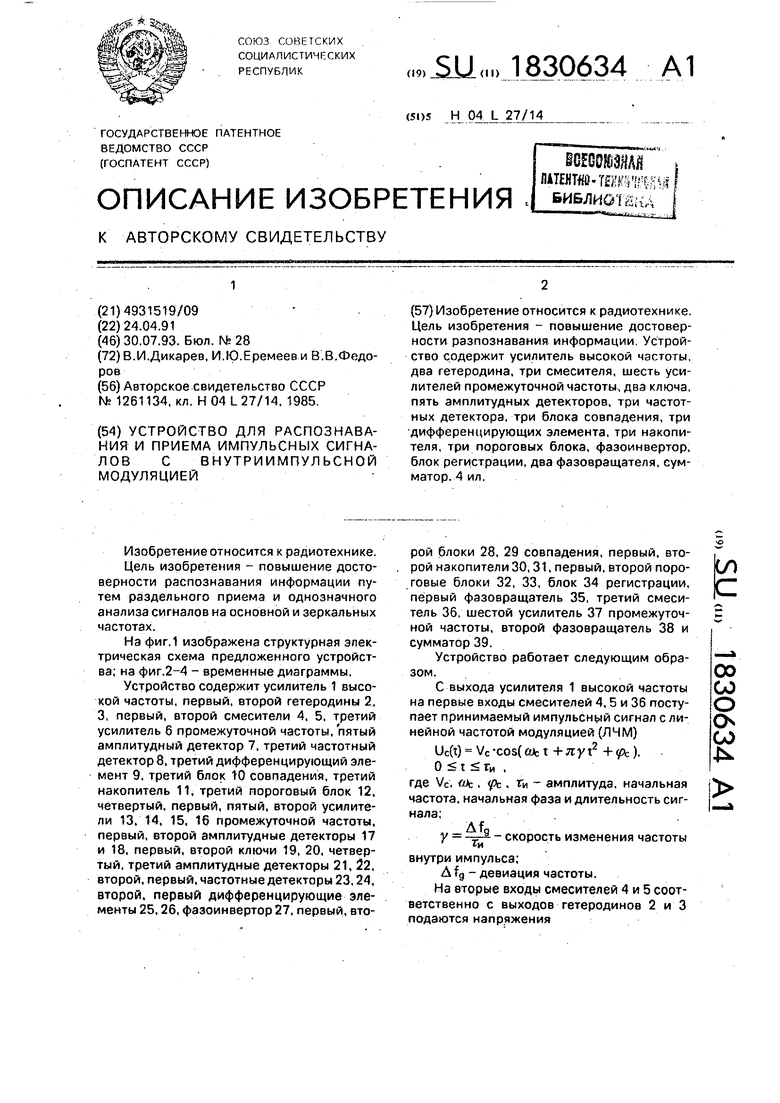

Напряжение Unpg{t) попадает в полосу пропускания усилителя 13 промежуточной частоты, детектируется амплитудным детектором 22 и поступает на управляющий вход ключа 20, открывая его. При этом напряжение Unpn(t) (фиг.За) выделяется усилителем 16 промежуточной частоты и через открытый ключ 20 одновременно поступает на входы амплитудного 18 и частотного 24 детекторов. Амплитудный детектор 18 выделяет огибающую напряжения UnpnW (фиг.Зв), которая поступает на первый вход блока 29 совпадения. С выхода частотного детектора 24 видеосигнал (фиг.Зг) поступает на вход дифференцирующего элемента 26, выходной сигнал которо- го (фиг.Зд) подается на второй вход элемента 29 совпадения. Последний срабатывает, его выходное напряжение (фиг.Зе) поступает в накопитель 31. Выходное напряжение накопителя 31 сравнивается ело- роговым уровнем Vnop в пороговом блоке 33 (фиг.Зк). В случае превышения порогового уровня Vnop в пороговом блоке 33 формируется напряжение (фиг.Зл), которое поступает на третий вход блока 34 регистрации, фиксируя распознавание ЛЧМ сигнала, принимаемого по второму зеркальному каналу на частоте %2 .

Если ЛЧМ сигналы одновременно при

нимаются по основному каналу на частоте

и по зеркальному каналам на частотах о и ОЪ2 , то в работе участвуют все блоки устройства.

Таким образом, предлагаемое устройство по сравнению с известным обеспечивает раздельный, прием и однозначный анализ ЛЧМ сигналов, принимаемых на основной и зеркальных частотах. Тем самым достоверность распознавания ЛЧМ сигналов повышается. Это достигается использованием трех каналов приема и.фазокомпенсацион- ного метода подавления первого зеркального канала приема.

Формула.изобретения

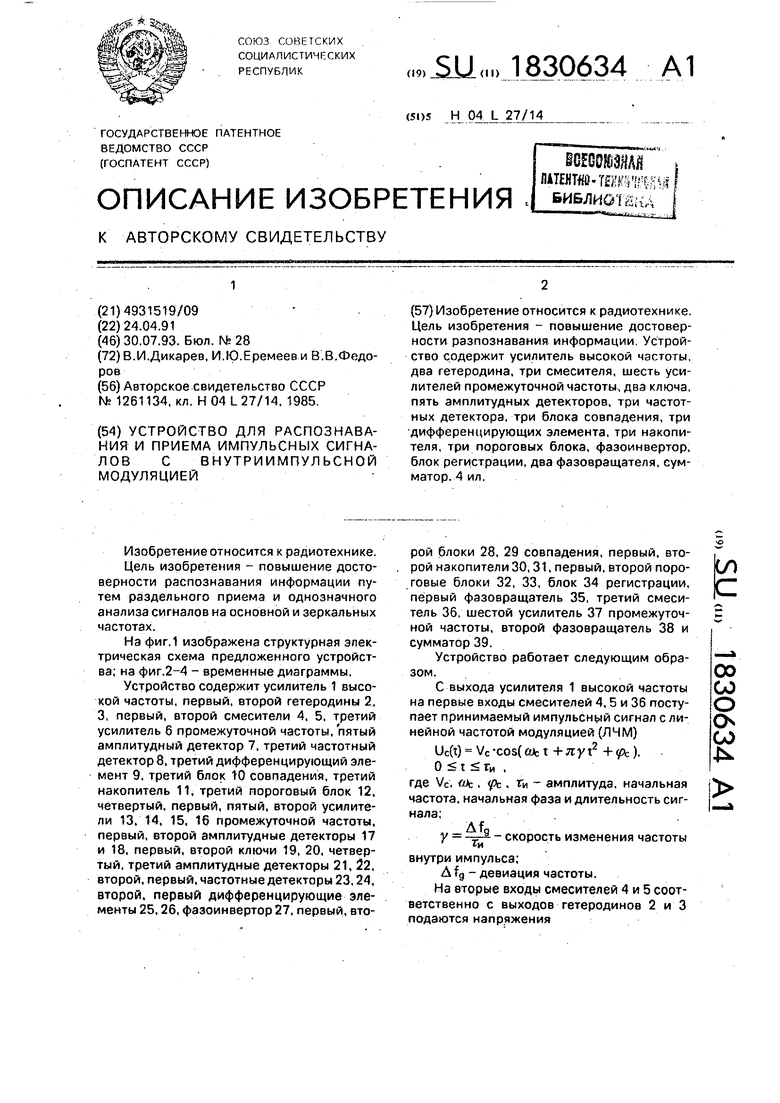

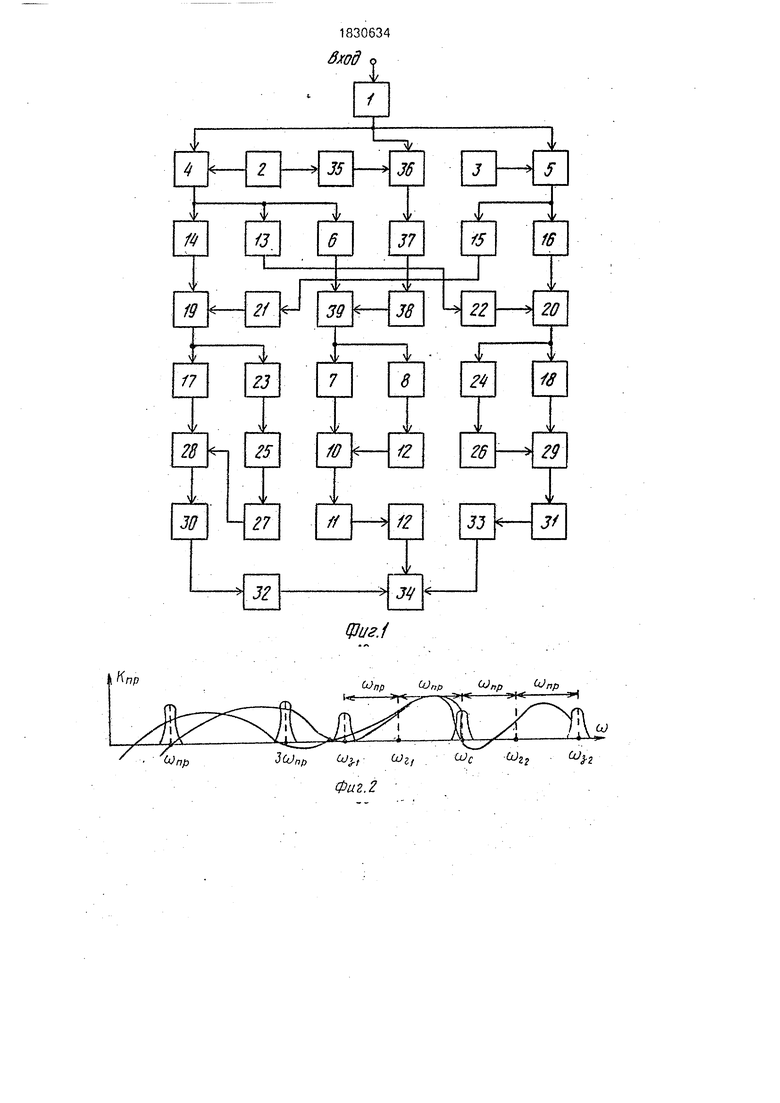

Устройство для распознавания и приема импульсных сигналов с внутриимпульс- ной модуляцией, содержащее усилитель высокой частоты, вход которого является входом устройства, последовательно соеди ненные первый смеситель, первый усилитель промежуточной частоты, первый ключ, первый амплитудный детектор, первый блок совпадения, первый накопитель и первый пороговый блок, выход которого соединен с первым входом блока регистрации, последовательно соединенные второй смеситель, второй усилитель промежуточной частоты,

„-

5Ю1520

25

30

5

°

45

второй ключ, второй амплитудный детектор, второй блок совпадения, второй накопитель и второй пороговый блок, выход которого соединен с вторым входом блока регистрации, первый гетеродин, первый выход которого соединен с первым входом первого смесителя, выход которого соединен с входами третьего и четвертого усилителей промежуточной частоты, выход последнего через третий амплитудный детектор соединен с вторым входом второго ключа, выход которого через первый частотный детектор соединен с входом первого дифференцирующего элемента, выход второго смесителя через последовательно соединенные пятый усилитель промежуточной частоты и четвертый амплитудный детектор подключен к второму входу первого ключа, выход которого через последовательно соединенные второй частотный детектор, второй дифференцирующий элемент и фазоинвертор подключен к второму еходу первого блока совпадения, второй гетеродин, выход кото; рого соединен с первым входом второго смесителя, второй вход которого и второй вход первого смесителя соединены с выходом усилителя высокой частоты, вход пятого амплитудного детектора соединен с входом третьего частотного детектора, выход которого через последовательно соединенные третий дифференцирующий элемент, третий блок совпадения, третий накопитель и третий пороговый блок соединен с третьим входом блока регистрации, выход пятого амплитудного детектора соединен с вторым входом третьего блокасовпадения, от л ичающееся тем, что, с целью повышения достоверности распознавания информации путем раздельного приема и однозначного анализа сигналов на основной и зеркальной частотах, введены последовательно соединенные первый фазовращатель, третий смеситель, шестой усилитель промежуточной частоты, второй фазовращатель и сумматор, причем второй выход первого гетеродина соединен с входом первого фазовращателя, выход усилителя высокой частоты соединен с вторым входом третьего смесителя, выход третьего усилителя промежуточной частоты соединен с вторым входом сумматора, выход которого соединен с входом пятого амплитудного детектора.

1830634

food

i

i

| название | год | авторы | номер документа |

|---|---|---|---|

| Индикаторное устройство | 1990 |

|

SU1793229A2 |

| Индикаторное устройство | 1990 |

|

SU1744472A2 |

| Индикаторное устройство | 1991 |

|

SU1800272A1 |

| Индикаторное устройство | 1991 |

|

SU1809307A1 |

| ИНДИКАТОРНОЕ УСТРОЙСТВО | 1991 |

|

RU2005992C1 |

| Устройство для распознавания и приема импульсных сигналов с внутриимпульсной модуляцией | 1985 |

|

SU1261134A1 |

| Анализатор спектра | 1990 |

|

SU1774281A2 |

| Акустооптический анализатор спектра | 1990 |

|

SU1767449A1 |

| Индикаторное устройство | 1990 |

|

SU1744473A1 |

| Устройство для приема широкополосных сигналов с линейной частотной модуляцией | 1990 |

|

SU1765902A2 |

Фиг.1

Jnf)

Oj tOJZlCJCй)г

Фиг, 2

ш

2

гтп п п п ../

1 ь 1 л k

V Y. Т

«яШЈ//

к

IITg SJh4

с

/

J i.

1

з

(ЙУс

/

Авторы

Даты

1993-07-30—Публикация

1991-04-24—Подача