Изобретение относится к электроизмерительной технике и может быть использован э при аппаратурном контроле качества эле прической энергии по выбросам и провал эм действующего значения напряжения,

Целью изобретения является расширение функциональных возможностей устройства за счет одновременного параллельного анализа как амплитуды, так и длительности выбросов и провалов напряжения.

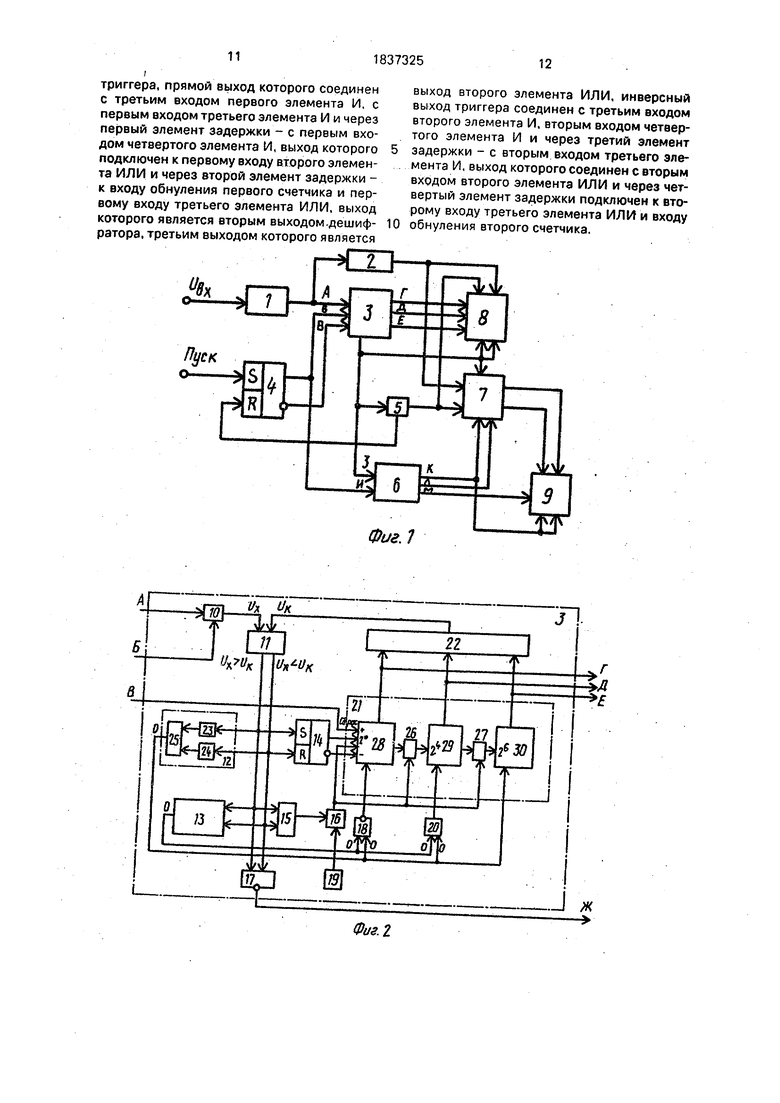

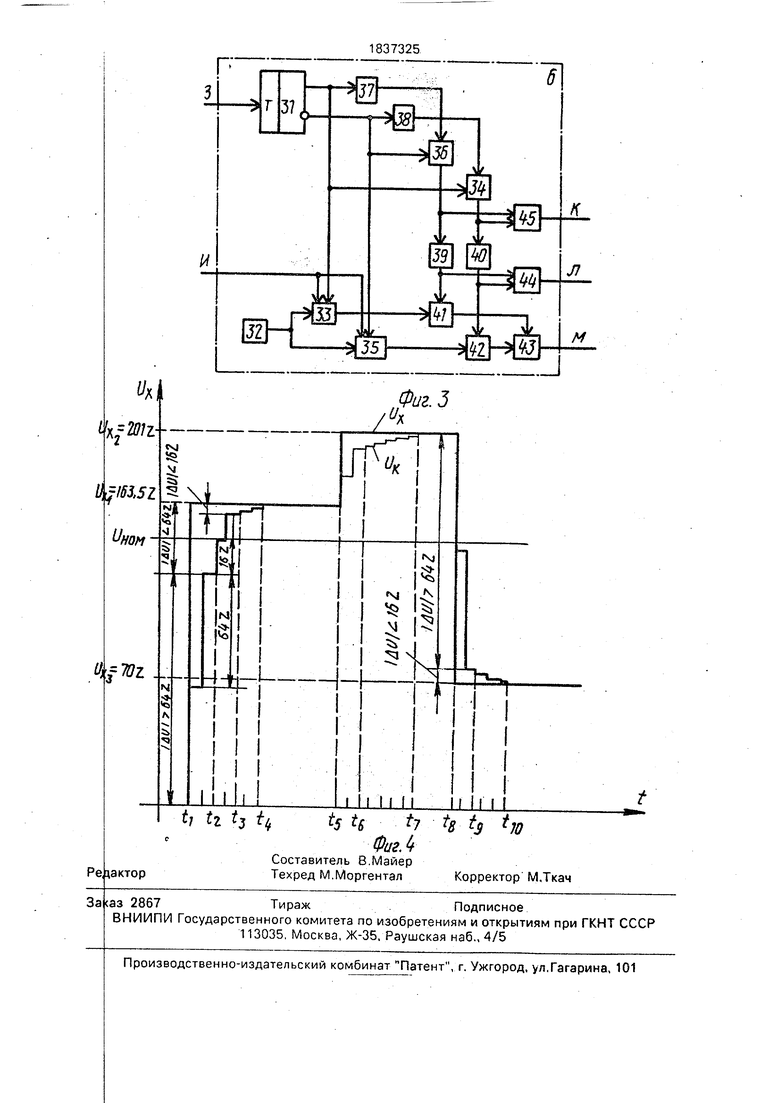

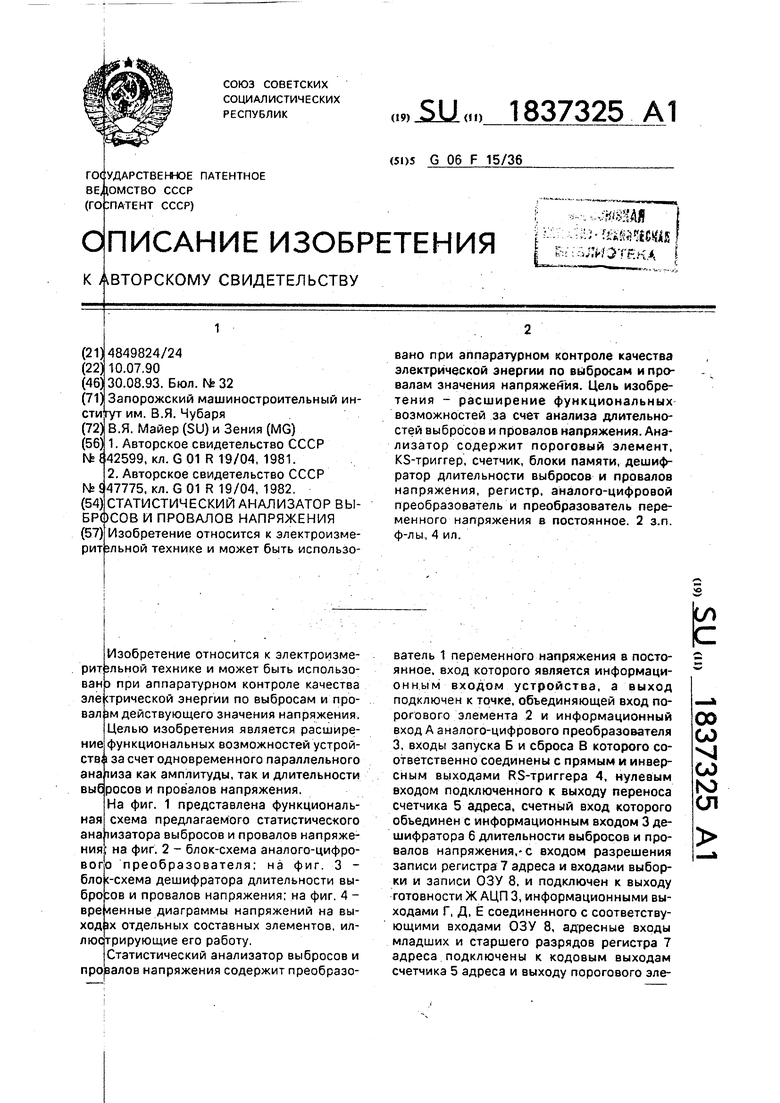

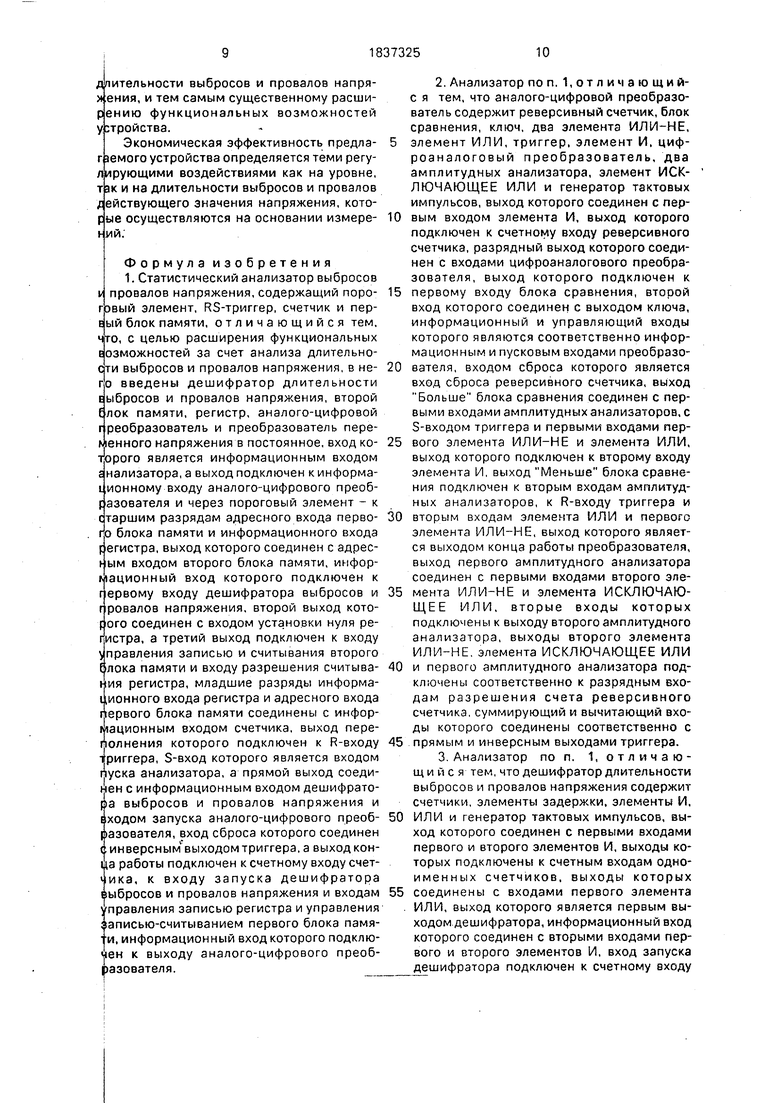

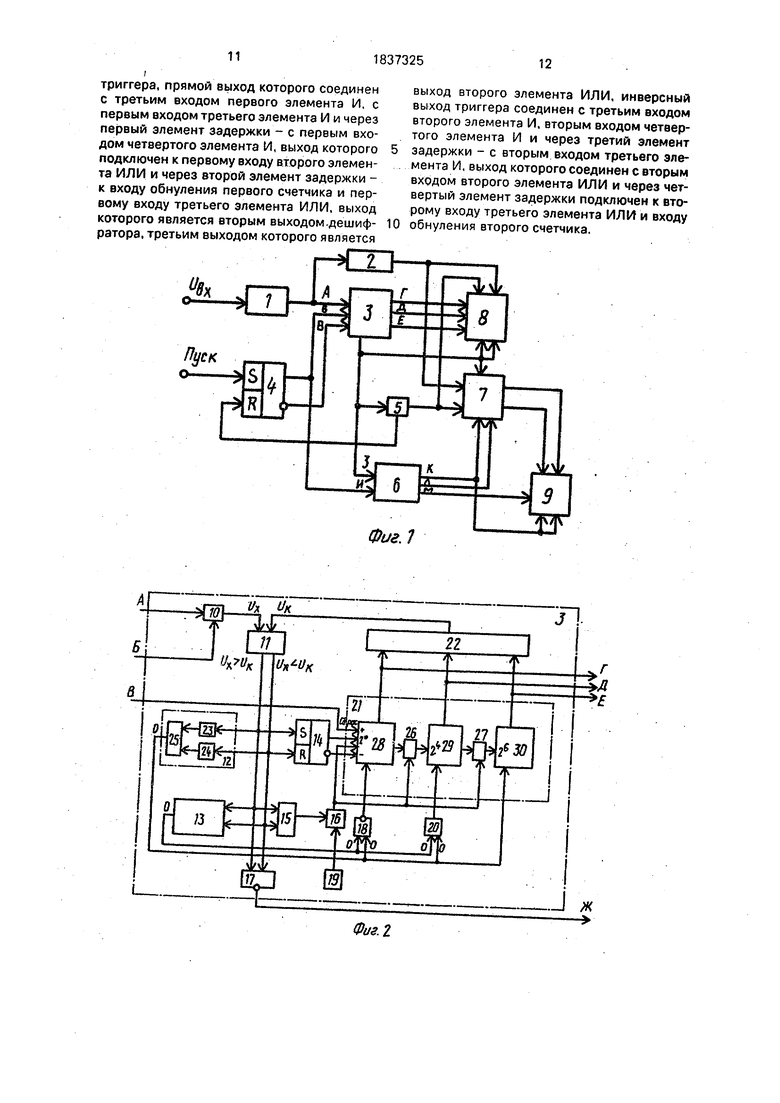

На фиг. 1 представлена функциональная схема предлагаемого статистического ана чизатора выбросов и провалов напряжения; на фиг. 2 - блок-схема аналого-цифрового преобразователя; на фиг. 3 - бло с-схема дешифратора длительности вы- бро:ов и провалов напряжения; на фиг. 4 - временные диаграммы напряжений на выходах отдельных составных элементов, иллюстрирующие его работу.

Статистический анализатор выбросов и провалов напряжения содержит преобразователь 1 переменного напряжения в постоянное, вход которого является информаци- онн.ым входом устройства, а выход подключен к точке, объединяющей вход порогового элемента 2 и информационный вход А аналого-цифрового преобразователя 3, входы запуска Б и сброса В которого соответственно соединены с прямым и инверсным выходами RS-триггера 4, нулевым входом подключенного к выходу переноса счетчика 5 адреса, счетный вход которого объединен с информационным входом 3 дешифратора 6 длительности выбросов и провалов напряжения, с входом разрешения записи регистра 7 адреса и входами выборки и записи ОЗУ 8, и подключен к выходу готовности Ж АЦП 3, информационными выходами Г, Д. Е соединенного с соответствующими входами ОЗУ 8, адресные входы младших и старшего разрядов регистра 7 адреса подключены к кодовым выходам счетчика 5 адреса и выходу порогового

Ё

00

со XI

00

ю ел

мента 2 соответственно. Вход разрешения считывания регистра 7 адреса объединен с входами выборки и записи ОЗУ 9 и подключен к стробирующему выходу К дешифратора 6 выбросов и провалов напряжения, управляющий выход Л которого соединен с входом установки нуля регистра 7 адреса, а информационный выход М - подключен к соответствующему входу ОЗУ 9, адресными входами соединенного с информационными выходами регистра 7 адреса.

Аналого-цифровой преобразователь 3 выполнен в виде комплексного блока, содержащего управляемый ключ 10, компаратор 11, амплитудные анализаторы 12 и 13, триггер 14 знака элемент ИЛИ 15, элемент А 16, элементы ИЛИ-НЕ 17 и 18, генератор 19 тактовых импульсов, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 20, реверсивный счетчик 21 и цифроаналоговый преобразователь (ЦАП) 22. При этом каждый из амплитудных анализаторов 12 и 13 содержит по два пороговых элемента 23 и 24, подключенным выходами к элементу ИЛИ 25, а реверсивный счетчик 21 состоит из трех последовательно-параллельно соединенных через элементы ИЛИ 26 и 27 групп младших 28, средних 29 и старших 30 разрядов, счетные выходы которых объединены и подключены через элемент И 16 ic выходу генератора 19 тактовых импульсов. Входы реверсивного счетчика

21,разрешающие операцию Сложение (+) и Вычитание (-), соединены соответственно с прямым и инверсным выходами триггера 14 знака, единичный и нулевой входы которого соответственно объединены с входами параллельно соединенных элемента ИЛИ 15, элемент ИЛИ-НЕ 17 и пороговых элементов 23 и 24 амплитудных анализаторов 12 и 13, подключены к выходам Больше () и Меньше () компаратора 11. Выход элемента ИЛИ 15 соединен со статическим входом элемента И 16. Выход элемента ИЛИ 25, являющийся выходом амплитудного анализатора 12, подключен к первым входам элемента ИЛИ-НЕ 18 и ИСКЛЮЧАЮЩЕГО ИЛИ 20, а также разрешающему счет входу группы старших разрядов 30. Выход амплитудного анализатора 13 соединен со вторыми входами элемента ИЛИ- НЕ 18 и ИСКЛЮЧАЮЩЕГО ИЛИ 20, выходы которых соответственно подключены к разрешающим счет входам групп младших 28 и средних 29 разрядов. Выходы групп младших 28, средних 29 и старших 30 разрядов, являющиеся кодовыми выходами реверсивного счетчика 21, соединены с входами ЦАП

22,выход которого подключен к опорному входу компаратора 11, сигнальным входом соединенного с выходом ключа 10. Информационный вход ключа 10 соединен с входом А АЦП 3, а управляющий вход- с входом Б АЦП 3, к выходу Ж которого подключен выход элемента ИЛИ-НЕ 17. Вход установ- ки нуля реверсивного счетчика 21 соединен с входом В АЦП, а кодовые выходы - с выходами Г, Д, Е АЦПЗ.

Дешифратор 6 длительности выбросов и провалов напряжения состоит из счетного

0 триггера 31, генератора 32 тактовых импульсов, элементов И 33-36, элементов задержки 37-40, счетчиков импульсов 41 и 42, и элементов ИЛИ 43-45. При этом прямой выход счетного триггера 31 подключен к точке,

5 объединяющей вход элемента 37 задержки, первый статический вход элемента И 33 и динамический вход элемента И 34, а инверсный выход - к точке, объединяющей вход элемента 38 задержки, первый статический

0 вход элемента И 35 и динамический вход элемента И 36. Выход генератора 32 тактовых импульсов соединен с динамическими входами элементов И 35 и 33, выходы которых соответственно подключены к счетным

5 входам счетчиков импульсов 41 и 42, выходами соединенных через элемент ИЛИ 43 с выходом М дешифратора. Входы установки нуля счетчиков 41 и 42 объединены с входами элемента ИЛИ 44 и подключены к выхо0 дам элементов задержки 39 и 40 соответственно, входы которых объединены с входами элемента ИЛИ 45 и подключены к выходам элементов И 36 и 34 соответственно, статистическими входами соединен5 ных с выходами элементов задержки 37 и 38 соответственно. Вход счетного триггера 31 соединен с входом 3 дешифратора 6, к входу И которого подключены объединенные вторые статические входы элементов И 33 и 35,

0 а выходы элементов ИЛИ 45 и 44 соединены соответственно с выходами К и Л дешифратора 6 длительности выбросов и провалов напряжения.

Устройство работает следующим обра5 зом.

Переменный выходной сигнал UBX преобразуется блоком 1 в постоянный, который изменяется скачком в соответствии с изменением огибающей напряжения сети. Это

0 позволяет наглядно получить характеристику исследуемого напряжения сети, которому присущи выбросы и провалы, что в значительной степени упрощает процесс его обработки и следовательно одновременный

5 параллельный анализ как амплитуды, так и длительности выбросов и провалов.

Таким образом, преобразуемое напряжение постоянного тока UxC выхода преобразователя 1 подается на пороговый элемент 2, порог срабатывания которого равен номинальному напряжению КноМ, и на аналого-цифровой преобразователь 3.

По сигналу Пуск триггер 4 устанавливается в единичное состояние. При этом, в

ПР

10

образователе 3 аналог-код (фиг. 2), ключ замыкается и измеряемая величина Ux

подается на сигнальный вход компаратора

11 ме Uk

где она уравновешивается дискретно из- яющейся компенсирующей величиной поступающей на его опорный вход из

циороаналогового преобразователя 22. При этом в преобразователе 22 код-аналог осуществляется неравномерно - ступенчатая отработка Uk за счет того, что при боль- ши с разбалансах отработка сразу ведется старшими разрядами, а по мере уменьшение напряжений разбалансов поочередно отключаются старшие разряды, и окончание

пр

цесса отработки осуществляется только

ступенями младшего разряда. Для этого ре- ве сивный счетчик 21 имеет три группы (младших, средних и старших) двоичных разрядов 28, 29, 30 (фиг. 2), направление счета импульсов в каждом из которых опре- де;яется сигналами с компаратора 11, пост; лающими на триггер 14 знака, уп|; авляющий шинами сложения + и вычи- таь ия - счетчика, Схема (фиг. 2) перестра- иврется в структуру уравновешения

ра. но

личными ступенями при значениях раз- тиДи IUx-Ukl, например

z Ди 16z;

16 z Ди 64z;

64 z Ди, где z- значение ступени младшего разряда, соответственно для групп младших 28, ср дних 29 и старших 30 разрядов, с по- мо цью пороговых элементов 23 и 24 амплитудных анализаторов 12 и 13. При этом помоги срабатывания Ucpi пороговых эле- ме шэв23и24 анализаторов 12 и 13 должны соответствовать весам двоичных разрядов сч тчика 21, например:

UcP231 + 64z;

UcP24 -64z;

UcP23 +16z;

UCp2413 -16z.

Распределение импульсов с амплитудных анализаторов 12 и 13 на входах схем И/ И-НЕ 18 и ИСКЛЮЧАЮЩЕГО ИЛИ 20, а та) же на разрешающем счет входе группы старших разрядов 30 показано на фиг. 2 для исходного состояния, когда Д U 0. При этом на выходе элемента ИЛ И-НЕ 18 появ- ля гтся единица, которая подготавливает группу младших разрядов 28 к работе, а нуш с выходов схемы ИСКЛЮЧАЮЩЕГО ИЛИ 20 и амплитудного анализатора 13 запрещают работу в группах средних и старших разрядов 29 и 30 соответственно. Однако в группе младших разрядов 28 счет импульсов не происходит, так как схема И 16 закрыта нулевыми сигналами с выходов

компаратора 11 и импульсы опорной частоты от генератора 19 импульсов не поступают. Кроме того на выходе элемента И Л И-НЕ 17 появляется единичный сигнал, который прикладывается к входам счетного триггера

31 (фиг. 3) и счетчика 5 адреса, состояние каждого из которых изменяется по спаду этого сигнала,

Таким образом, при подключении измеряемого напряжения Ux в момент времени

ti (фиг. 4), наступление разбаланса Ux UHOM приводит к срабатыванию порогового элемента 2, выходное единичное напряжение которого прикладывается к адресному входу старшего разряда оперативного запоминающего устройства 8 и к информационному входу старшего разряда счетчика 7 адреса, а наступление разбаланса - к срабатыванию компаратора 11, на прямом выходе которого появляется сигнал больше

64 z, который вызывает появление единиц на прямом выходе триггера 14 знака, на статическом входе элемента И 16 и на выходах пороговых элементов 23 амплитудных анализаторов 12 и 13, а также нуля на выходе элемента ИЛИ-НЕ 117. При этом схемы ИЛИ-НЕ 18 и ИСКЛЮЧАЮЩЕЕ ИЛИ 20 блокирует счет импульсов в группах младших и средних разрядов 28 и 29, а амплитудный анализатор 13 включает в работу сразу

старшие разряды 30 реверсивного счетчика 21, установленного триггером 14 знака на сложение импульсов опорной частоты, поступающих через открытую схему И 16 от генератора 19 импульсов. В этот момент, в

дешифраторе 6 длительности выбросов и провалов напряжения (фиг. 3), счетный триггер 31 открывает схему И 33, через которую в счетчик 41 начинают поступать импульсы от тактового генератора 32. Когда разность

z, в момент времени т.2 (фиг. 4), старшие разряды 30 (фиг. 2) отключаются, а импульсы от генератора 19 импульсов заносятся сначала в средние разряды 29 (на интервале времени , затем в младшие

разряды 28 при , в момент времени гз (фиг. 4). При Д U z, в момент времени tj, компаратор 11 возвращается в исходное состояние и схема И 16 закрывается. Счетчик прекращает считать и остающееся на его

выходе неизменным число, соответствующее величине выброса напряжения ,5z (фиг, 4) появляется на выходах Г, Д, Е АЦП 3, и тем самым на информационных входах ОЗУ 8. Разрешение на запись

числа в блок 8 памяти дает единичный сигнал элемента ИЛИ-НЕ 17, включенного на два выхода компаратора 11, по адресу, указанному пороговым элементом 2 и счетчиком 5, который также записывается в регистр 7 адреса.

В момент времени ts (фиг. 4), измеряемое напряжение становится равным Uxz, что снова приводит к неравенству Ux Uk, то срабатывает только пороговый элемент 23 амплитудного анализатора 13. В результате чего, на выходе схемы ИСКЛЮЧАЮЩЕГО ИЛИ 20 появляется единица, которая разрешает счет импульсов в группе средних разрядов 29, а младшие и старшие разряды 28 и 30 блокированы нулями с выходом элемента ИЛИ-НЕ 18 и амплитудного анализатора 12 соответственно. Кроме того на выходе элемента ИЛИ-НЕ 17 опять возникает нулевой импульс. При этом, в момент появления нуля на выходе элемента ИЛИ-НЕ 1.7, счетчик 5 переходит в следующее состояние, а счетный триггер 31 (фиг. 3) перебрасывается на нуль, В результате этого в дешифраторе 6 длительности выбросов и провалов напряжения (фиг. 3), схема И 33 закрывается, а элементы И 35 и 36 открываются. При этом счетчик 41 импульсов прекращает считать и остающиеся на его выходе неизменным число, соответствующее длительности указанного выброса напряжения (интервал времени ti-ts, фиг. 4) появляется на выходе М дешифратора 6, и тем самым на информационном входе ОЗУ 9. Разрешение на запись числа в блок 9 памяти дает единичный сигнал, образуемые за время п на выходе схемы И 36 и подаваемый через элемент ИЛИ 45 на выход К дешифратора, по адресу, считываемому из регистра 7 адреса. Затем через время ti указанный сигнал достигает выхода элемента 39 задержки и сбрасывает на нуль счетчик 41 импульсов, а также через элемент ИЛИ 44 - регистр 7 адреса, В этот момент, через открытую схему И 35, импульсы от тактового генератора 32 поступают на счетный вход счетчика 42. Когда Д U 16z в момент времени те(фиг. 4), средние разряды 29 (фиг. 3) отключаются, и тактовые импульсы заносятся в младшие разряды 28. По окончании процесса данной отработки в момент времени т. (фиг, 4), выходной код реверсивного счетчика 21, соответствующий величине выброса напряжения , записывается в ОЗУ 8.

Если в момент времени ts (фиг. 4), напряжение уменьшается и становится Uk, то пороговый элемент 2 воз- аращается в исходное состояние и его выходное напряжение принимает нулевое

значение, а на инверсном выходе компаратора 11 появляется отрицательный сигнал, модуль которого больше 64z. Это приводит к срабатыванию пороговых элементов 24 амплитудных анализаторов 12 и 13, и установке триггера 14 знака в нуль. При этом, отработка ведется группой старших разрядов 30. В этот момент, в дешифраторе 6 длительности И 35 и открывает элементы И

0 33 и 34. При этом счет импульсов в счетчике 42 прекращается и с его выхода код, соответствующий длительности данного выброса напряжения (интервал времени , фиг. 4), поступает через элемент ИЛИ 43 на вы5 ход М дешифратора и записывается в ячейки блока 9 памяти. В этот момент тактовые импульсы от генератора 32 снова поступают на счетчик 41. Затем, когда A U 16z в момент времени tg (фиг. 4), пороговые элемен0 ты 24 амплитудных анализаторов 12 и 13 возвращаются в исходное состояние и процесс отработки продолжается группой младших разрядов 28, по окончании которого (момент времени tio) информация с выхо5 дов разрядов счетчика 21, соответствующая величине провала напряжения (фиг. 4), записывается в блок 8 памяти,

Таким образом, осуществляется накопление информации в блоках памяти устрой0 ства. Работа анализатора как при выбросах, так и при провалах напряжения аналогична. Только накопление информации в ОЗУ 8 и 9 осуществляется по адресам вида (ХХХХХХХз при выбросах, а при провалах 5 ОХХХХХХХ2. При этом максимальное количество информации определяется циклом работы 2П двоичного счетчика 5, который, переводя по сигналу переноса Я5-триггер4 в нуль, возвращает АЦП 3 в исходное состо0 яние по окончании анализа сигналов.

После накопления достаточного объема информации по содержимым ОЗУ 8 и 9 строятся гистограммы или функции зависимости выбросов и провалов от реального времени

5 их распределения, по которым более достоверно оценивается качество напряжения исследуемой электрической сети.

Положительным эффектом предлагае- . мого изобретения является то, что обработ0 ка информации в процессе анализа случайного процесса выбросов и провалов напряжения осуществляется с помощью преобразователя 1 переменного напряжения в постоянное, аналого-цифрового пре5 образователя 3 и дешифратора 6 длительности выбросов и провалов напряжения, а ее накопление и хранение - в ячейках оперативных запоминающих.устройств 8 и 9, что способствует одновременному параллельному анализу как амплитуды, так и

длительности выбросов и провалов напряжения, и тем самым существенному расширению функциональных возможностей устройства.

Экономическая эффективность предла- г земого устройства определяется теми регулирующими воздействиями как на уровне, так и на длительности выбросов и провалов действующего значения напряжения, которые осуществляются на основании измерений;

Формула изобретения 1. Статистический анализатор выбросов v провалов напряжения, содержащий пороговый элемент, RS-триггер, счетчик и первый блок памяти, отличающийся тем, что, с целью расширения функциональных возможностей за счет анализа длительности выбросов и провалов напряжения, в него введены дешифратор длительности выбросов и провалов напряжения, второй Елок памяти, регистр, аналого-цифровой преобразователь и преобразователь переменного напряжения в постоянное, вход которого является информационным входом г нализатора, а выход подключен к информационному входу аналого-цифрового преобразователя и через пороговый элемент - к старшим разрядам адресного входа первого блока памяти и информационного входа F егистра, выход которого соединен с адрес- ым входом второго блока памяти, информационный вход которого подключен к г ервому входу дешифратора выбросов и г ровалов напряжения, второй выход кото- f ого соединен с входом установки нуля регистра, а третий выход подключен к входу управления записью и считывания второго Ешока памяти и входу разрешения считыва- ия регистра, младшие разряды информа- ионного входа регистра и адресного входа ервого блока памяти соединены с информационным входом счетчика, выход переполнения которого подключен к R-входу триггера, S-вход которого является входом пуска анализатора, а прямой выход соединен с информационным входом дешифратора выбросов и провалов напряжения и Е1ходом запуска аналого-цифрового преобразователя, вход сброса которого соединен с инверсным выходом триггера, а выход конца работы подключен к счетному входу счетчика, к входу запуска дешифратора шбросов и провалов напряжения и входам управления записью регистра и управления записью-считыванием первого блока памяти, информационный вход которого подключен к выходу аналого-цифрового преобразователя.

2.Анализатор по п. 1, от л и ч а ю щий- с я тем, что аналого-цифровой преобразователь содержит реверсивный счетчик, блок сравнения, ключ, два элемента ИЛИ-НЕ,

элемент ИЛИ, триггер, элемент И, циф- роаналоговый преобразователь, два амплитудных анализатора, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и генератор тактовых импульсов, выход которого соединен с пер0 вым входом элемента И, выход которого подключен к счетному входу реверсивного счетчика, разрядный выход которого соединен с входами цифроаналогового преобразователя, выход которого подключен к

5 первому входу блока сравнения, второй вход которого соединен с выходом ключа, информационный и управляющий входы которого являются соответственно информационным и пусковым входами преобразо0 вателя, входом сброса которого является вход сброса реверсивного счетчика, выход Больше блока сравнения соединен с первыми входами амплитудных анализаторов, с S-входом триггера и первыми входами пер5 вого элемента ИЛИ-НЕ и элемента ИЛИ, выход которого подключен к второму входу элемента И, выход Меньше блока сравнения подключен к вторым входам амплитудных анализаторов, к R-входу триггера и

0 вторым входам элемента ИЛИ и первого элемента ИЛИ-НЕ, выход которого является выходом конца работы преобразователя, выход первого амплитудного анализатора соединен с первыми входами второго эле5 мента ИЛИ-НЕ и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которых подключены к выходу второго амплитудного анализатора, выходы второго элемента ИЛИ-НЕ. элемента ИСКЛЮЧАЮЩЕЕ ИЛИ

0 и первого амплитудного анализатора подключены соответственно к разрядным входам разрешения счета реверсивного счетчика, суммирующий и вычитающий входы которого соединены соответственно с

5 прямым и инверсным выходами триггера.

3.Анализатор по п. 1, отличающий с я тем, что дешифратор длительности выбросов и провалов напряжения содержит счетчики, элементы задержки, элементы И,

0 ИЛИ и генератор тактовых импульсов, выход которого соединен с первыми входами первого и второго элементов И, выходы которых подключены к счетным входам одноименных счетчиков, выходы которых

5 соединены с входами первого элемента . ИЛИ, выход которого является первым выходом дешифратора, информационный вход которого соединен с вторыми входами первого и второго элементов И, вход запуска дешифратора подключен к счетному входу

/

триггера, прямой выход которого соединен с третьим входом первого элемента И, с первым входом третьего элемента И и через первый элемент задержки - с первым входом четвертого элемента И, выход которого подключен к первому входу второго элемента ИЛИ и через второй элемент задержки - к входу обнуления первого счетчика и первому входу третьего элемента ИЛИ, выход которого является вторым выходом .дешифратора, третьим выходом которого является

выход второго элемента ИЛИ, инверсный выход триггера соединен с третьим входом второго элемента И, вторым входом четвертого элемента И и через третий элемент

задержки - с вторым входом третьего элемента И, выход которого соединен с вторым входом второго элемента ИЛИ и через четвертый элемент задержки подключен к второму входу третьего элемента ИЛИ и входу

обнуления второго счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОУРОВНЕВЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ДЛИТЕЛЬНОСТИ ВЫБРОСОВ И ПРОВАЛОВ НАПРЯЖЕНИЯ | 1991 |

|

RU2054195C1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ВЫБРОСОВ И ПРОВАЛОВ НЕСТАЦИОНАРНОГО НАПРЯЖЕНИЯ | 2000 |

|

RU2189631C2 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ФУНКЦИИ МОМЕНТОВ ЕРМАКОВА В.Ф. | 1994 |

|

RU2092897C1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ФУНКЦИЙ МОМЕНТОВ СЛУЧАЙНЫХ ПРОЦЕССОВ | 1998 |

|

RU2178202C2 |

| Статистический анализатор выбросов и провалов напряжения | 1980 |

|

SU947775A1 |

| Адаптивный коммутатор телеизмерительной системы | 1980 |

|

SU877597A1 |

| Анализатор длительности выбросов и провалов напряжения | 1988 |

|

SU1674156A1 |

| ИМИТАТОР РЕАЛИЗАЦИИ СЛУЧАЙНЫХ ИЗМЕНЕНИЙ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 1995 |

|

RU2099863C1 |

| Анализатор величины колебания амплитуды случайного процесса | 1983 |

|

SU1134951A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 2000 |

|

RU2170444C1 |

рит Изобретение относится к электроизме- ;льной технике и может быть использовано при аппаратурном контроле качества электрической энергии по выбросам и провалам значения напряжения. Цель изобретения - расширение функциональных возможностей за счет анализа длительностей выбросов и провалов напряжения. Анализатор содержит пороговый элемент, KS-триггер, счетчик, блоки памяти, дешифратор длительности выбросов и провалов напряжения, регистр, аналого-цифровой преобразователь и преобразователь переменного напряжения в постоянное. 2 з.п. ф-лы, 4 ил.

v УК

Фиг Л

| В.Я | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1993-08-30—Публикация

1990-07-10—Подача