Предлагаемое изобретение относится к области радиосвязи и может быть использовано в широкополосных системах связи.

В настоящее время известен ряд многоканальных устройств, позволяющих вести борьбу с узкополосными помехами. Большинство из известных устройств содержит многоканальный анализатор спектра параллельного типа, каналы которого разбивают полосу частот принимаемого сигнала на m равных полос. Подавление узкополосных помех в каждом из каналов осуществляется различными способами, например в пат. США № 3112452 осуществляется ограничение узкополосных помех в каналах, ипользуется режекция участков спектра сигнала, пораженных узкополосными помехами.

Недостатком рассмотренных устройств является низкая эффективность подавления узкополосных помех.

Наиболее близким по технической сущности к заявляемому объекту является устройство (прототип).

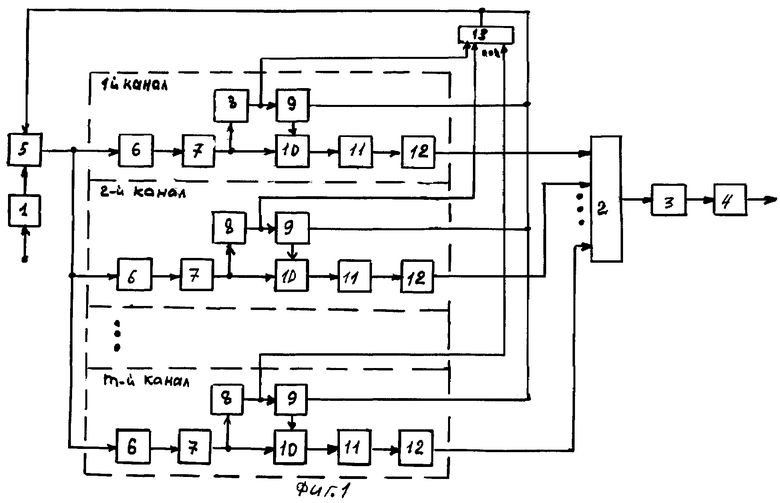

Блок-схема устройства-прототипа представлена на фиг.1, где введены следующие обозначения:

1 - широкополосный входной фильтр с полосой пропускания, большей или равной полосе частот широкополосного сигнала;

2 - сумматор;

3 - ограничитель;

4 - фильтр с полосой пропускания, равной полосе частот широкополосного сигнала;

5 - блок усиления и преобразования частоты принимаемого сигнала в промежуточную частоту;

6 - узкополосный фильтр;

7 - канальный усилитель;

8 - детектор;

9 - схема сравнения;

10 - регулируемый усилитель;

11 - ограничитель;

12 - фазовращатель;

13 - схема выбора минимума (Р.С.).

Широкополосный входной фильтр 1 подключен к высокочастотному входу блока усиления и преобразования 5, выход которого соединен со входами m параллельных каналов подавления, каждый из которых состоит из последовательно соединенных фильтра 6, усилителя 7, регулируемого усилителя 10, ограничителя 11 и фазовращателя 12, а также последовательно соединенных детектора 8 и схемы сравнения 9, при этом вход детектора 9 соединен с усилителями 7, 10, а выход - со схемой выбора минимума (Р.С.), второй вход схемы сравнения 9 - с выходом Р.С. 13 и вторым входом блока усиления и преобразования 5, а выход - со вторым входом усилителя 10, выходы m параллельных каналов соединены с последовательно соединенными сумматором 2, ограничителем 3 и фильтром 4, выход которого является информационным выходом.

Известное устройство работает следующим образом. Предположим, что на вход входного фильтра 1 поступает широкополосный полезный сигнал (ШПС), белый шум и узкополосные помехи. В этом случае устройство осуществляет подавление узкополосных помех методом уменьшения коэффициентов усиления каналов, пораженных помехами. Это происходит следующим образом: PC 13 выбирает минимальное напряжение из напряжений на выходах детекторов 8, которое используется в качестве напряжения автоматической регулировки усиления (АРУ), а также поступает на вычитающие входы схемы сравнения 9, в которых это напряжение вычитается из напряжений, поступающих с выходов соответствующих детекторов 8. Коэффициент усиления усилителей 10 уменьшается с ростом напряжений на выходах схем сравнений 9. По этой причине наибольший коэффициент усиления усилителя 9 будет в канале, суммарный уровень помех в котором наименьший.

Таким образом, при возрастании сигнала на выходе какого-либо фильтра 6 коэффициент усиления соответствующего усилителя 10 будет уменьшаться. В этом случае наибольший сигнал будет на выходе канала с минимальным уровнем помех.

Сигналы с выходов каналов суммируются на сумматоре 2, далее суммарный сигнал через ограничитель 3 и широкополосный фильтр 4 поступает на выход устройства.

Недостатком известного устройства является низкая эффективность подавления узкополосных помех.

Целью предлагаемого изобретения является повышение эффективности подавления узкополосных помех.

Прежде чем пояснять суть предлагаемого изобретения, для удобства укрупним блок-схему прототипа.

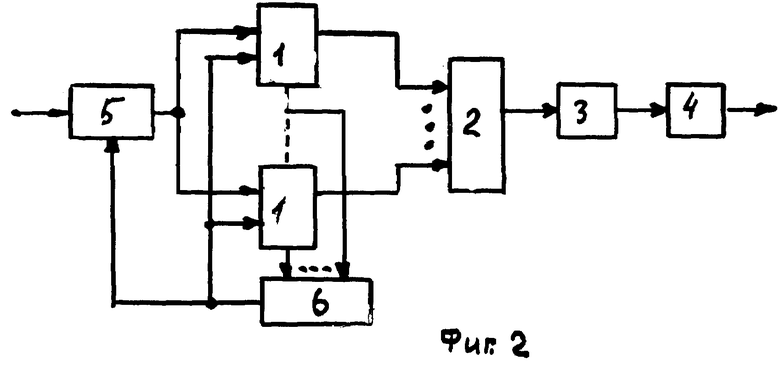

Укрупненная блок-схема устройства представлена на фиг.2, где обозначения блоков 2, 3, 4, 5 - те же, что и на фиг.1, 1 - канал подавления помех, 6 - решающая схема.

При этом вход блока усиления, преобразования и фильтрации 5 является информационным входом, а выход соединен с m параллельными каналами подавления помех 1, первые выходы которых соединены с последовательно соединенными сумматором 2, ограничителем 3 и фильтром 4, вторые выходы - с решающей схемой 6, а управляемый выход - с блоком усиления, преобразования и фильтрации 5 и выходом решающей схемы 6.

При этом блоки 2, 3, 4, 6 укрупненной блок-схемы прототипа абсолютно идентичны соответственно блокам 2, 3, 4, 13 на фиг.1, блок 5 укрупненной блок-схемы прототипа включает в себя последовательно соединенные фильтр 1 и блок усиления и преобразования 5, изображенные на фиг.4, а канал подавления 1 абсолютно идентичен изображенному на фиг.1 каналу подавления помех, состоящему из последовательно соединенных фильтра 6, усилителей 7, 10, ограничителя 11, фазовращателя 12, а также подключенных к первому и второму входам усилителя 10 последовательно соединенных детектора 8 и схемы сравнения 9.

Поставленная цель (повышение эффективности подавления узкополосных помех) достигается за счет введения дополнительно двух коммутаторов, прямого и обратного устройств преобразования Фурье, решающей схемы, устройства задержки и фазирования, а также блока управления.

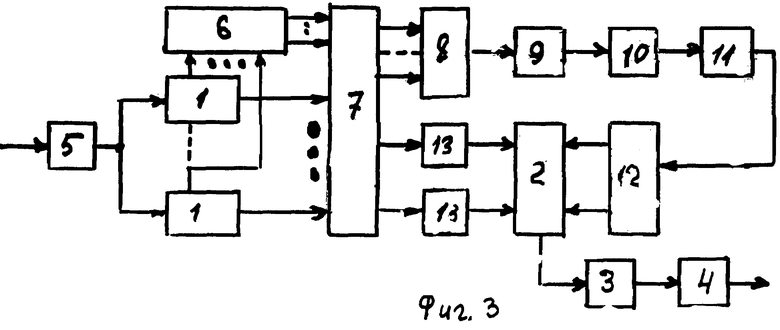

Блок-схема предлагаемого изобретения приведена на фиг.3, где обозначения

1-6 - те же, что и в прототипе;

7 - коммутатор;

8 - распределитель;

9 - устройство прямого преобразования Фурье (ФП);

10 - решающая схема (РС);

11 - устройство обратного преобразования Фурье (ФО);

12, 13 - устройство задержки и фазирования (УФ).

Связи между блоками в заявляемом устройстве те же, что и прототипе, за исключением следующего: решающая схема 6 соединена с управляющими входами коммутатора 7, информационные входы которого соединены с выходами каналов подавления 1, первые выходы - с последовательно соединенными распределителем 8, ФП 9, РС 10, ФО 11 и УФ 12, выходами соединенными с сумматором 2, вторые входы которого соединены через УФ 10 с коммутатором 7.

Заявляемое устройство работает аналогично прототипу, за исключением следующего: сигналы с непораженных помехами каналов поступают с выхода коммутатора 7 через УФ14 на вход сумматора 12. Сигналы с пораженных каналов поступают через коммутаторы 7 и распределитель 8 на дополнительную обработку, которая осуществляется следующим образом.

В этом случае в РС 10 вырабатывается управляющее напряжение, по которому коммутатор 7 подключает выходы пораженных каналов ко входам распределителя 8.

С выхода распределителя 8 сигналы от пораженных каналов поступают на вход устройства ФП 9, где преобразовываются из частотной области во временную. В решающей схеме 10 известными методами (например, режекцией) происходит подавление помехи. Преобразованный таким образом сигнал поступает в блок обратного преобразования Фурье 11, где происходит восстановление сигнала из временной области в частотную. После задержки и фазирования в УФ 12 обработанный таким образом сигнал суммируется в сумматоре 2 с сигналами от непораженных каналов.

Покажем достижение поставленной цели. Как известно, в загруженных диапазонах волн могут сложиться ситуации, когда в известном устройстве могут быть поражены помехами до 90% каналов, которые в прототипе не используются для выделения полезного сигнала. В то же время, как это показано выше, в заявляемом устройстве, пораженные каналы не отбрасываются, а подвергаются вторичной обработке, что значительно повышает эффективность выделения полезного сигнала. Следует заметить, что в заявляемом объекте нет принципиальных трудностей при увеличении разрешающей способности при вторичной обработке пораженных каналов.

В прототипе для эффективного выделения сигнала требуется большое количество параллельных каналов, однако их техническая реализация вызывает принципиальные трудности, так как нельзя создать достаточно узкополосные фильтры. Рассмотрим пример. Стандартный блок защиты (прототип) в одном из диапазонов имеет рабочую полосу 2,8 МГц, двадцать параллельных каналов подавления по 140 кГц. Таким образом, относительная полоса фильтра в канале составляет 5%. Делать полосу фильтра менее 5% нецелесообразно, так как в этом случае ухудшается температурная стабильность, кроме того, у LC-фильтров полосу в принципе нельзя сделать уже 1%. В заявляемом объекте при тех же условиях можно получить эквивалентную полосу анализа 300 Гц. Следовательно, если узкополосная помеха с шириной спектра менее 300 Гц в прототипе поражает канал с полосой 5 кГц, то в заявляемом объекте - только 300 Гц. Что и доказывает достижение поставленной цели.

Рассмотрим аппаратурную реализацию вновь введенных блоков, Решающая схема 6 может быть выполнена любым известным способом и в простейшем случае представляет собой m компараторов, на первые входы которых подаются напряжения с выходов каналов подавления, а на вторые - сформированное каким либо образом пороговое напряжение. Коммутатор 7 является стандартным элементом цифровой техники и в простейшем случае представляет собой двунаправленный ключ, например, на основе м/с серий 133, 564, 533 и т.п.

Устройство задержки и фазирования 12, 13 предназначено для согласования сигналов от различных каналов по времени и по фазе, является стандартам элементом радиотехнических схем и дополнительных пояснений не требует.

Устройства прямого 9 и обратного 11 преобразования Фурье являются стандартными устройствами радиотехнических схем, применяемых для частотного анализа сигнала, могут быть изготовлены любым известным образом, в простейшем случае, например, на основе дисперсионных линий задержки (см., например, В.И.Речицкий. Радиокомпоненты на поверхностных акустических волнах, М.: Радио и связь, 1984, с.87; Н.В.Соболь и др. Аналоговые Фурье-процессоры и их применение. Зарубежная радиоэлектроника, 1983, № 4, с.47-69 и др.).

Решающая схема 10 в простейшем случае представляет собой компаратор, например, на м/с серий 521, 597 и др.

Распределитель 8 предназначен для поочередного подключения пораженных каналов на вход преобразователя Фурье 9, в простейшем случае может быть обычным аналоговым мультиплексором с генератором тактовых импульсов, например, на основе м/с серии 133, 533, 564 и др.

При дополнительном поиске, проведенном авторами согласно п.52 ЭЗ-1-74, не обнаружены объекты со сходными признаками отличительной части. Учитывая это, авторы считают, что предлагаемое решение отвечает критерию "существенные отличия".

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНОЕ УСТРОЙСИТВО ДЛЯ ВЫДЕЛЕНИЯ ШИРОКОПОЛОСНОГО СИГНАЛА ИЗ ПОМЕХ | 1981 |

|

SU1840502A1 |

| КАНАЛ МНОГОКАНАЛЬНОГО УСТРОЙСТВА ДЛЯ ВЫДЕЛЕНИЯ ШИРОКОПОЛОСНОГО СИГНАЛА ИЗ ПОМЕХ | 1983 |

|

SU1840215A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ ШИРОКОПОЛОСНОГО СИГНАЛА ИЗ ПОМЕХ | 1986 |

|

SU1840240A2 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ УЗКОПОЛОСНЫХ ПОМЕХ | 1988 |

|

SU1840158A1 |

| УСТРОЙСТВО ДЛЯ ПОДАВЛЕНИЯ УЗКОПОЛОСНЫХ ПОМЕХ | 1983 |

|

SU1840214A1 |

| СПОСОБ ОБРАБОТКИ ШУМОПОДОБНОГО СИГНАЛА | 1977 |

|

SU1840484A1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ ПОМЕХ | 1998 |

|

RU2153768C2 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ СТРУКТУРНЫХ ПОМЕХ | 1992 |

|

RU2114502C1 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ ШИРОКОПОЛОСНЫХ ПОМЕХ | 2001 |

|

RU2196385C2 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ ПОМЕХ ДЛЯ ПРИЕМНИКОВ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1999 |

|

RU2154341C1 |

Изобретение относится к области радиосвязи и может быть использовано в широкополосных системах связи. Техническим результатом изобретения является повышение эффективности подавления узкополосных помех, который достигается за счет введения дополнительно двух коммутаторов, прямого и обратного устройств преобразования Фурье, решающей схемы, устройства задержки и фазирования, а также блока управления. 3 ил.

Устройство выделения широкополосного сигнала из помех, содержащее блок усиления, преобразования и фильтрации, вход которого является информационным входом устройства, а выход блока усиления, преобразования и фильтрации подключен ко входам m каналов подавления помех, первые выходы которых подключены ко входам блока формирования управляющего напряжения, а также последовательно соединенные сумматор, ограничитель и фильтр, выход которого является выходом устройства, отличающееся тем, что, с целью повышения помехозащищенности при одновременном упрощении устройства, введены коммутатор, m первых блоков задержки и фазирования и последовательно соединенные распределитель, блок прямого преобразования Фурье, блок режекции, блок обратного преобразования Фурье и второй блок задержки и фазирования, выходы которого подключены к первым входам сумматора, к вторым входам которых подключены выходы m первых блоков задержки и фазирования, ко входам которых и входам распределителя подключены соответствующие выходы коммутатора, к управляющим входам которого подключены выходы блока формирования управляющего напряжения, а выходы m каналов подавления помех подключены к соответствующим входам коммутатора.

Авторы

Даты

2006-07-20—Публикация

1985-09-05—Подача