Известны однэтактные реверсивные двоичные счетчики, содержащие трансформатор, транзистор и резисторы.

Предложенный счетчик отличается от известных тем, что он содержит импульсный трансформатор, обмотки которого последовательно соединены с обмотками запоминающего трансформатора, и транзистор.

База этого транзистора через резистор подключена к обмотке запоминающего трансформатора, эмиттер - к одной из шин питания, а коллектор связан с базой другого транзистора.

Это позволяет повысить быстродействие, помехоустойчивость, исключить подбор входящих элементов, а также обеспечить ввод информации параллельным кодом без снятия напряжения питания.

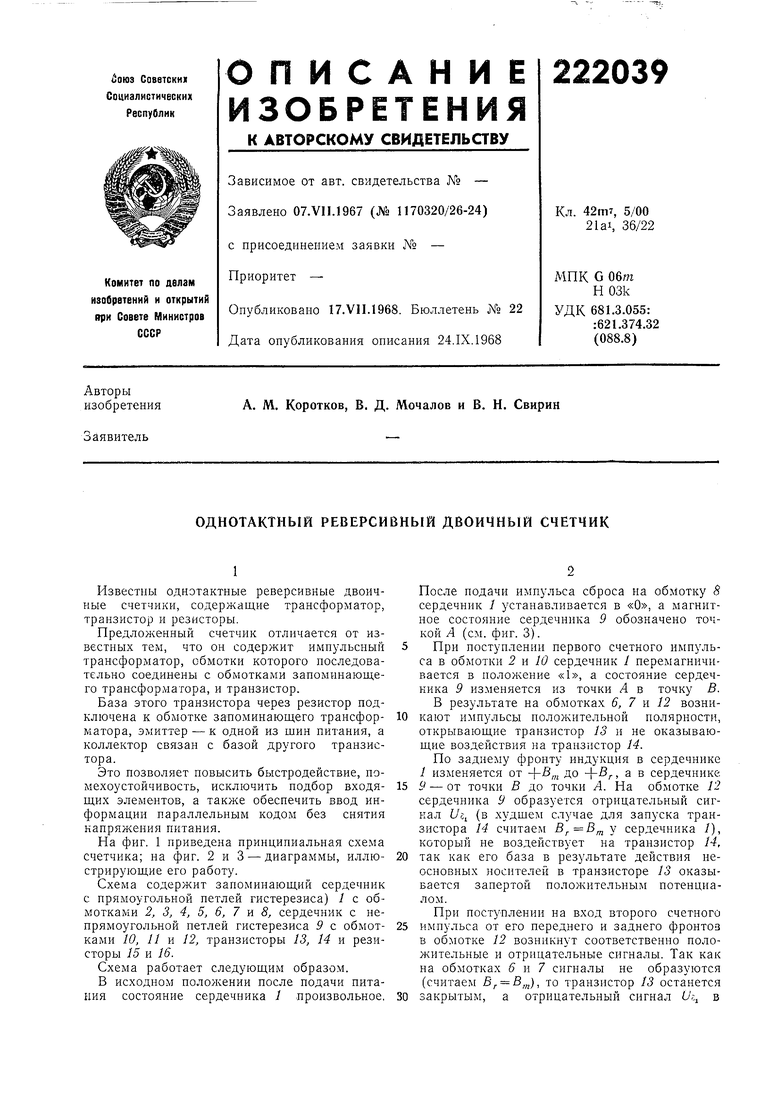

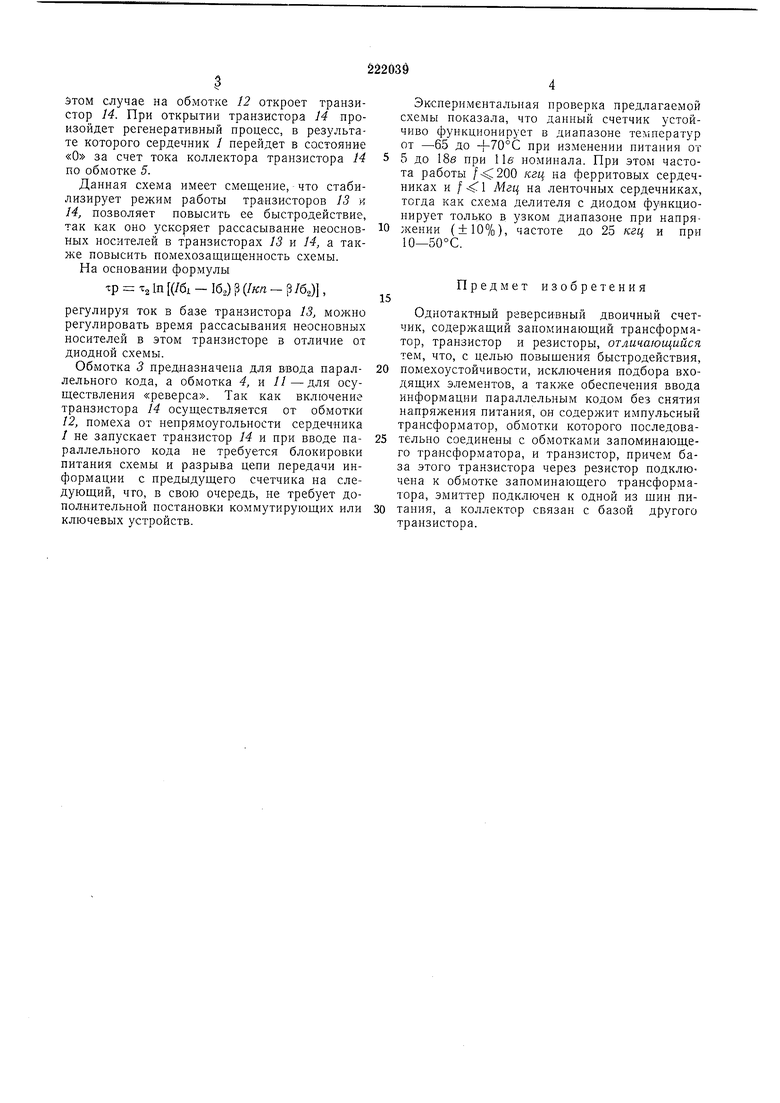

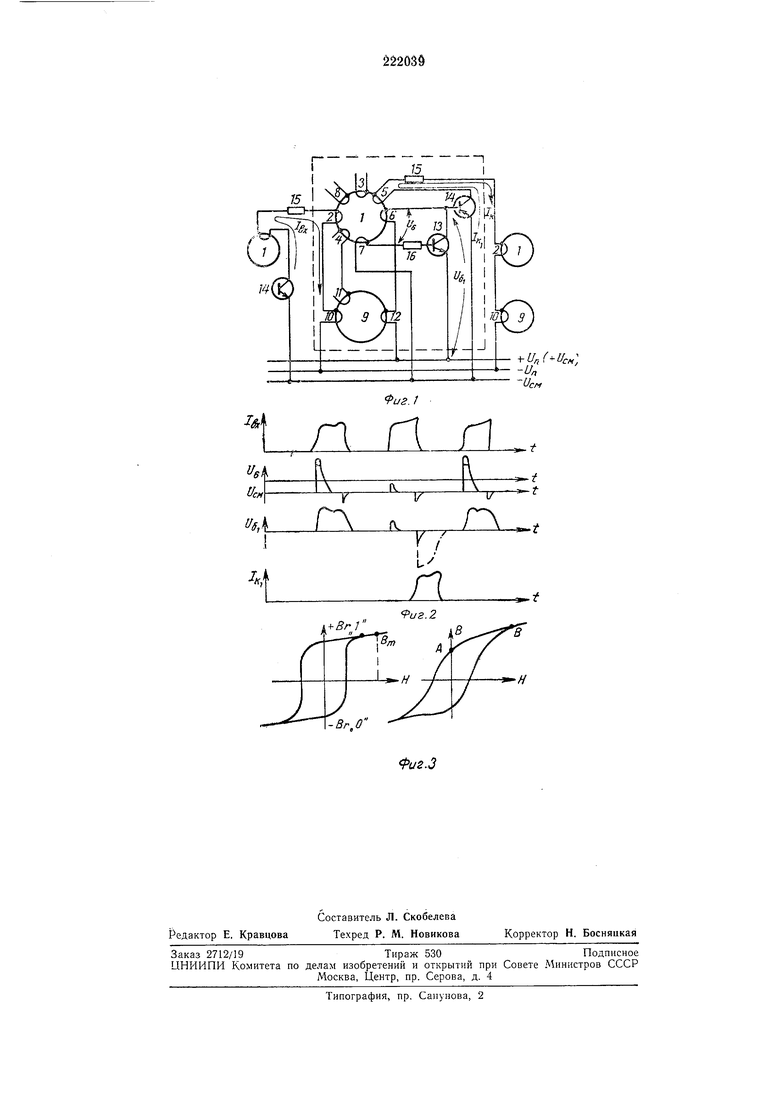

На фиг. 1 приведена принципиальная схема счетчика; на фиг. 2 и 3 - диаграммы, иллюстрирующие его работу.

Схема содержит запоминающий сердечник с прямоугольной петлей гистерезиса) 1 с обмотками 2, 3, 4, 5, 6, 7 и 8, сердечник с непрямоугольной нетлей гистерезиса 9 с обмотками 10, 11 и 12, транзисторы 13, 14 и резисторы 15 и 16.

После подачи импульса сброса на обмотку 8 сердечник 1 устанавливается в «О, а магнитное состояние сердечника 9 обозначено точкой А (см. фиг. 3).

При поступлении первого счетного импульса в обмотки 2 и Ш сердечник / перемагничивается в положение «1, а состояние сердечника 9 изменяется из точки А в точку В. В результате на обмотках 6, 7 и 12 возникают импульсы положительной полярности, открывающие транзистор 13 и не оказывающие воздействия на транзистор 14.

По заднему фронту индукция в сердечнике } изменяется от +В,„ до +5, а в сердечнике

9 - от точки В до точки Л. На обмотке Г2 сердечника 9 образуется отрицательный сигнал t/o (Б худщем случае для запуска транзистора 14 считаем сердечника /), который не воздействует на транзистор 14,

так как его база в результате действия неосновных носителей в транзисторе 13 оказывается запертой положительным потенциалом.

При поступлении на вход второго счетного

импульса от его переднего и заднего фронтов в обмотке 12 возникнут соответственно положительные и отрицательные сигналы. Так как на обмотках 5 и 7 сигналы не образуются (считаем Б В,), то транзистор 13 останется этом случае на обмотке 12 откроет транзистор 14. При открытии транзистора 14 произойдет регенеративный процесс, в результате которого сердечник / перейдет в состояние «О за счет тока коллектора транзистора 14 по обмотке 5. Данная схема имеет смещение, что стабилизирует режим работы транзисторов 13 и 14, позволяет повысить ее быстродействие, так как оно ускоряет рассасывание неосновных носителей в транзисторах 13 и 14, а также повысить помехозащищенность схемы. На основании формулы тр Т2 In (/61 - 16,) р (1кп - р 16,), регулируя ток в базе транзистора 13, можно регулировать время рассасывания неосновных носителей в этом транзисторе в отличие от диодной схемы. Обмотка 3 предназначена для ввода парал- 20 лельного кода, а обмотка 4, и 11-для осуществления «реверса. Так как включение транзистора 14 осуществляется от обмотки 2, помеха от непрямоугольности сердечника / не запускает транзистор 14 и при вводе па- 25 раллельного кода не требуется блокировки питания схемы и разрыва цепи передачи информации с предыдущего счетчика на еледующий, что, в свою очередь, не требует дополнительной постановки коммутирующих или 30 ключевых устройств. 5 10 Экспериментальная проверка предлагаемой схемы показала, что данный счетчик устойчиво функционирует в диапазоне температур от -65 до -j-70°C при изменении питания от 5 до 188 при 11б номинала. При этом частота работы кгц на ферритовых сердечниках и /- Мгц на ленточных сердечниках, тогда как схема делителя с диодом функционирует только в узком диапазоне при напряженин (±10%), частоте до 25 кгц и при 10-50°С. Предмет изобретения Однотактиый реверсивный двоичный счетчик, содержащий запоминающий трансформатор, транзистор и резисторы, отличающийся тем, что, с целью повышения быстродействия. помехоустойчивости, исключения подбора входящих элементов, а также обеспечения ввода информации параллельным кодом без снятия напряжения питания, он содержит импульсный трансформатор, обмотки которого последовательно соединены с обмотками запоминающего трансформатора, и транзистор, причем база этого транзистора через резистор подключена к обмотке запоминающего трансформатора, эмиттер подключен к одной из шин питания, а коллектор связан с базой другого транзистора.

1 n П n .

5

Uc.

r , , ГЛ ..

Us,

r

Un

-Uc

IT

/

u.t

fus.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоустойчивый магнито-транзисторный элемент | 1973 |

|

SU438097A1 |

| СПОСОБ ВЫПОЛНЕНИЯ ЛОГИЧЕСКИХ ОПЕРАЦИЙ НА МАГНИТОПОЛУПРОВОДНИКОВЫХ ЭЛЕМЕНТАХ | 1970 |

|

SU265948A1 |

| ОДНОТАКТНЫЙ РЕВЕРСИВНЫЙ ДВОИЧНЫЙ СЧЕТЧИК | 1969 |

|

SU242517A1 |

| Транзисторный ключ | 1987 |

|

SU1443162A1 |

| ОДНОТАКТНЫЙ РЕВЕРСИВНЫЙ ДВОИЧНЫЙ СЧЕТЧИК | 1970 |

|

SU264821A1 |

| Устройство управления силовым магнитно-транзисторным ключом | 1974 |

|

SU683022A1 |

| Устройство для управления силовым транзисторным ключом | 1983 |

|

SU1133663A1 |

| Генератор телевизионной строчной развертки | 1988 |

|

SU1637027A1 |

| Преобразователь постоянного напряжения | 1987 |

|

SU1504771A1 |

| Однотактный преобразовательНАпРяжЕНия | 1979 |

|

SU832685A1 |

Даты

1968-01-01—Публикация