Предлагаемое устройство относится к аналоговой вычислительной технике, точнее к устройствам для запоминания однозначных функций.

В известных запоминающих устройствах, содержащих операционные усилители и конденсаторы во входных цепях и в цепи обратной связи, где применяются транзисторные ключевые схемы, существуют утечка заряда с конденсаторов за счет конечного сопротивления ключевых схем.

Предлагаемое устройство отличается тем, что для повышения точности за счет уменьщения утечки заряда конденсаторов в нем применены ключевые схемы с двумя гальванически развязанными транзисторами.

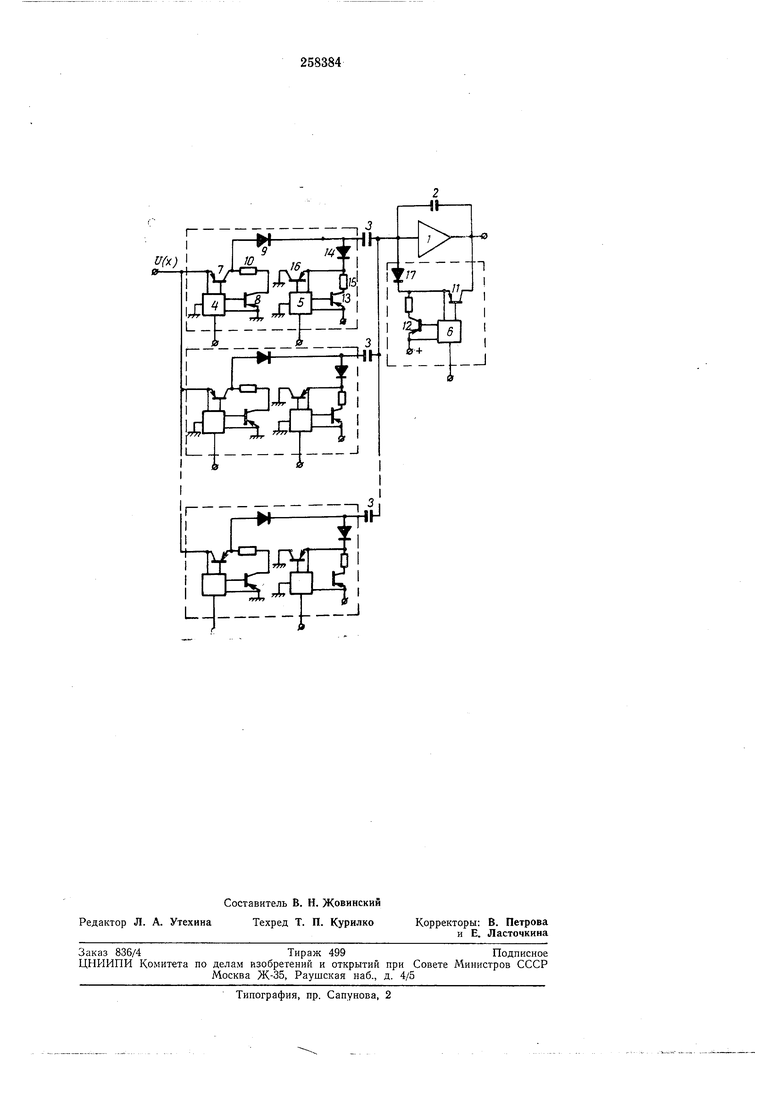

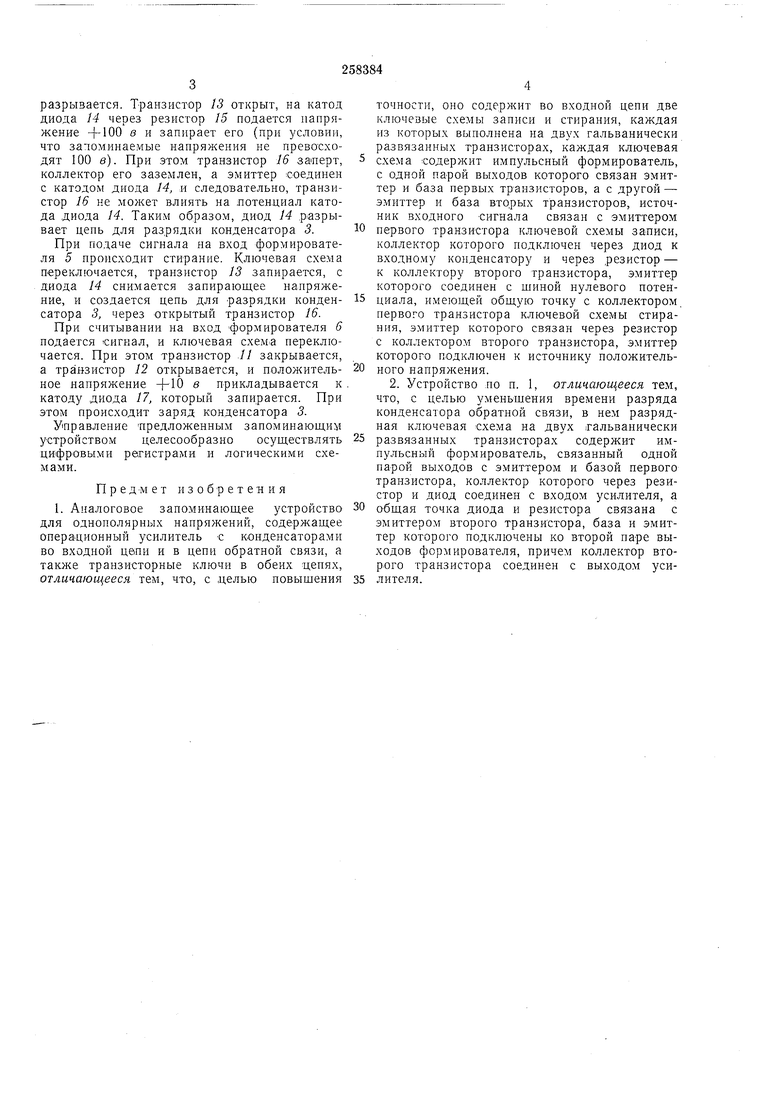

Схема устройства показана на чертеже.

Устройство содержит усилитель / с конденсатором 2 в цепи обратной связи и с группой входных конденсаторов 3.

Во входной цепи устройство содержит импульсные формирователи 4 и 5 и формирователь 6 разрядной ключевой схемы.

В устройстве применены три ключевые схемы: записи, стирания и разряда.

Все ключевые схемы состоят из двух гальванически развязанных транзисторов, работающих таким образом, что в каждом из двух состояний один триод открыт, другой закрыт.

Ключевая схема записи представляет собой два гальванически развязанных транзистора 7 и 8.

Запись осуществляется следующим образом.

При подаче сигнала на вход формирователя 4 идет запоминание входного напрял ения. В этом случае транзистор 7 открыт и напряжение через диод 9 заряжает конденсатор 3,

подключенный ко входу усилителя /. Транзистор 8 заперт и не влияет на работу схемы, эмиттер его заземлен, а коллектор череЗ резистор 10 соединен с анодом диода 9. Во время записи, когда на входе формирователя

6 отсутствует сигнал, транзистор // открыт, ключевая схема разряда шунтирует усилитель / и запертый транзистор /2 не влияет на работу. При снятии сигнала со входа формирователя 4, ключевая схема записи переключается. Транзистор 7 запирается, и открывается транзистор 8, который подключает «землю к аноду диода 9. Последний запирается, прерывая тем самым цепь разрядки конденсатора 3. Запоминание напряжений, поданных на другие входы стирания, происходит аналогично.

Для стирания (применяется идентичная ключевая схема. При отсутствии единицы на входе формиразрывается. Транзистор 13 открыт, на катод диода 14 через резистор 15 подается напряжение + 100 в и запирает его (при условии, что запоминаемые напряжения не превосходят 100 б). При этом транзистор 16 заперт, коллектор его заземлен, а эмиттер соединен с катодом диода 14, и следовательно, транзистор 16 не может влиять на .потенциал катода диода 14. Таким образом, диод 14 р.азрывает цепь для разрядки конденсатора 3. При подаче сигнала на вход формирователя 5 происходит стирание. Ключевая схема переключается, транзистор 13 запирается, с диода 14 снимается запирающее напряжение, и создается цепь для разрядки конденсатора 3, через открытый транзистор 16. При считывании на вход -формирователя 6 подается сигнал, и ключевая схем.а иереключается. При этом транзистор 11 закрывается, а транзистор 12 открывается, и ноложительное напряжение -f-lO в прикладывается к катоду диода 17, который запирается. При этом происходит заряд конденсатора 3. Управление -предложенным запоминающим устройством целесообразно осуществлять цифровыми регистрами и логическими схемами. Ир ед мет изобретения 1. Аналоговое запоминающее устройство для однополярных напряжений, содержащее операционный усилитель с конденсаторами во входной цепи и в цепи обратной связи, а также транзисторные ключи в обеих цепях, отличающееся тем, что, с делью повыщения точности, оно содержит во входной цепи две ключевые схемы записи и стирания, каждая из которых выполнена на двух гальванически развязанных транзисторах, каждая ключевая схема содержит импульсный формирователь, с одной парой выходов которого связан эмиттер и база первых транзисторов, а с другой- эмиттер и база вторых транзисторов, источник входного сигнала связан с эмиттером первого транзистора ключевой схемы записи, коллектор которого подключен через диод к входному конденсатору и через резистор - к коллектору второго транзистора, эмиттер которого соединен с шиной нулевого потенциала, имеющей общую точку с коллектором. первого транзистора ключевой схемы стираВИЯ, эмиттер которого связан через резистор с коллектором второго транзистора, эмиттер которого подключен к источнику положительного напряжения. 2. Устройство ло п. 1, отличающееся тем, что, с целью уменьщения времени разряда конденсатора обратной связи, в нем разрядная ключевая схема на ДВУХ гальванически развязанных транзисторах содержит импульсный формирователь, связанный одной парой выходов с эмиттером и базой первого транзистора, коллектор которого через рези диод соединен с входом усилителя, а точка диода и резистора связана с эмиттером второго транзистора, база и эмиттер которого подключены ко второй паре выходов формирователя, причем коллектор втовыходом усирого транзистора соединен с лителя.

тЛг7 I

- ---TL: L J

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ЦИФРОВОЙ ИНДИКАЦИЕЙ | 1973 |

|

SU399857A1 |

| Преобразователь постоянного напряжения | 1987 |

|

SU1444921A1 |

| Устройство управления газоразрядной индикаторной панелью | 1989 |

|

SU1709388A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели переменного тока | 1985 |

|

SU1295439A1 |

| Однотактный преобразователь напряжения постоянного тока | 1983 |

|

SU1181077A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU822295A1 |

| ИСТОЧНИК ПИТАНИЯ | 1991 |

|

RU2017202C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СТЕКЛООМЫВАТЕЛЕМ ТРАНСПОРТНОГО СРЕДСТВА | 1992 |

|

RU2089416C1 |

| Устройство для регулирования температуры | 1988 |

|

SU1594503A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

Даты

1970-01-01—Публикация