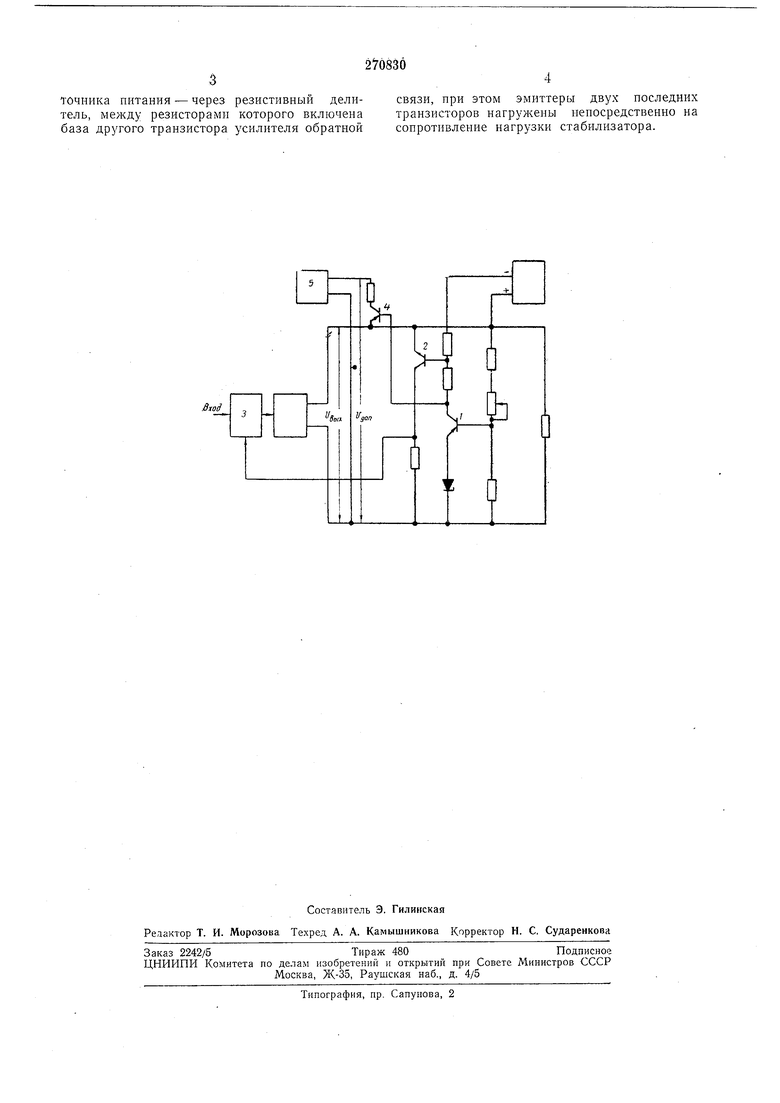

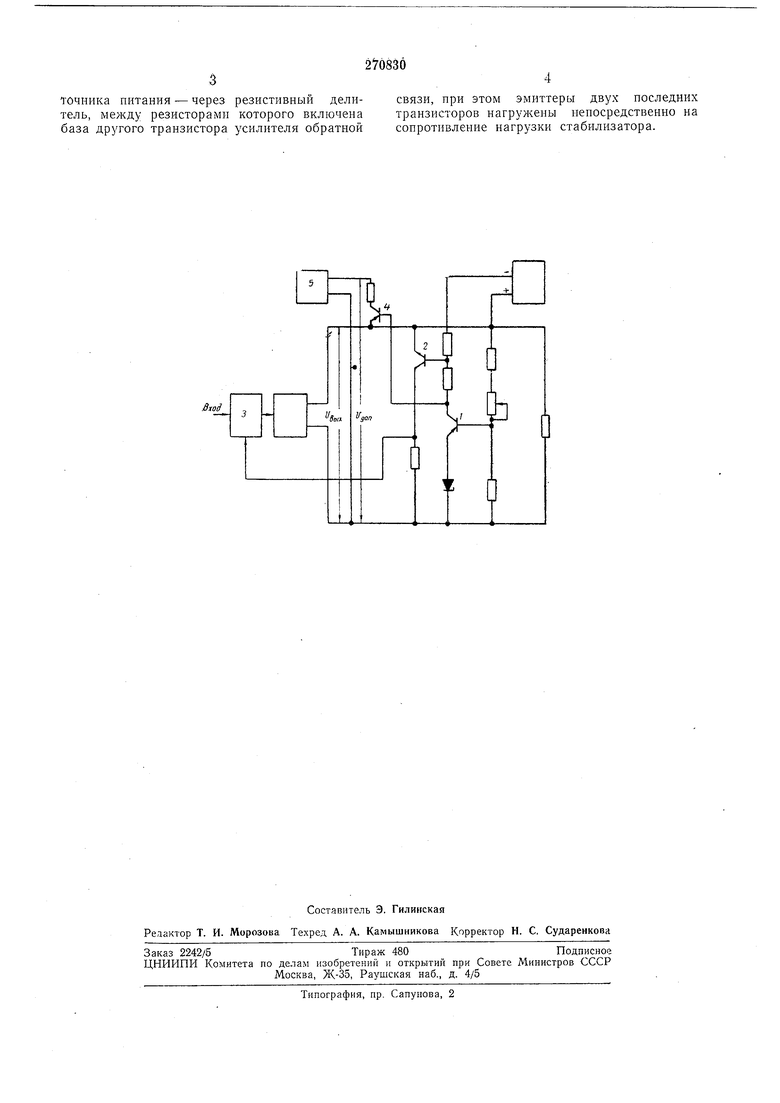

Известны полупроводниковые стабилизаторы напряжения, у которых осуществляется подавление отрицательных выбросов выходного напряжения. Предлагаемое устройство отличается от известных тем, что один из транзисторов усилителя обратной связи стабилизатора подсоединен коллектором одновременно к базе транзистора каскада подавления отрнцательных выбросов выходного напряжения и к отрицательному полюсу своего источника питания - через резистивный делитель, между резисторами которого включена база другого транзистора усилителя обратной связи, при этом эмиттеры двух последних транзисторов нагружены непосредственно на сопротивление нагрузки стабилизатора, в результате чего уменьшается величина выбросов напряжения на выходе стабилизатора и повышается коэффициент стабилизации. На чертеже изображена принципиальная схема предлагаемого стабилизатора. Работа устройства происходит следующим образом. В статическом режиме работы стабилизатора траизисторы 1 и 2 находятся в режиме усиления. Фаза выходного сигнала от транзистора 2 выбрана с таким расчетом, что при уменьшении выходного напрял ения стабилизатора она отпирает регулирующий орган 3 стабилизатора, При понижении выходного напрян ения стабилизатора в переходном релшме транзистор 1 полностью запирается, транзистор 2 4 отпирается и происходит включение дополнительного нестабилизпрованного источника 5 (дол ), что предотвращает появление отрицательного выброса на выходе стабилизатора. Одновременно выходной сигнал транзистора 2 приводит к отпиранию регулирующего его органа 3 и, следовательно, увеличению выходного напряжения. По истечении времени иереходного процесса устанавливается выходное напря}кение стабилизатора, и транзистор 4 снова запирается. Таким образом, транзистор 4 работает только при переходных режимах и рассеиваемая мощность незначительна. Предмет изобретения Стабилизатор напряжения, содержащий усилитель обратной связи и каскад подавления отрицательных выбросов вы.одного напряжения, отличающийся тем, что, с целью повышения коэффициента стабилизации и уменьшения выбросов выходного напряжения, один из транзисторов зтилителя обратной связи подсоединен коллектором одновременно к базе транзистора каскада подавления непосредственно и к отрицательному полюсу своего источника питания - через резистивный делитель, между резисторами которого включена база другого транзистора усилителя обратной

связи, ири этом эмиттеры двух последних транзисторов нагружены неносредственно на сопротивление нагрузки стабилизатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизатор постоянного напряжения | 1974 |

|

SU506837A1 |

| СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ | 1972 |

|

SU327556A1 |

| СТАБИЛИЗАТОР НАПРЯЖЕНИЯ | 1970 |

|

SU277886A1 |

| ВСЕСОЮЗНАЯ 'nAr:[iTHO-v::;;,--•:.;.:!;;EHb;iHO.i?KA IВ. М. Машенков | 1970 |

|

SU281553A1 |

| Стабилизатор постоянного напряжения с защитой от перегрузки | 1976 |

|

SU615467A1 |

| Низковольтный стабилизатор постоянного напряжения | 1974 |

|

SU613312A1 |

| Широтно-импульсный модулятор | 1974 |

|

SU534030A1 |

| Устройство для регулирования температуры | 1982 |

|

SU1024891A1 |

| Стабилизированный источник питания | 1981 |

|

SU1029167A1 |

| СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ | 2016 |

|

RU2628763C1 |

Вход

Даты

1970-01-01—Публикация