Изобретение относится к области импульсной техники и может быть использовано в различных устройствах для смешивания импульсов как совпадающих, так и несовпадающих по времени.

По основному авт. ев № 250991 известны смесители импульсных сигналов, обеспечивающие сложение или вычитание совпадающих и несовпадающих по времени импульсов с сохранением на выходе пропорциональности амплитуды сигнала суммы или разности амплитуд смещиваемых сигналов.

Однако известные устройства обеспечивают сложение или вычитание несовпадающих по времени импульсов при условии, что на выход смесителя, с которого снимается импульс синхронизации, поступающий на управляющие электроды тиристоров, должен поступать импульс, задний фронт которого отстает от заднего фронта импульса, поступающего на другой вход смесителя. Если очередность импульсов другая, то команда на разряд тиристоров формируется до того момента, когда обе зарядные цепочки (по обоим каналам) получат полную информацию об амплитуде входных импульсов, в результате чего на выходе не сохраняется пропорциональность разности или сумма входных амплитуд.

ступления в предлагаемом смесителе между отсекающим диодом и входом усилительного каскада включена цепочка, состоящая из триггерной ячейки и дифференцирующей цепи, при

этом первый вход смесителя подключен через последовательно соединенные конденсатор и дополнительный отсекающий диод к отсекающему диоду.

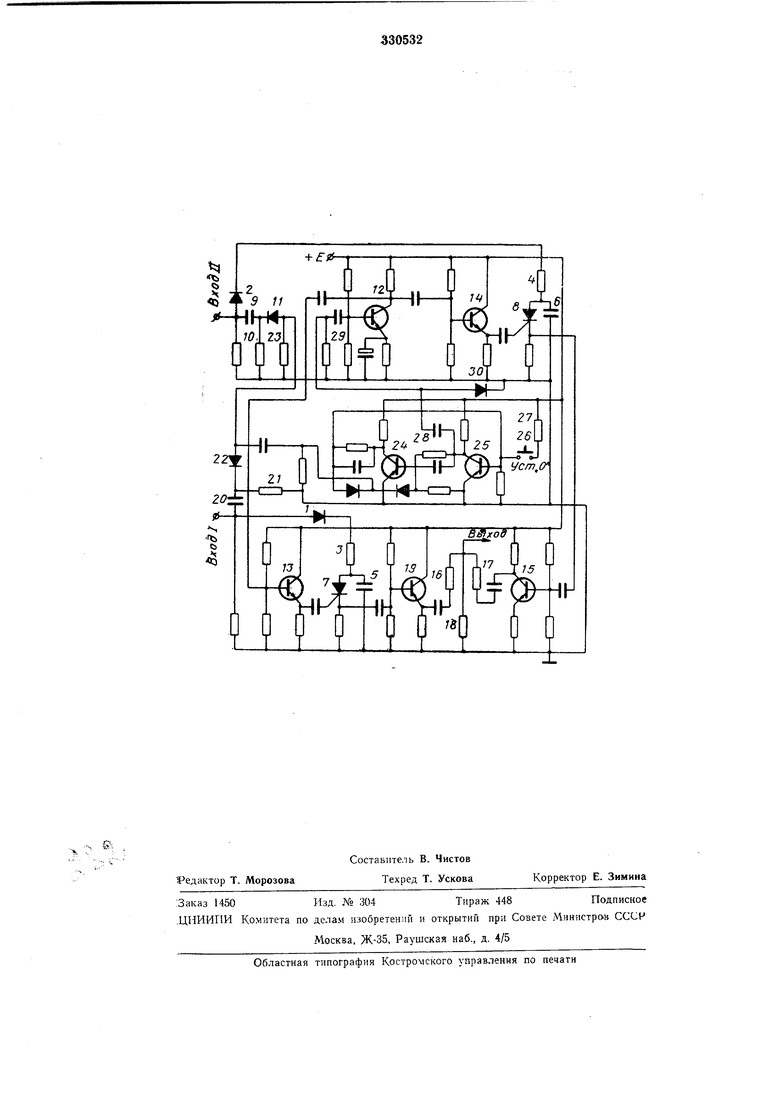

На чертеже дано предлагаемое устройство.

Предлагаемый смеситель импульсных сигналов включает в себя зарядные цепочки, идентичные по своему построению и включаемые в каждый из двух каналов, состоящие из диодов J и 2, резисторов 3 и 4, конденсаторов 5 и 5,

тиристоров 7 v( 8.

Синхроимпульсы одного канала формируются конденсатором 9, резистором 10 и отсекающим диодом 11 и усиливаются каскадом, собранным на транзисторе 12. Устройство содержит также эмиттерные повторители 13 и 14, фазоинвертор 15, смесительную Т-образную ячейку на резисторах 16, 17 и 18, эмиттерный повторитель 19. Синхроимпульсы другого канала формируются конденсатором 20, резистором 21 и отсекающим диодом 22. Сформированные импульсы смешиваются на резисторе

23,затем триггерной ячейкой на транзисторах

24,25 формируется импульс, длительность которого определяется величиной задержки по

пары импульсов. Начальная установка триггерной ячейки осуществляется с помощью кнопочного выключателя 26, обеспечивающего подключение источника питания 4-Е через резистор 27 к базе соответствующего транзистора триггерной ячейки. Между выходом триггерной ячейки и входом усилительного каскада транзистора 12 подключена дифференцирующая цепь (конденсатор) 28 и резистор 29, выделяющая задний фронт импульса с триггерной ячейки, соответствующего по временному положению последнему из задних фронтов входной пары импульсов. Параллельно резистору 29 подключен диод 30, закорачивающий импульс положительной полярности с выхода дифференцирующей цепи, состоящей из конденсатора 28 и резистора 29.

Устройство работает следующим образом.

На входы смесителя поступают импульсы, несовпадающие по времени. Пройдя через диоды , 2 н резисторы 3, 4, они заряжают конденсаторы 5, 6. Входные импульсы дифференцируются также / С-цепями (конденсаторы 9, 20 и резисторы 10, 21) и затем через отсекающие диоды 11, 22 отрицательные импульсы, соответствующие задним фронтам входных импульсов, поступают на резистор 23, образующ ш вместе с диодами 11, 22 каскад «ИЛИ. С резистора 23 пара отрицательных импульсов поступает на триггерную ячейку на транзисторах 24, 25, предварительно установленную в исходное положение с помощью выключателя 26. С выхода триггерной ячейки импульс положительной полярности, длительность которого равна времени задержки между задними фронтами входных импульсов, поступает цепь на конденсатор 28, резистор 29,

диод 30, которая выделяет его задний фронт в внде импульса отрицательной полярности. Этот импульс, соответствующий по времени заднему фронту последнего, из входных импульсов (независимо от их очередности следования) усиливается и инвертируется усилительным каскадом на транзисторе 12 и затем через эмнттерные повторители 13, 14 поступает на управляющие входы тиристоров

7,8.

При открывании тиристоров 7, 8 обеспечивается одновременный разряд конденсаторов 5, 6 через тиристоры на соответствующие нагрузочные резисторы, с которых сигнал через

фазоинвертор 15 и повторитель 19 поступает на смесительную Г-образную ячейку 16, 17 и 18, с выхода которой снимается сигнал, пропорциональный разности результирующих всплесков и пропорциональный разности амплитуд входных импульсов.

при сложении процесс повторяется, но вместо фазоинвертора 15 необходимо применить эмиттерный повторитель.

Предмет изобретения

25

Смеситель имлульсных сигналов по авт. св. № 250991, отличающийся тем, что, с целью обеспечения сложения или вычитания импульсов независимо от очередности поступления, между отсекающим диодом и входом усилительного каскада включена цепочка, состоящая из триггерной ячейки и дифференцирующей цепи, при этом первый вход смесителя

подключен через последовательно соединенные конденсатор и дополнительный отсекающий диод к отсекающему диоду.

| название | год | авторы | номер документа |

|---|---|---|---|

| Блок логических схем устройства для импульсного управления высоковольными вентилями -фазного каскадно-мостового преобразователя | 1973 |

|

SU599713A1 |

| ЭЛЕКТРОИСКРОВОЙ ОТМЕТЧИК ДИСБАЛАНСА И ФОРМИРОВАТЕЛЬ ВРЕМЕНИ РАЗРЯДА | 1992 |

|

RU2075736C1 |

| Дискриминатор момента перехода через максимум видеосигналов произвольной формы | 1972 |

|

SU437212A1 |

| Устройство поиска и автосопровождения сигнала | 1972 |

|

SU441639A1 |

| Предоконечный каскад блока управления мощным переключательным транзистором | 1981 |

|

SU970588A1 |

| ВЫСОКОВОЛЬТНЫЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1991 |

|

RU2044402C1 |

| Расширитель импульсов | 1977 |

|

SU687575A1 |

| Одноканальное устройство для фазового управления трехфазным тиристорным преобразователем | 1985 |

|

SU1252882A1 |

| Отметчик верхней мертвой точки поршня в цилиндре двигателя внутреннего сгорания | 1982 |

|

SU1063782A1 |

| Формирователь импульсов | 1980 |

|

SU886225A1 |

Даты

1972-01-01—Публикация