Изобретение относится к автоматике и вычислительной технике.

Известен усилитель мощности по авт. св. № 258381.

Цель изобретения - расширение полосы пропускания усилителя и увеличение его нагрузочной способности. Достигается она тем, что в предлагаемом усилителе между эмиттером транзистора динамической нагрузки и конденсатором, подключенным к месту соединения резистора и диода, включен резистор, а нагрузка подключена между эмиттером того же транзистора и средней точкой двух источников питания.

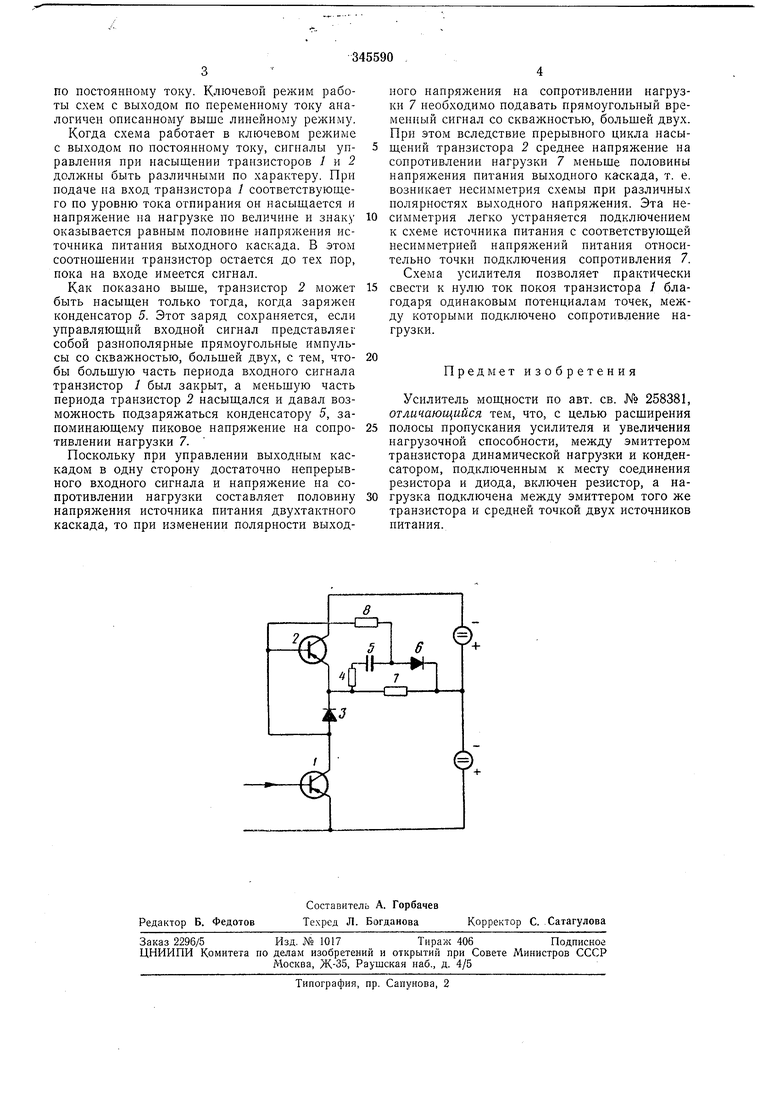

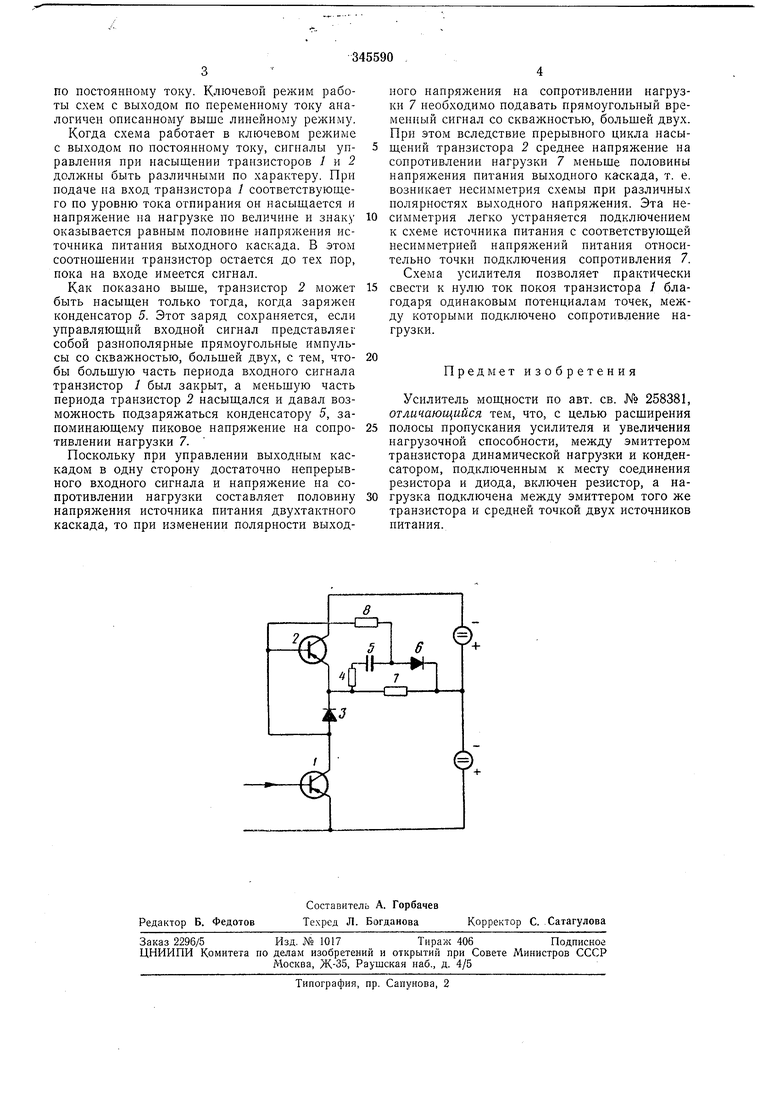

На чертеже приведена схема предлагаемого усилителя мощности.

Однотипные транзисторы 7 и 2 включены последовательно по питанию. Коллектор транзистора / соединен с базой транзистора 2 и переход база - эмиттер транзистора 2 зашунтирован диодом 3. Цепь из последовательно соединенных резистора 4, конденсатора 5 и диода 6 включена между эмиттером транзистора 2 и средней точкой источиика питания параллельно сопротивлению нагрузки 7 с подключением базы транзистора 2 через резистор 8 к точке связи конденсатора 5 и диода 6. Такое подключение цепочки из резистора 4, конденсатора 5 и диода 6 позволяет практически исключить потребление мощности в режиме покоя.

Транзистор / усилителя управляется входным током. Транзистор 2 управляется током транзистора /, а также током от дополнительного источника питания, образуемого цепочкой из резистора 4, конденсатора 5 и диода 6, подключенной но переменному току параллельно сопротивлению нагрузки 7. Диод 6 выпрямляет напряжение на сопротивлении 7, конденсатор 5 запоминает пиковое напряжение в первый полупериод входного сигнала. Резистор 4 улучшает форму выходного сигнала и расширяет полосу пропускания усилителя. Резистор 8 в цепи базы транзистора 2 ограничивает ток в цепи базы от дополнительного источника питания.

Усилитель имеет различное усиление по полyпepиoдa r входного сигнала. Когда открыт транзистор /, транзистор 2 заперт падением напряжения на диоде 3, и усиление с.хемы но

току составляет (Зь При запирании транзистора / открывается транзистор 2. Транзис-. тор 2 управляется транзистором /. В этот полуперпод входного сигнала транзисторы 1 и 2 включены последовательно и коэффициент

усиления по току составляет ргрз- Однако введение глубокой отрицательной обратной связи ликвидирует несимметрпю статической характеристики выходного каскада с любой степенью точности.

по постоянному току. Ключевой режим работы схем с выходом по переменному току аналогичен описанному выше линейному режиму.

Когда схема работает в ключевом режиме с выходом по постоянному току, сигналы управления при насыщении транзисторов 1 и 2 должны быть различными по характеру. При подаче на вход транзистора / соответствующего по уровню тока отпирания он насыщается и напряжение на нагрузке по величине и знаку оказывается равным половине напряжения источника питания выходного каскада. В этом соотношении транзистор остается до тех пор, пока на входе имеется сигнал.

Как показано выше, транзистор 2 может быть насыщен только тогда, когда заряжен конденсатор 5. Этот заряд сохраняется, если управляющий входной сигнал представляет собой разнополярные прямоугольные импульсы со скважностью, большей двух, с тем, чтобы большую часть периода входного сигнала транзистор 1 был закрыт, а меньшую часть периода транзистор 2 насыщался и давал возможность подзаряжаться конденсатору 5, запоминающему пиковое напряжение на сопротивлении нагрузки 7.

Поскольку при управлении выходным каскадом в одну сторону достаточно непрерывного входного сигнала и напряжение на сопротивлении нагрузки составляет половину напряжения источника питания двухтактного каскада, то при изменении полярности выходного напряжения на сопротивлении нагрузки 7 необходимо подавать прямоугольный временный сигнал со скважностью, большей двух. При этом вследствие прерывного цикла насыщений транзистора 2 среднее напряжение на сопротивлении нагрузки 7 меньше половины напряжения питания выходного каскада, т. е. возникает несимметрия схемы при различных полярностях выходного напряжения. Эта несимметрия легко устраняется подключением к схеме источника питания с соответствующей несимметрией напряжений питания относительно точки подключения сопротивления 7. Схема усилителя позволяет практически свести к нулю ток покоя транзистора / благодаря одинаковым потенциалам точек, между которыми подключено сопротивление нагрузки.

Предмет изобретения

Усилитель мощности по авт. св. № 258381, отличающийся тем, что, с целью расширения полосы пропускания усилителя и увеличения нагрузочной способности, между эмиттером транзистора динамической нагрузки и конденсатором, подключенным к месту соединения резистора и диода, включен резистор, а нагрузка подключена между эмиттером того же транзистора и средней точкой двух источников питания.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАСКАДНЫЙ ТРАНЗИСТОРНЫЙ УСИЛИТЕЛЬ | 2000 |

|

RU2183380C2 |

| Усилитель мощности | 1982 |

|

SU1050094A2 |

| Усилитель высокой частоты | 1989 |

|

SU1646045A1 |

| Транзисторный инвертор | 1990 |

|

SU1757069A1 |

| Усилитель | 1980 |

|

SU1107277A1 |

| Устройство защиты ключевого усилителя мощности | 1982 |

|

SU1078585A1 |

| Импульсный стабилизатор постоянного напряжения | 1990 |

|

SU1777129A1 |

| Усилитель мощности | 1980 |

|

SU930579A1 |

| УСИЛИТЕЛЬ МОЩНОСТИ ЗВУКОВОЙ ЧАСТОТЫ | 1993 |

|

RU2115224C1 |

| Каскодный усилитель | 1986 |

|

SU1425809A1 |

Даты

1972-01-01—Публикация