1

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении высоконадежных устройств.

Известный динамический элемент содержит две соединенных параллельно идентичных цепи, каждая из которых содержит диоды и резисторы входной логической схемы, запоминающий конденсатор, схему управления транзистором, инвертор и развязывающую схему, состоящую из трансформаторов, резисторов, и источников напряжения.

Однако в этом элементе короткое замыкание отдельных частей нарушает работоспособность всего элемента, короткое замыкание одного из диодов входной логической схемы снижает положительное напряжение на остальных его входах. Кроме того, схема очень сложна для реализации ее средствами микроэлектроники.

Устранение указанных недостатков в предлагаемом логическом элементе достигается с помощью поэлементного резервирования диодов входной логической схемы, подключения ее к источнику тактового питания через резервированные диоды. Причем развязывающая схема выполнена из последовательно соединенных конденсатора и диода, точка соединения которых через резистор подключена к источнику постоянного напряжения.

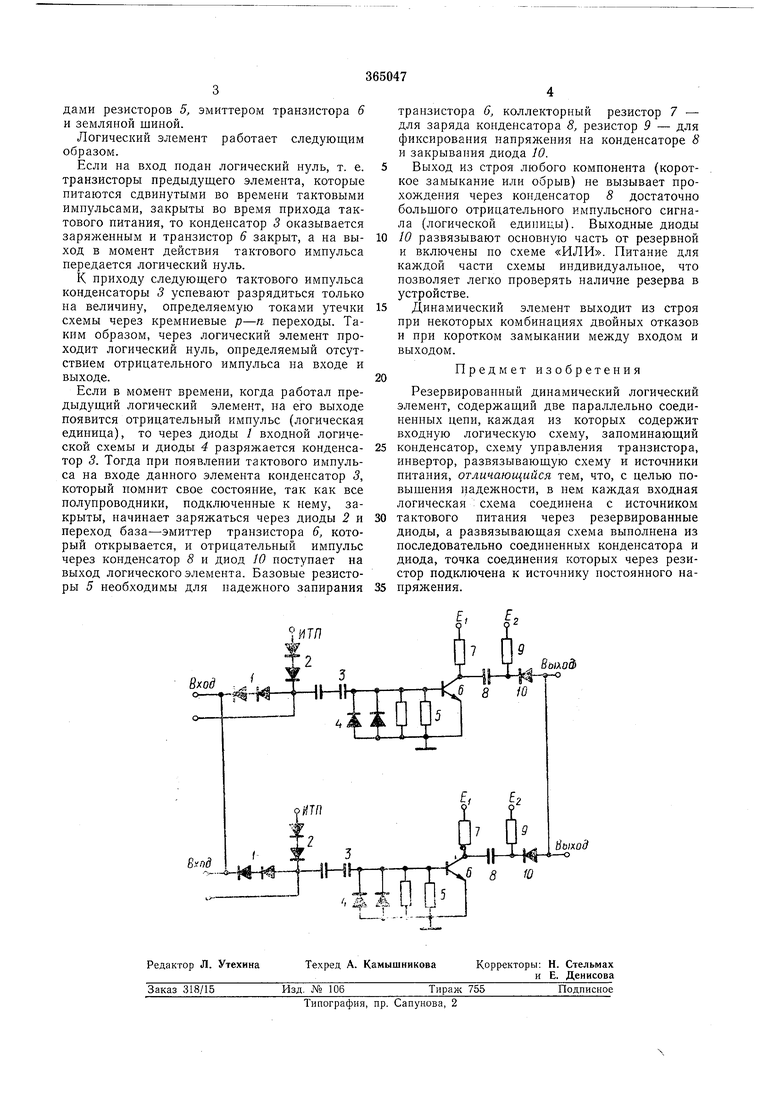

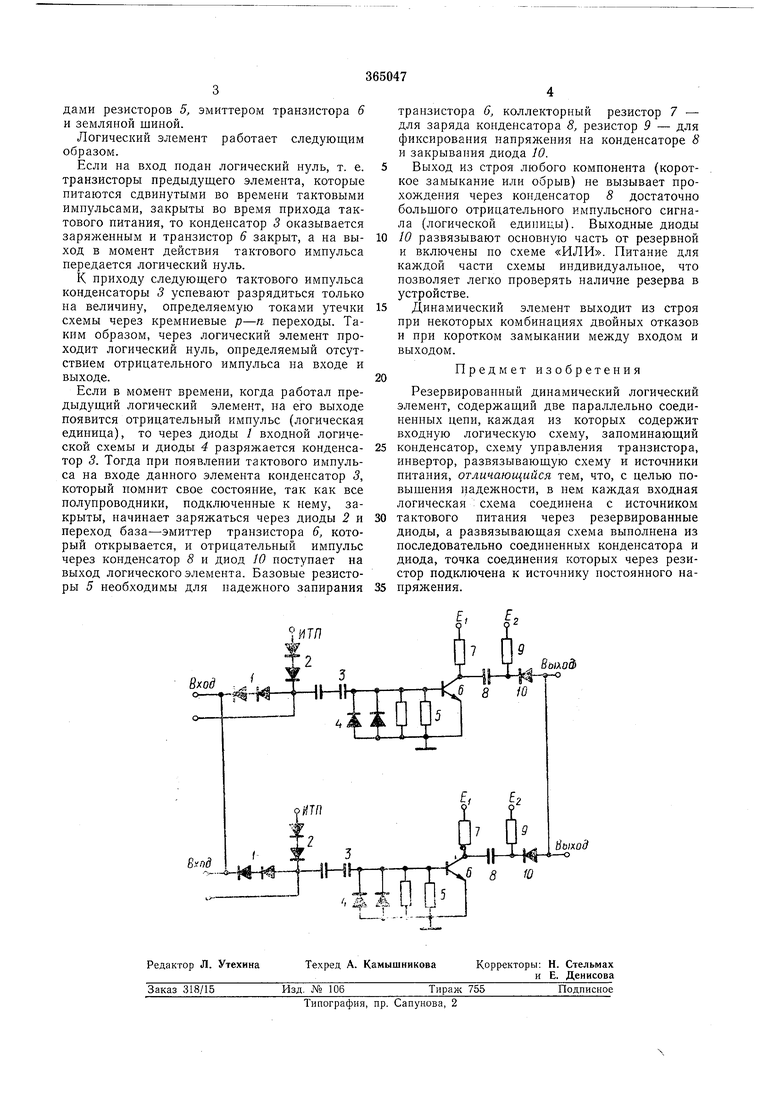

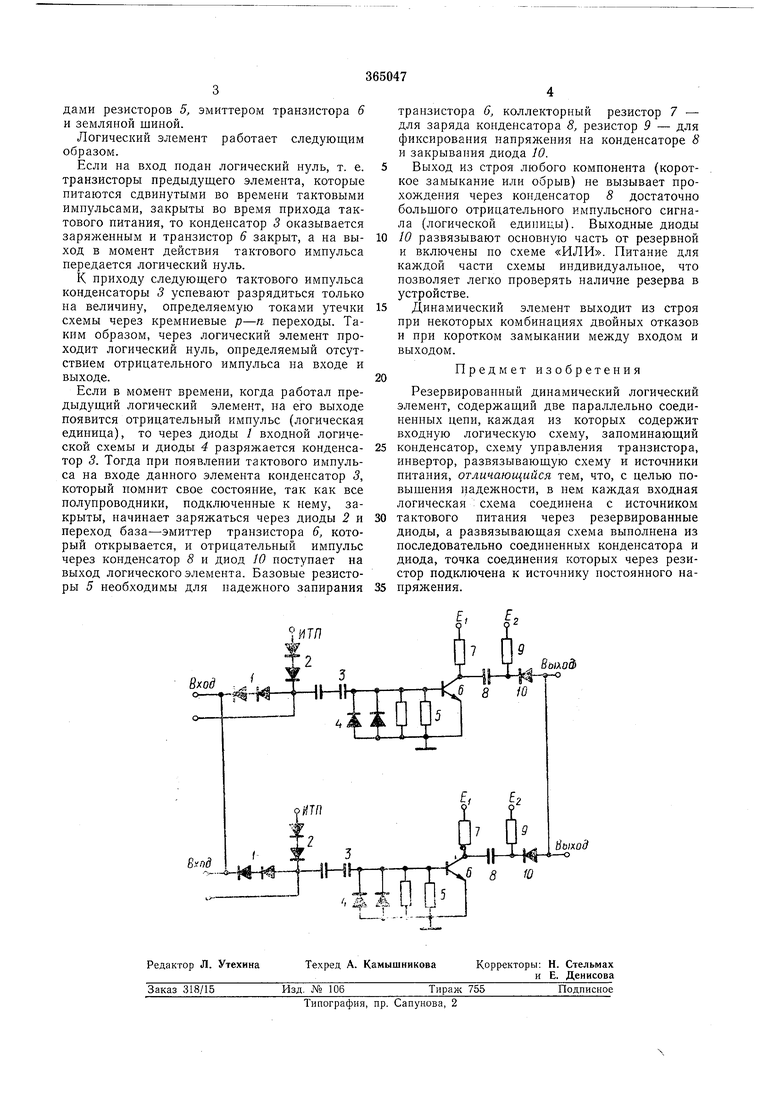

Принципиальная схема резервированного динамического логического элемента приведена на чертеже.

Элемент содержит диоды входной логической схемы /, диоды 2 тактового питания, запоминающие конденсаторы 3, фиксирующие диоды 4, базовые резисторы 5, транзисторы 6, коллекторные резисторы 7, развязывающие конденсаторы , резисторы смещения 9 и выходные развязывающие диоды 10.

Логический элемент состоит из двух одинаковых цепей, соединенных параллельно. Каждая цепь содержит входную логическую схему, построенную на диодах / и подключенную к диодам тактового питания 2 и запоминающим конденсаторам 3. Конденсатор 3 соединен со схемой управления транзистороминвертором 6, выполненной в виде фиксирующих диодов 4 и базовых резисторов 5, соединенных параллельно между собой и включенных в переход база-эмиттер. В коллектор транзистора 6 включен резистор 7 и развязывающий конденсатор 8, вторая обкладка которого подключена к резистору смещения 9 и

катоду выходного развязывающего диода 10, анод которого соединяется с выходом. При этом анод диода 2 соединен с шиной источника тактового питания ИТП, резисторы 7 и 5 подключены к постоянным источникам питания

EI, EZ, а аноды диодов 4 объединены с выводами резисторов 5, эмиттером транзистора 6 и земляной шиной.

Логический элемент работает следующим образом.

Если на вход подан логический нуль, т. е. транзисторы предыдущего элемента, которые питаются сдвинутыми во времени тактовыми импульсами, закрыты во время прихода тактового питания, то конденсатор 3 оказывается заряженным и транзистор 6 закрыт, а на выход в момент действия тактового импульса передается логический нуль.

К приходу следующего тактового импульса конденсаторы 3 успевают разрядиться только на величину, определяемую токами утечки схемы через кремниевые р-п переходы. Таким образом, через логический элемент проходит логический нуль, определяемый отсутствием отрицательного импульса па входе и выходе.

Если в момент времени, когда работал предыдущий логический элемент, па его выходе появится отрицательный импульс (логическая единица), то через диоды / входной логической схемы и диоды 4 разряжается конденсатор 3. Тогда при появлении тактового импульса на входе данного элемента конденсатор 3, который помнит свое состояние, так как все полупроводники, подключенные к нему, закрыты, начинает заряжаться через диоды 2 и переход база-эмиттер транзистора 6, который открывается, и отрицательный импульс через конденсатор 8 и диод 10 поступает на выход логического элемента. Базовые резисторы 5 необходимы для падежного запирания

транзистора 6, коллекторный резистор 7 - для заряда конденсатора 8, резистор 9 - для фиксирования напряжения на конденсаторе S и закрывания диода 10.

Выход из строя любого компонента (короткое замыкание или обрыв) не вызывает прохождения через конденсатор 8 достаточно большого отрицательного импульсного сигнала (логической единицы). Выходные диоды 10 развязывают основную часть от резервной и включены по схеме «ИЛИ. Питание для каждой части схемы индивидуальное, что позволяет легко проверять наличие резерва в устройстве.

Динамический элемент выходит из строя при некоторых комбинациях двойных отказов и при коротком замыкании между входом и выходом.

Предмет изобретения

Резервированный динамический логический элемент, содержащий две параллельно соединенных цепи, каждая из которых содержит входную логическую схему, запоминающий

конденсатор, схему управления транзистора, инвертор, развязывающую схему и источники питания, отличающийся тем, что, с целью повышения надежности, в нем каждая входная логическая схема соединена с источником

тактового питания через резервированные диоды, а развязывающая схема выполнена из последовательно соединенных конденсатора и диода, точка соединения которых через резистор подключена к источнику постоянного напряжения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированный мультивибратор | 1973 |

|

SU452911A1 |

| ТРАНЗИСТОРНЫЙ КЛЮЧ | 2005 |

|

RU2287219C1 |

| ПЕРЕКЛЮЧАТЕЛЬ УКАЗАТЕЛЕЙ ПОВОРОТА | 1993 |

|

RU2092340C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1991 |

|

RU2009612C1 |

| БЕЗОПАСНАЯ СХЕМА "2И" | 2008 |

|

RU2370395C1 |

| Устройство электронной защиты | 1980 |

|

SU974358A1 |

| Стабилизатор постоянного напряжения | 1985 |

|

SU1273903A1 |

| Стабилизатор напряжения | 1989 |

|

SU1700546A1 |

| Преобразователь напряжения | 1983 |

|

SU1136278A1 |

| Устройство для защиты от перегрузок по току силового транзистора регулирующего элемента | 1978 |

|

SU752602A1 |

Даты

1973-01-01—Публикация