1

В основном авт. св. № 311359 онисаи автоматический регулятор возбуждения, содержащий аналоговое устройство, обеспечивающее регулирование по отклоиению контролируемого параметра и импульсно-цифровое устройство с блоком формирования обобщенного параметра регулирования, при этом блок формирования обобщенного параметра подключен к цифровому дифференциатору, циклически определяющему приращение обобщениого ларам-етра за пе1риод дискретности, а выход последнего через расширитель длительности временного интервала соединен с блоком преобразования длительности импульсов в управляющее напряж ение.

Указанный автоматический регулятор снабжен узлом контроля, включенным одежду цифровым дифференцнатором и расщирителем длительности временного интервала и состоящим из ограничителя длительности и логической схемы, вырабатывающей сигнал несоответствия параметра стабилизации физически возможному, а также узлом блокировки, включенным на выходе регулятор а, состоящим из апериодического звена с большой ностоянной времени, воздействующего на релейный элемент, от1ключающим импульсно-цифровое устройство.

Цель изофетения - упрощение устройства.

Эта цель достигнута в результате того, что

выход логической схемы контроля подключен через цепи сб;роса к цифровому дифференциатору и расширителю длительности временного интервала.

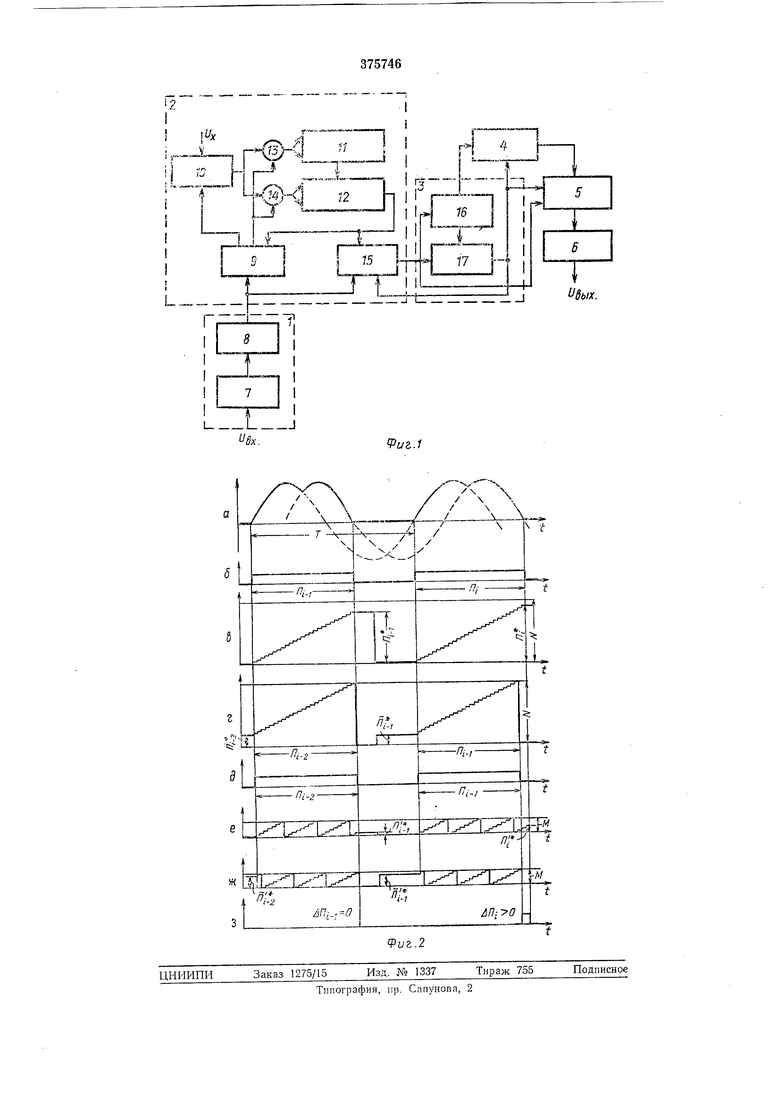

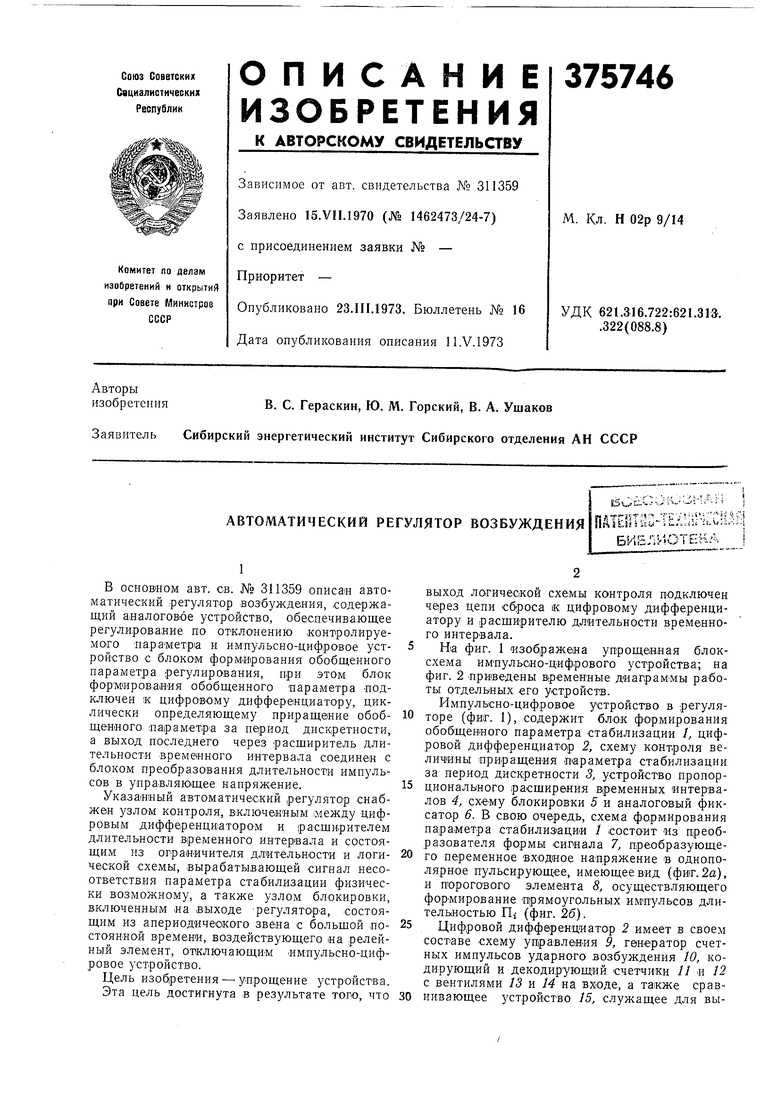

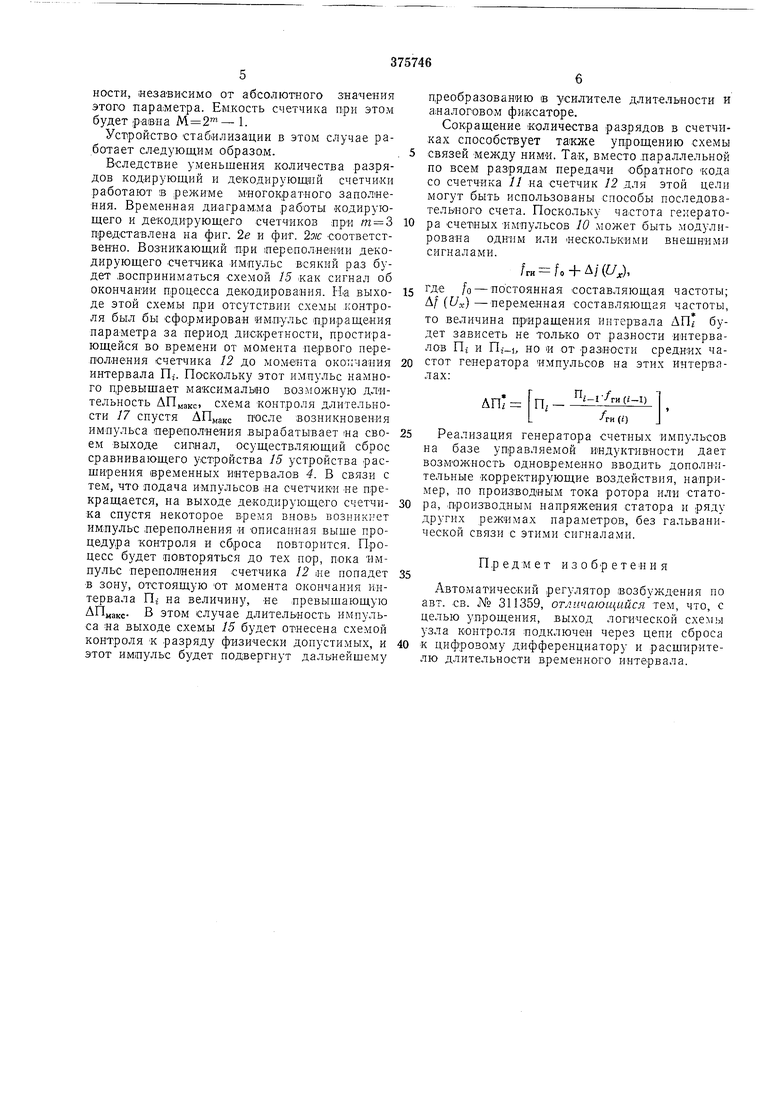

На фиг. 1 изображена упрощенная блоксхема импульсно-цифрового устройства; на фиг. 2 приведены временные диаграммы работы отдельных его устройств.

Импульсно-цифровое устройство в регуляторе (фиг. 1), содержит блок формирования обобщенного параметра стабилизации 1, цифровой дифференциатор 2, схему контроля величины приращения параметра стабилизации за период дискретности 3, устройство пропорционального расширения временных интервалов 4, схему блокировки 5 и аналоговый фиксатор 6. В свою очередь, схема формирования параметра стабилизации 1 состоит из преобразователя формы сигнала 7, преобразующего переменное входное напряжение в однополярное пульсирующее, имеющее вид (фиг. 2а), и порогового элемента 8, осуществляющего формирование прямоугольных импульсов длительностью Пг (фиг. 26).

Цифровой дифференциатор 2 имеет в своем составе схему управления 9, генератор счетных импульсов ударного возбуждения 10, кодирующий и декодирующий счетчики 11 н 12 с вентилями 13 и 14 на входе, а также сравнивающее устройство 15, служащее для выявления величины приращения интервала Пг за период дискретности (в лрототипе данная схема названа схемой несовпадения). Выход этой схемы соединен со входом схемы контроля 3, включающей в себя ограничитель длительности интервалов 16 и логическую схему К1онт роля длительности 17. Выход ограничителя длительности 16 соединен с устройством расширения временных интервалов 4, реализованного по известному принципу заряда разряда .кояденсатор а с различными скоростями. Выходной каскад усилителя длительности, выполненный в виде триггера Шмитта, через схему блокировки 5 соединен со входом аналогового фиксатора 6, -представляющего собой совокупность апериодических фиксаторов сз аданными динамическими свойствами.

Выход логической схемы контроля длительности 17 через цепи сброса соединен с усилИгелем длительности 4 и сравнивающим устройством /5; в свою очередь, выход схемы 15 заведен на вход схемы блокировки 5. Введение изменений по двум последним пунктам позволяет значительно сократить разрядность кодирующего и декодирующего счетчиков.

Уст;ройства стабилизации работает следующим образом.

Схема формирования параметра стабилизации 1 вырабатывает в каждом цикле работы регулятора прямоугольный импульс Пг (фиг. 26). В течение длительности интервала rii в кодирующий счетчик // поступают импулвсы генератора 10. Если разрядность счетчиков 11 и 12 выбрана исходя из максимально возможной величины интервала П„акс и частоты генератора fraMaKc (Как это было выполнено в Прототипе), т. е.

(Пмакс f гимакс).

ТО В счетчике 11 образуется код П (фиг. 2в). Емкость счетчиков при этом будет равна .

Од/новременно с началом кодирования интервала Пг в декодирующем счетчике 12 начикается преобразование полученного в предшествующем цикле кода во временной интервал Пг-i (фиг. 2г). Для этого перед началом декодирования в счетчик 12 заносится обратный «од и счетчик заполняется импульсами генератора до появления импульса переполнения. И-мпульс переполнения декодирую-щего счетчика -поступает в схему 15 и используется для формирования заднего фронта прямоугольяого имиульса Пг-i (фиг. 2(3). В результате сравнения интервалов П, и П,сравнивающее устройство 15 вырабатывает короткий прямоугольный импульс, длительность которого равна квантованному значенйю разности текущего и предшествующего интервалов:

дп: (п, - Ui-ir,

Этот импульс (фиг. 2з) поступает на входы огоаиичителя длительности 16, логической

схемы контроля длительности 17 и схемы блокировки 5.

С выхода ограничителя длительности 16 импульс ЛПг поступает на входы расширителя длительности 4 и логической схемы контроля длительности 17. Схема контроля 3 работает следующим образом. Бели длительность импульса АП не превышает физически возможную величину АПмакс. которая заранее устанавливается в схеме ограничителя длительности исходя из априорных сведений о максимальной скорости изменения параметра стабилизации з-а период дискретности Г, то импульс на входе и выходе схемы 16 имеет одинаковую длительность и блокирующий сигнал на выходе схемы контроля длительности 17 отсутствует. В этом случае имлульс удлиняется схемой 4 и беспрепятственно проходит через схему блокировки 5 на аналоговый фиксатор 6. Схема блокировки служит для предотвращения прохождения сигнала с усилителя длительности на аналоговый фиксатор в случае, если

ЛП ДП„акс,

Т. е. при возникновении отказов или сбоев.

Запрещак щим сигналом при этом является сигнал с выхода схемы контроля длительности 17. Поскольку запрещающий сигнал формируется с задержкой на ДПмакс относительно

момента вознииновения сигнала ДПг, то для предотвращения возможности прохождения на анологовый фиксатор даже коротких импульсов ДПг, последние с выхода схемы 15 заведены на второй запрещающий вход схемы блокировки. С учетом действия этой связи (и при отсутствии запрещающего сигнала с выхода схемы 17) результирующая длительность широтного сигнала, поступающего на аналоговый фиксатор 6 составляет

т ()Ап,

где & -коэффициент усиления длительности, имеющий для данного регулятора величину порядка 100-150.

Широтный сигнал в аналоговом фиксаторе с учетом знака ДПг преобразуется в напряжение /вых.

Работа схемы устройства стабилизации Рассматривалась ранее в предположении, что разрядность счетчиков 11 и 12 достаточна для кодирования максимально возможных интервалов Пмакс- Однако введение дополнительных связей со схемы контроля на цифровой дефференциатор и усилитель длительности позволяет сократить разрядность счетчиков примерно до значения

т log, (2fl ДП„акс/гв макс),

где т - количество разрядов в счетчиках, Т) (l,5s-2 - коэффициент запаса, т. е. в предлагаемом регуляторе разрядность цифрового дифференциатора может быть выбрана, исходя лищь из величины максимально возможного приращения параметра за период дискретности, независимо от абсолютного значения этого параметра. Емкость счетчика при этом будет р-авна 1.

Устройство стабилизации в этом случае работает следующим образом.

Вследствие уменьшения количества разрядов кодирующий и декодирующий счетчики работают в режиме мяогократного заполиения. Временная ди-аграмма работы кодирующего и декодирующего счетчиков при т 3 представлена на фиг. 2е и фиг. 2ж соответственно. ВозниКающий при переполнении декодирующего счетчика импульс всякий раз будет восприниматься схемой 15 как сигнал об окончании процесса декодирования, fla выходе этой схемы при отсутствии схемы .контроля был бы сформирован приращения параметра за период дискретности, простирающейся во времени от момента первого переполнения счетчика 12 до окончания интервала Dj. Поскольку этот импульс намного превышает максимально возможную длительность ДП„акс) схема контроля длительности /7 спустя АПмакс после возникновения импульса переполнения вырабатывает на своем выходе сипнал, осуществляющий сброс сравнивающего устройства 15 устройства расширения 1временных интервалов 4. В связи с тем, что подача импульсов на счетчики не прекращается, на выходе декодирующего счетчика спустя некоторое время вновь возникнет импульс переполнения « описанная выше процедура контроля и сброса повторится. Процесс будет повторяться до тех пор, пока импульс перепол1нения счетчика 12 1не попадет в зону, отстоящую от момента окончания интервала Пг на величину, не превышающую

АП.

В этом случае длительность импульса на выходе схемы 15 будет отнесена схемой контроля К разряду физически допустимых, и этот импульс будет подвергнут дальнейшему

преобразованию в усилителе длительности и аналоговом фиксаторе.

Сокращение количества разрядов в счетчиках способствует также упрощению схемы связей между ними. Так, вместо параллельной по всем разрядам передачи обратного кода со счетчйка // на счетчик 12 для этой цели могут быть использованы способы последовательного счета. Поскольку частота генератора счетных -импульсов 10 может быть модулирована одннм или несколькими внешними сигналами.

+ А/(х),

где /о - постоянная составляющая частоты; А/ Ux -переменная составляющая частоты, то величина приращения интервала АПг будет зависеть не только от разности интервалов Пг и но и ОТ разности средних частот генератора импульсов на этих интервалах:

i-l Ли (t-I)

ДП/ г П, /ги (О

Реализация генератора счетных импульсов на базе управляемой индуктивности дает возможность одновременно вводить дополнительные корректирующие воздействия, например, по производным тока ротора или статора, производным напряжепия статора и ряду других режимах параметров, без гальванической связи с этими сигналами.

П р е д :м е т изобретения

Автоматический регулятор возбуждения по авт. св. № 311359, отличающийся тем, что, с целью упрощения, выход логической схемы узла контроля подключен через цепи сброса к цифровому дифференциатору и расширителю длительности временного интервала.

| название | год | авторы | номер документа |

|---|---|---|---|

| АВТОМАТИЧЕСКИЙ РЕГУЛЯТОР ВОЗБУЖДЕНИЯ | 1971 |

|

SU311359A1 |

| Устройство для прогнозирования выбросов металла и шлака из конвертера | 1984 |

|

SU1250580A1 |

| Акустический анализатор состава | 1984 |

|

SU1245993A1 |

| Устройство управления углом опережения зажигания двигателя внутреннего сгорания | 1986 |

|

SU1381536A1 |

| Устройство для цифровой обработки аналогового сигнала | 1986 |

|

SU1332335A1 |

| СПОСОБ ВЫДЕЛЕНИЯ КОМАНД И УСТРОЙСТВО ВЫДЕЛЕНИЯ КОМАНД | 2004 |

|

RU2276462C1 |

| ОПТИЧЕСКИЙ РЕФЛЕКТОМЕТР | 2002 |

|

RU2214583C1 |

| Способ определения частотной характеристики испытуемого объекта и устройство для его осуществления | 1984 |

|

SU1223074A1 |

| Устройство прогнозирования выбросов металла и шлака из конвертора | 1984 |

|

SU1225859A1 |

| Устройство для дискретного регулирования мощности | 1991 |

|

SU1833957A1 |

Даты

1973-01-01—Публикация