il

Изобретение относится к устройствам для задержки аналогового сигнала и может найти применение при создании специализировапных блоков аналоговых вычислительных устройств.

Известны устройства регулируемого запаздывания аналоговых сигналов, преобразованных в широтно-импульсную форму, содержащие дифференциальную цепочку, связанную с разделительными диодами, параллельно соединенные одновибраторы, генератор, управляемый одновибраторами, и триггеры с системой схем совпадения.

Однако в известных устройствах тактовые и измерительные фронты широтно-модулированных сигналов распространяются каждый по своему отдельному каналу, причем задержка каждого отдельного фронта задается отдельным одновибратором. При такой системе образования задержек возникают погрешности, связанные с неидентичностью интервалов задержек, вырабатываемых различными одновибраторамн. Кроме того, в известных устройствах имеется только один интервал задержки, на который может быть отрегулировано устройство.

С целью повышения точности и упрощения регулировки времени задержки в предлагаемом устройстве входы интеграторов через ключи записи и блок размножения сигнала

е

соединены с источником аналогового сигнала, а через ключи считывания - с источником напряжения считывания; ключи записи и ключи считывания через соответствующие коммутаторы записи и считывания и ключи, управляемые триггерами записи и считывания соответственно, подключены к генератору тактовых импульсов, причем триггер записи соединен с источником сигнала запуска

непосредственно, а триггер считывания - через элемент регулируемой задержки, а выходы интеграторов через сумматор и триггер Шмидта соединены с выходом устройства.

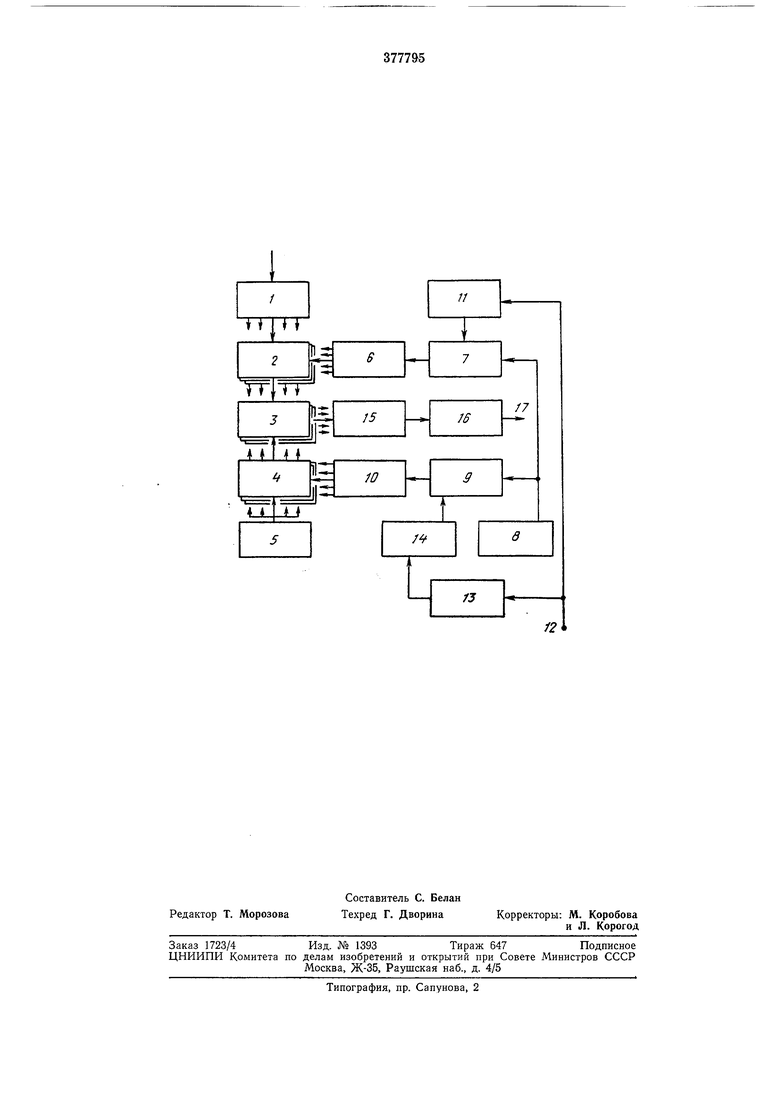

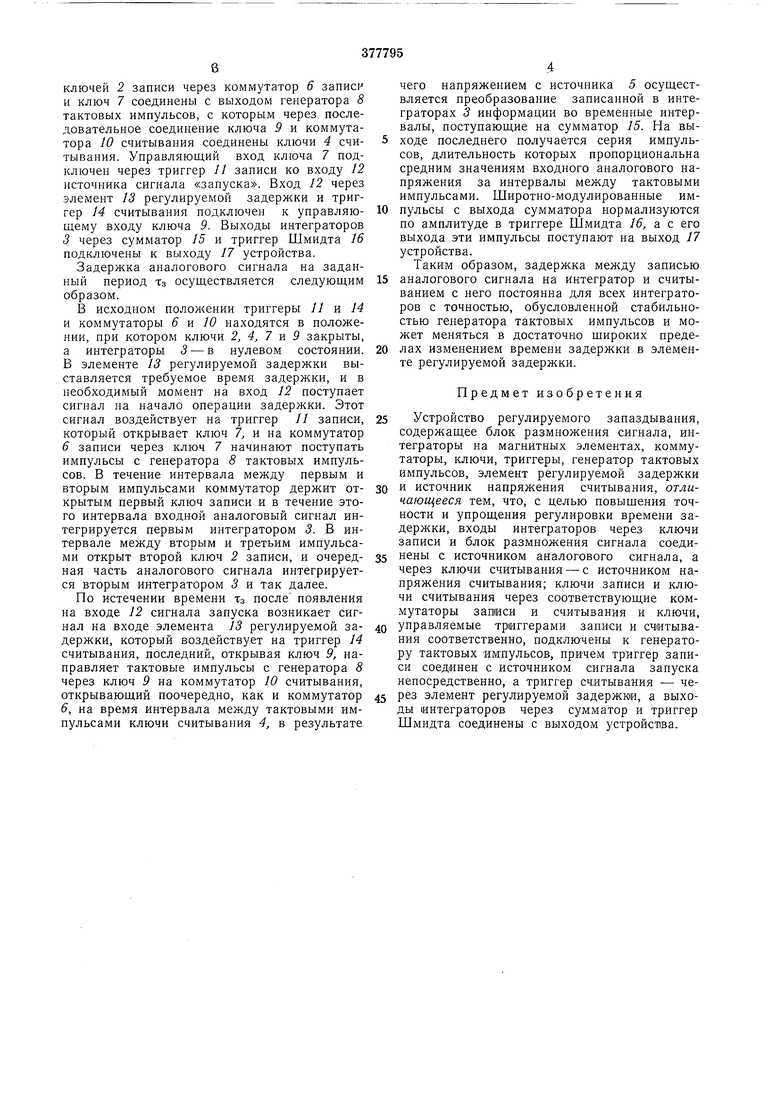

На чертеже дана функциональная схема предлагаемого устройства.

Устройство содержит блок / размножения сигнала, на вход которого поступает задерл иваемый аналоговый сигнал, разделяющийся затем на п аналогичных сигналов без изменения мгновенных значений. Каждый из сигналов ноступает на выход блока У, последний подключен к потенциальному входу ключа 2 записи, выходы ключей 2 подключены, в свою очередь, ко входам интеграторов 3 на магнитных элементах с прямоугольной петлей гистерезиса. К другим входам интеграторов 3 через ключи считывания 4 подключен источник 5 постоянного напряжения считывания бсч- Управляющие входы

ключей 2 записи через коммутатор 6 записи и ключ 7 соедииены с выходом генератора 8 тактовых импульсов, с которым через последовательное соединение ключа 9 и коммутатора 10 считывания соединены ключи 4 считывания. Управляющий вход ключа 7 подключен через триггер // записи ко входу 12 источника сигнала «запуска. Вход 12 через элемент 13 регулируемой задержки и триггер 14 считывания подключен к управляющему входу ключа 9. Выходы интеграторов 3 через сумматор 15 и триггер Шмидта 16 подключены к выходу 17 устройства.

Задержка аналогового сигнала на заданный период тз осуществляется следующим образом.

В исходном положении триггеры 11 и 14 и коммутаторы 6 и 10 находятся в положении, при котором ключи 2, 4, 7 и 9 закрыты, а интеграторы 3 - в нулевом состоянии. В элементе 13 регулируемой задержки выставляется требуемое время задержки, и в необходимый момент на вход 12 поступает сигнал на начало операции задержки. Этот сигнал воздействует на триггер // записи, который открывает ключ 7, и на коммутатор 6 записи через ключ 7 начинают поступать импульсы с генератора 8 тактовых импульсов. В течение интервала между первым и вторым импульсами коммутатор держит открытым первый ключ записи и в течение этого интервала входной аналоговый сигнал интегрируется первым интегратором 3. В интервале между вторым и третьим импульсами открыт второй ключ 2 записи, и очередная часть аналогового сигнала интегрируется вторым интегратором 3 и так далее.

По истечении времени Тз после появления на входе 12 сигнала запуска возникает сигнал на входе элемента 13 регулируемой задержки, который воздействует на триггер 14 считывания, последний, открывая ключ 9, направляет тактовые импульсы с генератора 8 через ключ 9 на коммутатор 10 считывания, открывающий поочередно, как и коммутатор 6, на время интервала между тактовыми импульсами ключи считывания 4, в результате

чего напряжением с источника 5 осуществляется преобразование записанной в интеграторах 3 информации во временные интервалы, поступающие на сумматор 15. На выходе последнего получается серия импульсов, длительность которых пропорциональна средним значениям входного аналогового напряжения за интервалы между тактовыми импульсами. Широтно-модулированные импульсы с выхода сумматора нормализуются

по амплитуде в триггере Шмидта 16, а с его

выхода эти импульсы поступают на выход 17

устройства.

Таким образом, задержка между записью

аналогового сигнала на интегратор и считыванием с него постоянна для всех интеграторов с точностью, обусловленной стабильностью генератора тактовых импульсов и может меняться в достаточно щироких пределах изменением времени задержки в элементе регулируемой задержки.

Предмет изобретения

Устройство регулируемого запаздывания, содержащее блок размножения сигнала, интеграторы на магнитных элементах, коммутаторы, ключи, триггеры, генератор тактовых импульсов, элемент регулируемой задержки

и источник напряжения считывания, отличающееся тем, что, с целью повыщения точности и упрощения регулировки времени задержки, входы интеграторов через ключи записи и блок размножения сигнала соедийены с источником аналогового сигнала, а через ключи считывания - с источником напряжения считывания; ключи записи и ключи считывания через соответствующие коммутаторы записи и считывания и ключи,

управляемые триггерами записи и считывания соответственно, подключены к генератору тактовых импульсов, причем триггер записи соединен с источником сигнала запуска непосредственно, а триггер считывания - через элемент регулируемой задержки, а выходы интеграторов через сумматор и триггер Шмидта соединены с выходом устройстаа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задержки аналогового сигнала | 1973 |

|

SU443471A1 |

| Система управления | 1983 |

|

SU1168896A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки (ЭЛТ) | 1988 |

|

SU1509862A1 |

| Статистический анализатор конечной разности фазы | 1987 |

|

SU1422182A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ОБЪЕМНОГО РАСХОДА ВЕЩЕСТВ С ПОМОЩЬЮ УЛЬТРАЗВУКОВЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1999 |

|

RU2169906C2 |

| Устройство для контроля физико-механических свойств материалов | 1985 |

|

SU1536301A1 |

| Преобразователь интервала времени в код | 1990 |

|

SU1830622A1 |

| Устройство для определения характеристик фотографических систем | 1988 |

|

SU1566381A1 |

| Устройство для синхронизации шумоподобных сигналов | 1982 |

|

SU1022326A1 |

| Устройство для контроля качества ферромагнитных изделий | 1987 |

|

SU1499212A1 |

Авторы

Даты

1973-01-01—Публикация