1

Изобретение относится к вычислительной технике и может найти применение в релейноимпульсных системах автоматического управления различными технологическими процессами для построения релейно-импульсных систем управления в качестве блоков запаздывающей отрицательной обратной связи, а также блоков с регулируемой выдержкой времени.

Известны устройства для регулирования задержки входного сигнала, содержащие времязадающий конденсатор, переключающую схему, резисторы и диоды.

С целью повышения надежности работы в предлагаемом устройстве переключающая схема выполнена на транзисторах, причем времязадающий конденсатор подключен через первый и второй диоды к коллекторам первых двух транзисторов, база первого транзистора подключена к источнику сигнала, база второго транзистора через резистор и третий диод подключена к коллектору первого транзистора, базы третьего и четвертого транзисторов через соответствующие развязывающие диоды подключены к обеим обкладкам времязадающего конденсатора, а коллекторы третьего и четвертого транзисторов подключены соответственно к эмиттеру и базе пятого транзистора, коллектор которого через резистор подключен к шине питания.

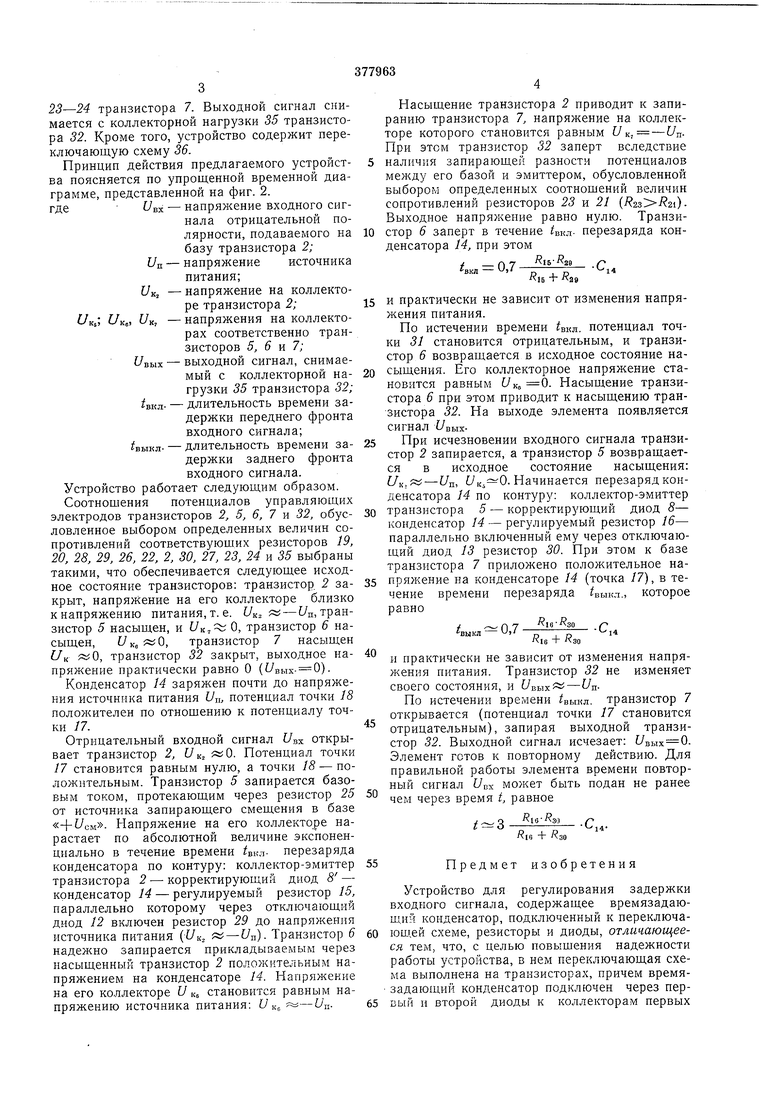

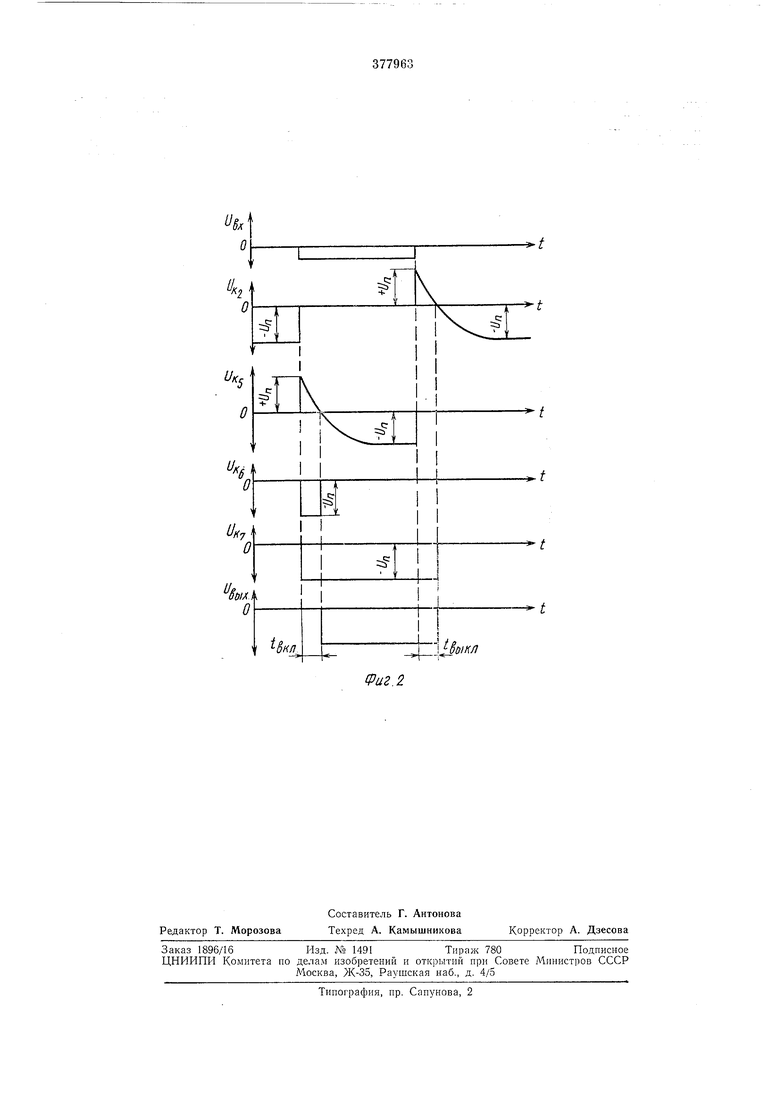

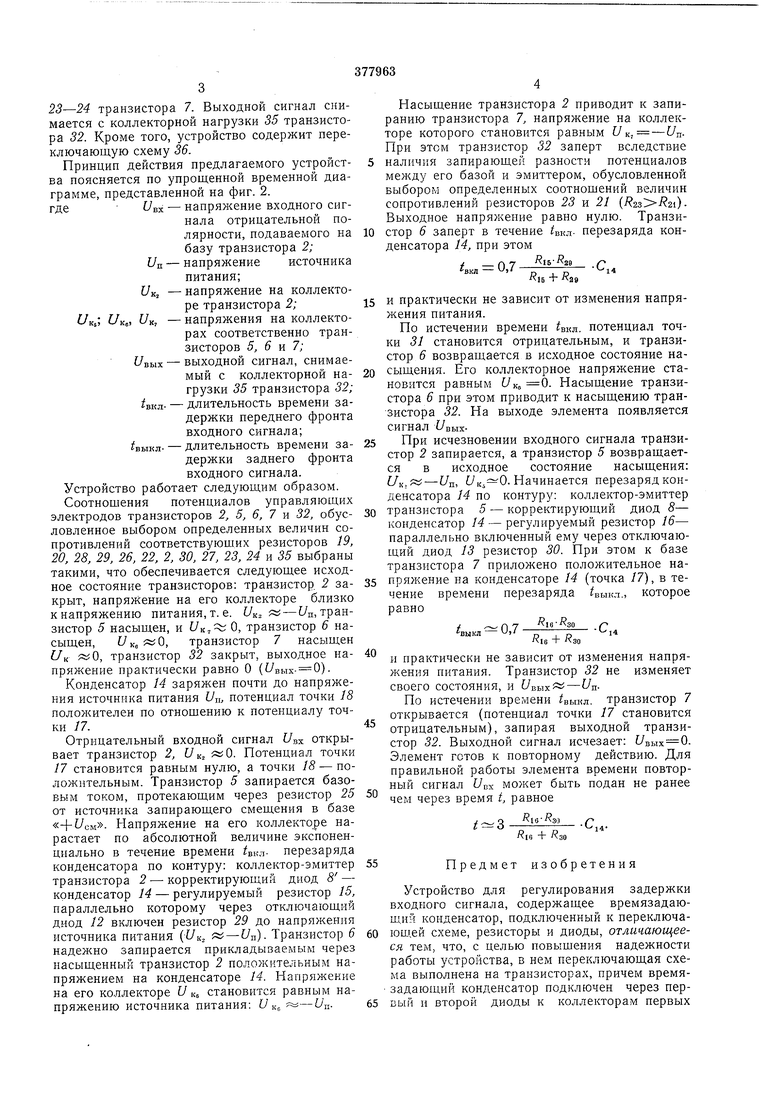

На фиг. 1 представлена принципиальная электрическая схема предлагаемого устройства; на фиг. 2 - времеиная диаграмма.

Предлагаемое устройство состоит из входного каскада 1, содержащего логический элемент типа «ИЛИ - НЕ на транзисторе 2 с запуском на базу и резистор 5 для запуска схемы на коллектор, каскад временной задержки 4, содержащий транзисторы 5-7, с корректирующими и отключающими диодами 8, 8-13 соответственно, времязадающий конденсатор 14, включенный между регулируемыми резисторами 15 и 16 перезарядных контуров (точки 17 и 18), раздельные от контуров перезаряда коллекторные нагрузки 19 и 20 первых двух транзисторов 2 и 5, коллекторные нагрузки 21-24 транзисторов 6 и 7, представляющие собой делители, составленные из низкоомных резисторов 2} и 23 и высокоомных резисторов 22 и 24, резисторов 25, 26 и 27, подключенных к источнику запирающего смещения в базах , резисторов 28, 29 и 30, образующих с резисторами 25, 26 и 27 базовые делители, определяющие исходные режимы транзисторов 5, б и 7.

Выходной каскад 31 выполнен на транзисторе 32 обратной проводимости по схеме ключа-звезды с общим эмиттером, база которого подключена к общей точке 33 делителя 21 и 22, а эмиттер - к общей точке 34 делителя

23-24 транзистора 7. Выходной сигнал снимается с коллекторной нагрузки 35 транзистора 32. Кроме того, устройство содержит переключающую схему 36.

Принцип действия предлагаемого устройства поясняется по упрощенной временной диаграмме, представленной на фиг. 2. где t/Bx - напряжение входного сигнала отрицательной полярности, подаваемого на базу транзистора 2; Un - напряжение источника

питания;

VK, - напряжение на коллекторе транзистора 2;

UK,, f/Ko, UK, - напряжения на коллекторах соответственно транзисторов 5, 6 и 7; -выходной сигнал, снимаемый с коллекторной нагрузки 35 транзистора 52; вкл- - длительность времени задержки переднего фронта входного сигнала; г выкл- - длительность времени задержки заднего фронта входного сигнала.

Устройство работает следующим образом. Соотнощения потенциалов управляющих электродов транзисторов 2, 5, 6, 7 и 32, обусловленное выбором определенных величин сопротивлений соответствующих резисторов 19, 20, 28, 29, 26, 22, 2, 30, 27, 23, 24 и 35 выбраны такими, что обеспечивается следующее исходное состояние транзисторов: транзистор 2 закрыт, напряжение на его коллекторе близко к напряжению питания, т.е. (Ук - t/n, транзистор 5 насыщен, и t/к, О, транзистор 6 насыщен, /7к„; 0, транзистор 7 насыщен UK , транзистор 32 закрыт, выходное напряжение практически равно О (/вых- 0).

Конденсатор 14 заряжен почти до напряжения источника питания t/ш потенциал точки 18 положителен по отнощению к потенциалу точки 17.

Отрицательный входной сигнал f/sx открывает транзистор 2, U кг . Потенциал точки 17 становится равным нулю, а точки 18 - положительным. Транзистор 5 запирается базовым током, протекающим через резистор 25 от источника запирающего смещения в базе . Папряжение на его коллекторе нарастает по абсолютной величине экспоненциально в течение времени вкл- перезаряда конденсатора по контуру: коллектор-эмиттер транзистора 2 - корректирующий диод 8 - конденсатор 14 - регулируемый резистор 15, параллельно которому через отключающий диод 12 включен резистор 29 до напряжения источника питания (t/к.. к - t/n). Транзистор 6 надежно запирается прикладываемым через насыщенный транзистор 2 положительным напряжением на конденсаторе 14. Напряжение на его коллекторе U к становится равным напряжению источника питания: U к « -U Насыщение транзистора 2 приводит к запиранию транзистора 7, напряжение на коллекторе которого становится равным f/к, - f/nПри этом транзистор 32 заперт вследствие

5 наличия запирающей разности потенциалов между его базой и эмиттером, обусловленной выбором определенных соотнощений величин сопротивлений резисторов 23 и 21 (). Выходное напряжение равно нулю. Транзистор 6 заперт в течение вкд. перезаряда конденсатора 14, при этом

/ П 7

«вкл - и,/ -t-M

16 +

5 И Практически не зависит от изменения напряжения питания.

По истечении времени вкл. потенциал точки 31 становится отрицательным, и транзистор 6 возвращается в исходное состояние насыщения. Его коллекторное напряжение становится равным С/к„ 0. Насыщение транзистора б при этом приводит к насыщению транзистора 32. На выходе элемента появляется сигнал 1/вых5 При исчезновении входного сигнала транзистор 2 запирается, а транзистор 5 возвращается в исходное состояние насыщения: f/K,K-Uji, . Начинается перезаряд конденсатора 14 по контуру: коллектор-эмиттер

0 транзистора 5 - корректирующий диод 8- конденсатор 14 - регулируемый резистор 16- параллельно включенный ему через отключающий диод 13 резистор 30. При этом к базе транзистора 7 приложено положительное напряжение на конденсаторе 14 (точка 17), в течение времени перезаряда выкл., которое равно

RisRso

-С

14

16 + 30

и практически не зависит от изменения напряжения питания. Транзистор 32 не изменяет

своего состояния, и /вых - пПо истечении времени выкл. транзистор 7 открывается (потенциал точки 17 становится отрицательным), запирая выходной транзистор 32. Выходной сигнал исчезает: . Элемент готов к повторному действию. Для правильной работы элемента времени повторный сигнал f/Bx может быть подан не ранее чем через время t, равное

-Rio ao

С

10 + 30

предмет изобретения

Устройство для регулирования задержки входного сигнала, содержащее времязадаюш,ий конденсатор, подключенный к переключа60 ющей схеме, резисторы и диоды, отличающееся тем, что, с целью повыщения надежности работы устройства, в нем переключающая схема выполнена на транзисторах, причем время задающий конденсатор подключен через пер65 вый и второй диоды к коллекторам первых

двух транзисторов, база первого транзистора подключена к источнику сигнала, база второго транзистора через резистор и третий диод подключена к коллектору первого транзистора, базы третьего и четвертого транзисторов через соответствующие развязывающие диоды

подключены к обеим обкладкам времязадающего конденсатора, а коллекторы третьего и четвертого транзисторов подключены соответственно к эмиттеру и базе пятого транзистора, коллектор которого через резистор подключен к шине питания.

%

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь постоянного напряжения | 1979 |

|

SU862341A1 |

| Формирователь импульсов | 1977 |

|

SU692071A2 |

| Генератор импульсов | 1973 |

|

SU487448A1 |

| Однотактный преобразователь постоянного напряжения | 1989 |

|

SU1661938A1 |

| Генератор импульсов | 1980 |

|

SU917305A1 |

| Полупроводниковое реле времени | 1979 |

|

SU860310A1 |

| Преобразователь постоянного напряжения | 1987 |

|

SU1444921A1 |

| Ячейка временной задержки импульсов | 1980 |

|

SU945967A1 |

| Блокинг-генератор | 1979 |

|

SU818434A1 |

| Одновибратор | 1978 |

|

SU733088A1 |

Авторы

Даты

1973-01-01—Публикация