1

Изобретение относится к области телемеханики.

Известны устройства для обнаружения ошибок декодированной информации, содержащие дешифратор, схему совпадения и формирования управляющего сигнала ошибки, триггеры, эмиттерные повторители, усилителиинверторы и блок преобразования и записи информации.

Целью изобретения является упрощение устройства и повыщение его надежиости в работе.

Для этого в предложенное устройство введены схемы «ИЛИ - «НЕ, .причем входы первых двух схем лодсоединены ко входам дешифратора и через эмиттерные повторители - к одним из входов блока преобразования и записи информации, а выходы к одним из входов триггеров, другие входы которых подключены к выходу третьей схемы «ИЛИ - «НЕ, входы которой подключены к выходам дешифратора, а выходы триггеров через соответствующие усилителиинверторы подсоединены ко входам схемы совпадения и формирования управляющего сигнала ощибки, выход которой подключен к другому входу блока преобразования и записи информации.

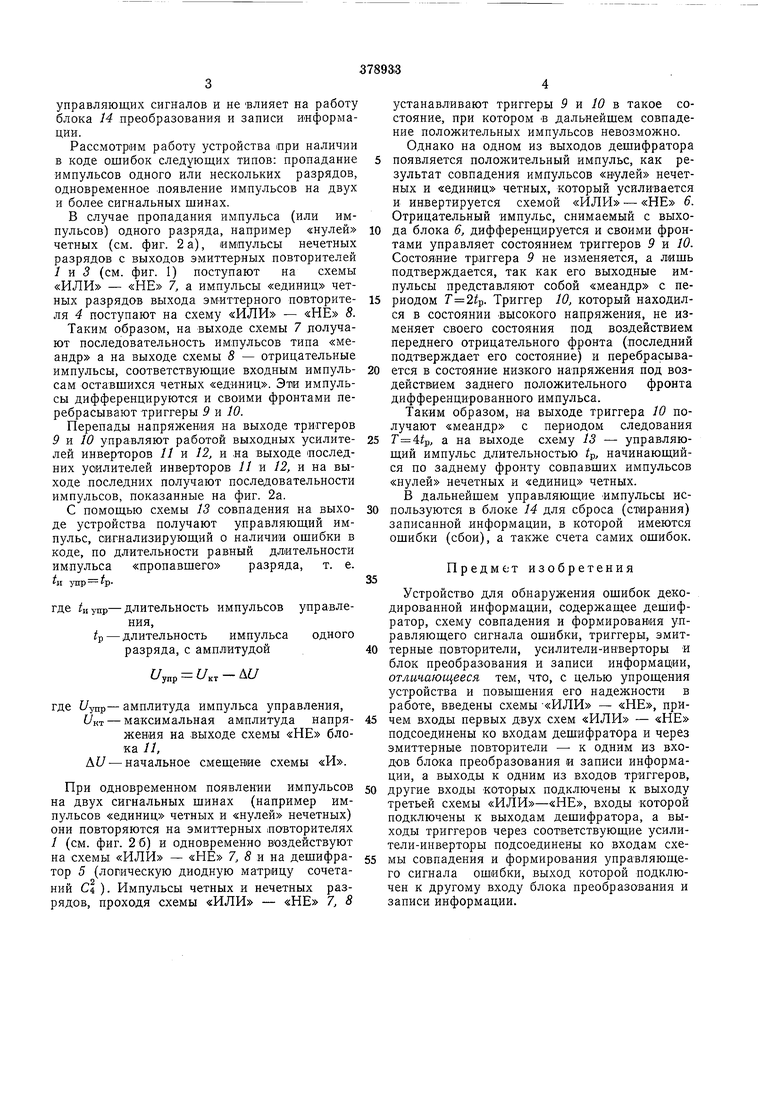

На фиг. 1 представлена блок-схема предложенного устройства, содержащая эмиттерные

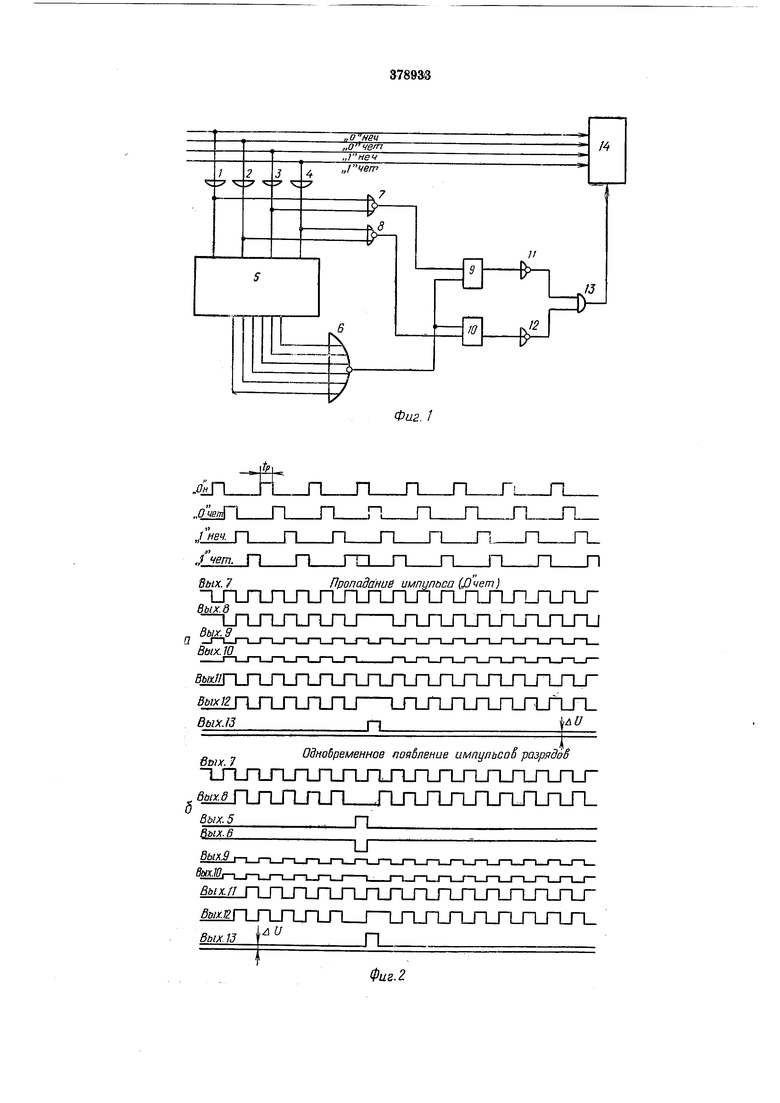

повторители 1-4, дешифратор 5, схемы «ИЛИ - «НЕ 6, 7 и 8, триггеры 9, 10 четных и нечетных разрядов, выходные усилители-инверторы 11, 12, схему 13 совпадения и формирования управляющего сигнала ошибки и блок 14 преобразования и записи информации; на фиг. 2 показаны временные диаграммы, поясняющие работу предложенного устройства.

Если код поступает без ошибок, им-пульсы четных и нечетных разрядов суммируются на схемах «ИЛИ - «НЕ 7, 8 и на выходах их получают последовательности импульсов типа «меандр (скважность равна двум), сдвинутым один относительно другого на 180°

- Г по временной оси).

(т. е. на время сдв

i

Далее эти последовательности импульсов, проходя узлы 9-12, дважды инвертируются и поступают в тех же фазах, что и с выходов схем 7, 8 на схему 13 совпадений. Управляющий импульс схемой 13 не формируется, так как совпадения последовательностей импульсов не происходит по всей временной оси.

Схема «ИЛИ - «НЕ 6 также не формирует никаких выходных сигналов, из-за отсутствия каких-либо совпадений импульсов на матричном дешифраторе 5 совпадений, и таким образом, устройство не вырабатывает управляющих сигналов и не влияет на работу блока 14 преобразования и записи информации. Рассмотрим работу устройства ори наличии в коде ошибок следующих типов: пропадание импульсов одного или нескольких разрядов, одновременное .появление импульсов на двух и более сигнальных щинах. В случае пропадания импульса (или импульсов) одного разряда, например «нулей четных (см. фиг. 2 а), импульсы нечетных разрядов с выходов эмиттер-ных повторителей / и 5 (см. фиг. 1) поступают на схемы «ИЛИ - «НЕ 7, а импульсы «единиц четных разрядов выхода эмиттерного повторителя 4 поступают на схему «ИЛИ - «НЕ 8. Таким образом, на выходе схемы 7 получают последовательность импульсов типа «меандр а на выходе схемы 8 - отрицательные импульсы, соответствующие входным импульсам оставшихся четных «единиц. Эш импульсы дифференцируются и своими фронтами перебрасывают триггеры 9 и 10. Нерепады напряжения на выходе триггеров 9 и 10 управляют работой выходных усилителей инверторов 11 и 12, и на выходе последних усилителей инверторов 11 и 12, и на выходе последних получают последовательности импульсов, показанные на фиг. 2а. С помощью схемы 13 совпадения на выходе устройства получают управляющий импульс, сигнализирующий о наличии ошибки в коде, по длительности равный длительности импульса «пропавшего разряда, т. е. hi -jTip pгде иупр-длительность импульсов управления, р - длительность импульса одного разряда, с амплитудой t/ynp KT-A где f/ynp- амплитуда импульса управления, t/KT - максимальная амплитуда напряжения на выходе схемы «НЕ блока 11, At/ начальное смещение схемы «И. При одновременном появлении импульсов на двух сигнальных шинах (например импульсов «единиц четных и «нулей нечетных) они повторяются на эмиттерных повторителях / (см. фиг. 26) и одновременно воздействуют на схемы «ИЛИ - «НЕ 7, 8 и на дешифратор 5 (логическую диодную матрицу сочетаний С1 ). Импульсы четных и нечетных разрядов, проходя схемы «ИЛИ - «НЕ 7, 8 устанавливают триггеры 9 и 10 ъ такое состояние, при котором в дальнейшем совпадение положительных импульсов невозможно. Однако на одном из выходов дешифратора появляется положительный импульс, как результат совпадения импульсов «нулей нечетных и «единиц четных, который усиливается и инвертируется схемой «ИЛИ - «НЕ 6. Отрицательный импульс, снимаемый с выхода блока 6, дифференцируется и своими фронтами управляет состоянием триггеров 9 и 10. Состояние триггера 9 не изменяется, а лишь подтверждается, так как его выходные импульсы представляют собой «меандр с периодом . Триггер 10, который находился в состоянии высокого напряжения, не изменяет своего состояния под воздействием переднего отрицательного фронта (последний подтверждает его состояние) и перебрасывается в состояние низкого напряжения под воздействием заднего положительного фронта дифференцированного импульса. Таким образом, ва выходе триггера 10 получают «меандр с периодом следования , а на выходе схему 13 - управляющий импульс длительностью tp, начинающийся по заднему фронту совпавших импульсов «нулей нечетных и «единиц четных. В дальнейшем управляющие импульсы используются в блоке 14 для сброса (стирания) записанной информации, в которой имеются ощибки (сбои), а также счета самих ошибок. Предмет изобретения Устройство для обнаружения ошибок декодированной информации, содержащее дешифратор, схему совпадения и формирования управляющего сигнала ошибки, триггеры, эмиттерные повторители, усилители-инверторы и блок преобразования и записи информации, отличающееся тем, что, с целью упрощения устройства и повыщения его надежности в работе, введены схемы -«ИЛИ - «НЕ, причем входы первых двух схем «ИЛИ - «НЕ подсоединены ко входам дешифратора и через эмиттерные повторители - к одним из входов блока преобразования и записи информации, а выходы к одним из входов триггеров, другие входы которых подключены к выходу третьей схемы , входы которой подключены к выходам дешифратора, а выходы триггеров через соответствуюшие усилители-инверторы подсоединены ко входам схемы совпадения и формирования управляющего сигнала ошибки, выход которой подключен к другому входу блока преобразования и записи информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| ЦИФРОВОЙ АНАЛИЗАТОР ВРЕМЕИНЫХ ХАРАКТЕРИСТИК ТРАНЗИСТОРНЫХ СХЕМ | 1971 |

|

SU297011A1 |

| ЦИФРОВОЙ ТЕРМОМЕТР | 1971 |

|

SU310131A1 |

| Устройство для акустического каротажа | 1971 |

|

SU443349A1 |

| Устройство для контроля ошибок канала цифровой магнитной записи | 1988 |

|

SU1510007A1 |

| Многоканальный преобразователь кода во временной интервал | 1972 |

|

SU484638A1 |

| Устройство для считывания графической информации с экрана электроннолучевой трубки | 1987 |

|

SU1425736A1 |

| ЦИФРОВОЙ МАГНИТОФОН | 1992 |

|

RU2054715C1 |

| ПРОЛЛЕЖУТОЧНЫЙ УСИЛИТЕЛЬ ВИДЕОСИГНАЛА | 1971 |

|

SU427489A1 |

| Датчик угловой скорости | 1985 |

|

SU1296949A1 |

Авторы

Даты

1973-01-01—Публикация