1

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в качестве функционального элемента универсальных и специализированных однородных структур (вычислительных сред).

Известна ячейка матричной однородной структуры, содержащая два триггера, инверторы и схемы «И и подключенная к двум информационным и трем настроечным машинам. Матричная однородная структура размером т-п, построенная на таких ячейках, имеет 3/п-|-2п- -2 внешних выводов (с учетом шин питания), при этом информационные шины в режиме настройки структуры не используются.

Предложенное устройство отличается от известных тем, что дополнительный настроечный вход соединен со входом дополнительной схемы «И и через инвертор соединен со вхо;дами всех выходных схем «И, вторая ин1формационная шина через дополнительную .схему «И соединена со входами всех входных схем «И обоих триггеров. Это позволяет повысить надежность ячейки и однородной структуры в целом (при реализации их средствами микроэлектроники) за счет уменьшения числа внешних выводов, что достигается использованием информационных шин в режиме настройки структуры.

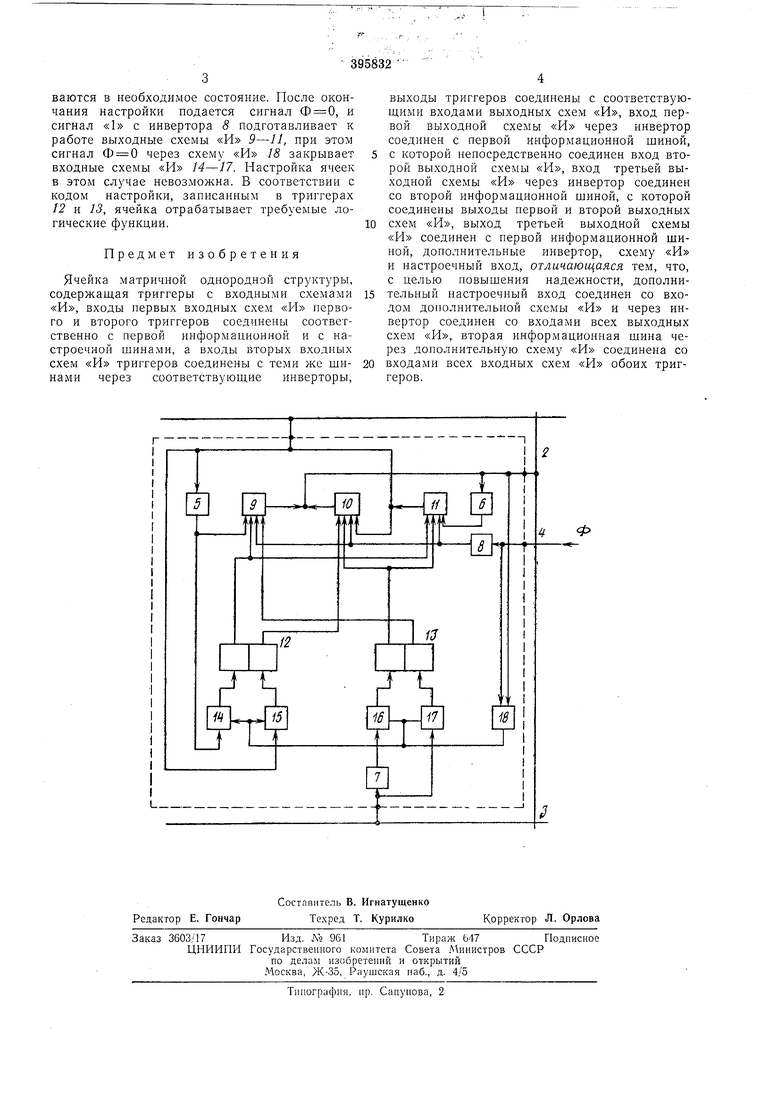

На чертеже изображена схема устройства.

Устройство содержит информационную шину /, к которой подключены данная ячейка и все остальные ячейки соответствующей строки матричной однородной структуры; информационную шину 2, к которой подключены данная ячейка и все остальные ячейки соответствующего столбца структуры; настроечную шину 3 общую для всех ячеек данной строки структуры; дополнительный настроечный вход 4 общий для всех ячеек структуры; инверторы 5-7, дополнительный инвертор 8. выходные схемы «И 9-//; триггеры 12 и 13 с входными схемами «И 14, 15 и 16, 17 соответственно; дополнительн ю схему «И 18.

Работа устройства происходит следующим образом.

При подаче общего настроечного сигнала на вход 4 (режим настройки) структуры нулевой сигнал с инвертора 8 закрывает выходные схемы «И 9-11 и подготавливает к работе схему «И 18. Настройка ячеек производится координатным способом по столбцам. После выбора настраиваемого столбца на шину 2 подается сигнал «1. Этот сигнал проходит через с.хему «И 18 и подготавливает к работе входные схемы «И 14- 17. Настроечная информация подается в ячейку по шинам и 3, триггеры устанавливаются в необходимое состояние. После окончания настройки подается сигнал Ф 0, и сигнал «1 с инвертора 8 подготавливает к работе выходные схемы «И 9-11, при этом сигнал Ф 0 через схему «И 18 закрывает входные схемы «И 14-17. Настройка ячеек в этом случае невозможна. В соответствии с кодом настройки, записанным в триггерах 12 и 13, ячейка отрабатывает требуемые логические функции.

Предмет изобретения

Ячейка матричной однородной структуры, содержащая триггеры с входными схемами «И, входы первых входных схем «И первого и второго триггеров соединены соответственно с первой информационной и с настроечной шинами, а входы вторых входных схем «И триггеров соединены с теми же шинами через соответствуюш,ие инверторы,

выходы триггеров соединены с соответствующими входами выходных схем «И, вход первой выходной схемы «И через инвертор соединен с первой информационной щиной, с которой непосредственно соединен вход второй выходной схемы «И, вход третьей выходной схемы «И через инвертор соединен со второй информационной шиной, с которой соединены выходы первой и второй выходных

схем «И, выход третьей выходной схемы «П соединен с первой информационной щиной, дополнительные инвертор, схему «И и настроечный вход, отличающаяся тем, что, с целью повышения надел ности, дополнительный настроечный вход соединен со входом дополнительной схемы «И и через инвертор соединен со входами всех выходных схем «И, вторая информационная шина через дополнительную схему «И соединена со

входами всех входных схем «И обоих триггеров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическая ячейка | 1975 |

|

SU577525A1 |

| Программируемая ассоциативная логическая матрица | 1988 |

|

SU1597934A1 |

| Устройство для решения задач на графах | 1988 |

|

SU1675907A1 |

| БЛОК НАСТРОЙКИ ЯЧЕЙКИ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 1973 |

|

SU407311A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СТРУКТУРЫ | 1993 |

|

RU2036511C1 |

| Устройство для настройки однородной структуры | 1975 |

|

SU551638A1 |

| Ячейка однородной структуры | 1990 |

|

SU1778757A1 |

| МАТРИЧНАЯ ОДНОРОДНАЯ СТРУКТУРАес^-^союзилнo^tEHTin:-.:.^^:ВИ?:ЛИП. | 1972 |

|

SU359647A1 |

| Ячейка однородной структуры | 1988 |

|

SU1501035A2 |

| Однородная вычислительная среда | 1974 |

|

SU618738A1 |

Даты

1973-01-01—Публикация