1

Изобретение отно.сится к области вычислительной техники ,и дискретной авто;матики, в част1ности оно может быть лс-пользовало вместо магн,ит1ных линий задержек, где требуются импульсы .малой длительности с ;малым регулируемым .интервалом следования.

Известен ра1сп.ределит1ель импульсов, в котором .каждый Каскад .содержит элемент задержки, .выпол.ненный на транзисторе, а «а входе включен триггер.

Однако быстр оде Й1СТВ)И;е та.кого распределителя огра.ничено .вр емвнем переключения триггера и временем восстановления зарядов на .конденсаторах через цепи яагрузоч.ных резисторов.

Целью изобретения является, увеличение быстродействия распределителя.

Для этого в каждый каскад введены две схемы «И .и формирователь и.м.пульсов, выполненный, например, на диодах с .накоплением заряда, причем .вход 1пер.вой схемы «И подключен к выходу элемента задержки своего каскада, а ее выход - жо .входу форм.ирователя дмлульоов своего .каскада и .ко входу элемента задерж.ки следующего каскада, выход .каждого фор.м.ирователя импульсов подключен ко входу второй схемы «И своего каскада, выход которой является выходом соот.ветствуюш.его каскада устройства.

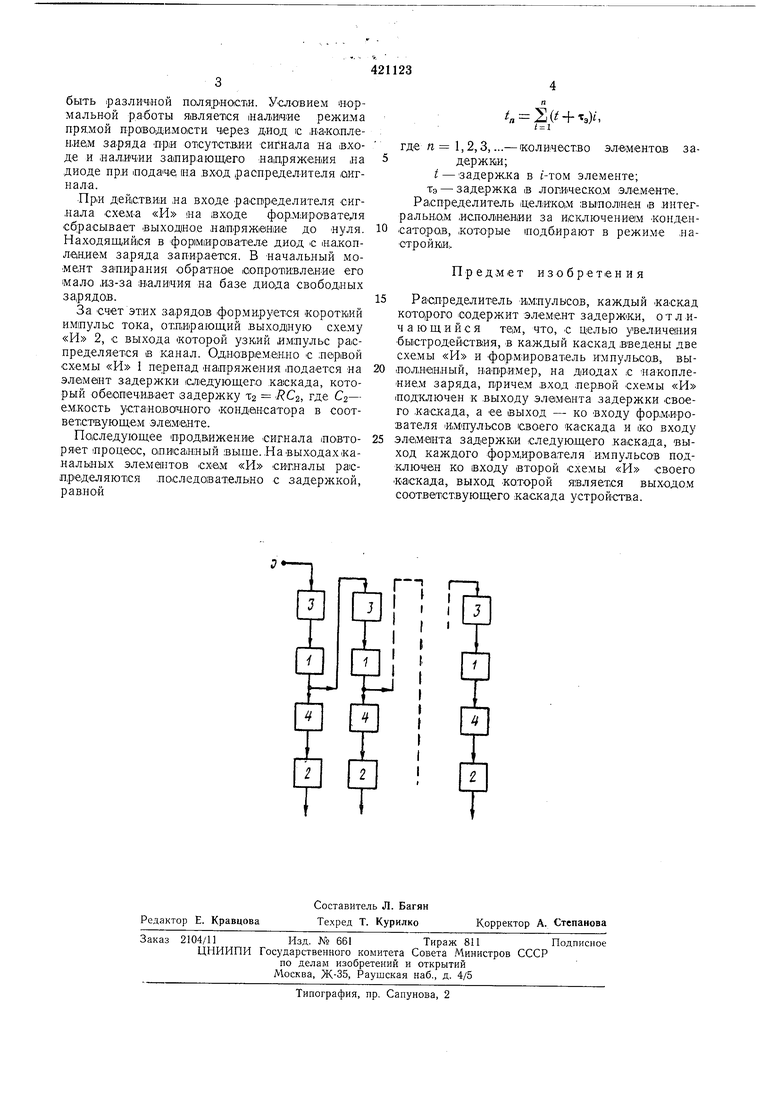

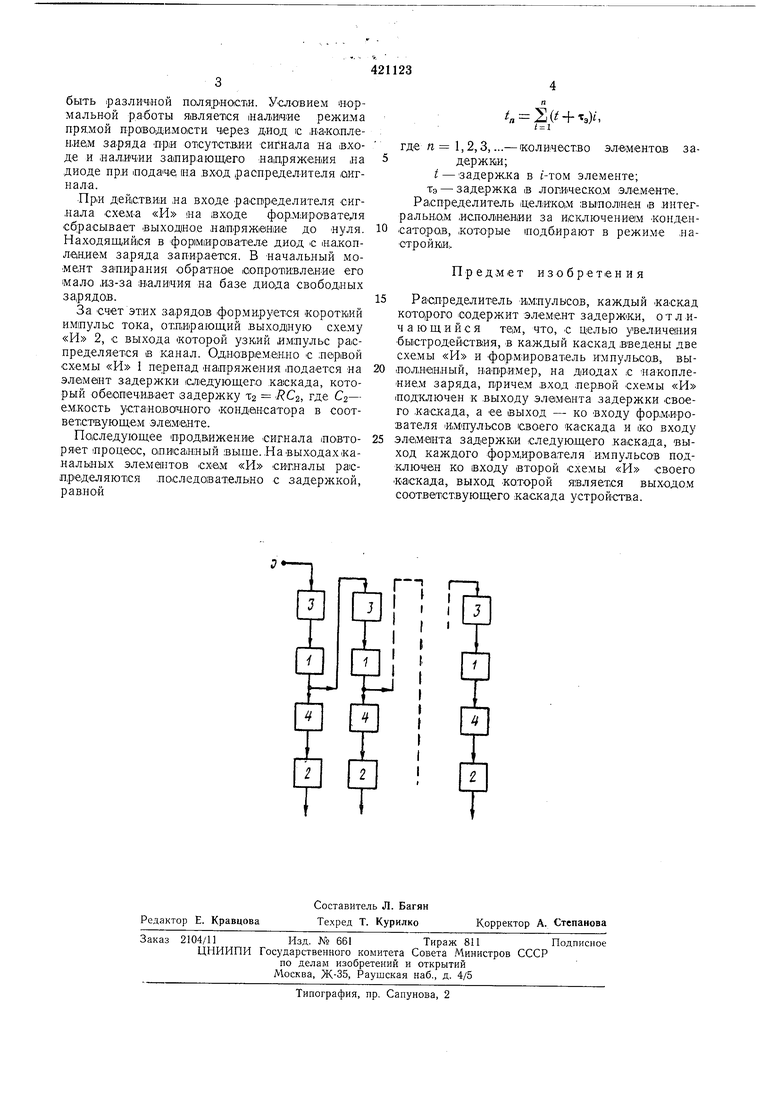

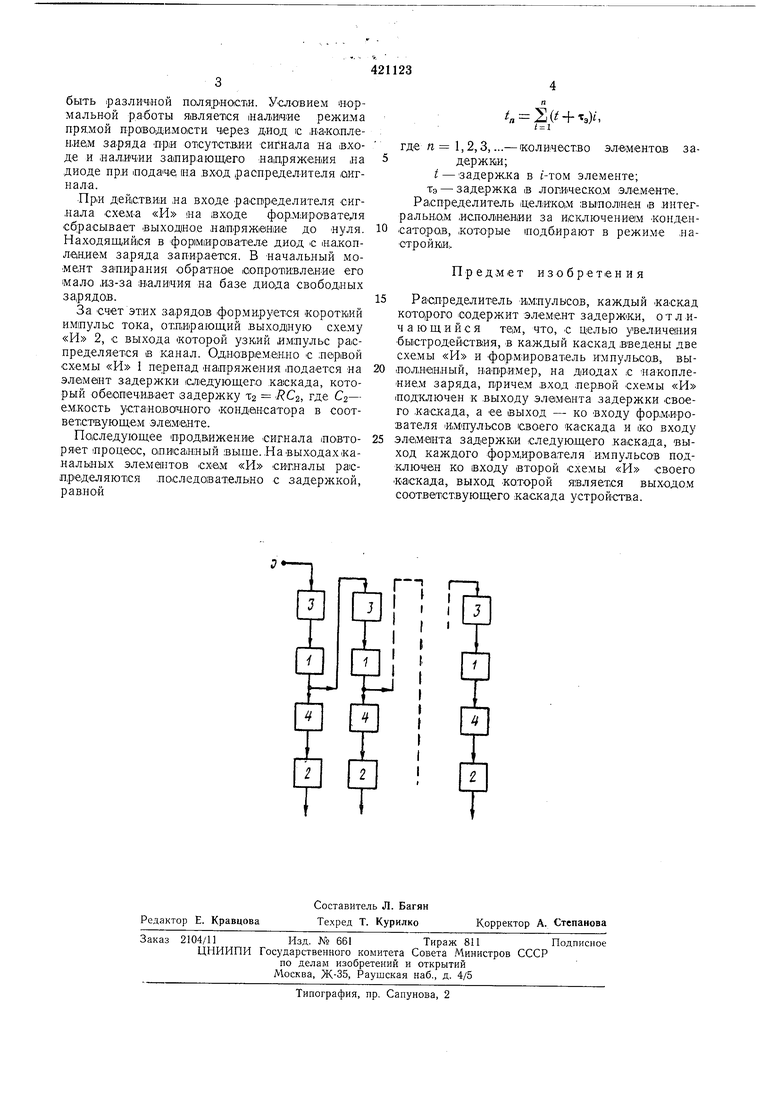

На чертеже 1представле1на функциональная блок-схема предложенного распреде тителя.

Устройство имеет п каскадов, калсдый из которых содержит схемы «И 1, 2, элемент задерж.ки 3 и формиро:ватель 4 узких импульсов, выполненный на диодах с накоплением заряда. Элемент задерж1ки 3 состоит из ко.нденсатора, величина емкости которого выби рается в соответствии с требуемой задержкой

и .импульсного диода, включенного .между .ис точником 5 сигнала и ко.ндвнсаторо.м и слу жащего для разряда послед.него .после око-н чания сигнала. Логические схемы «И 1 и / обеспечивают развязку элементов задержки 3

и формирователей 4, усиление сигнала, нагрузоч.ную способность выходного импульса и условия для получения узких импульсов с формирователя. При (наличии сигнала на .входе диод элемента задержки 3 запирается и его конденсатор начинает заряжаться под действием тока во входной цеп.и .схемы «И 1. Пр.и дост.ижен.ии на конденсаторе .напряжения заряда, равного пороговому, схема «И 1 выключается. Время

задержки определ.ится .как т RC, где R - входное сопротивление схемы «И. При выключении схемы «И на входе формирователя 4 резко изменяется уровень напряжения. В зависимости от типа проводимости полупроводниковых .п.риборов 1на пряжение может

быть различной полярности. Условием нормальной работы является «аличие режима прямой проводим ости через диод ic .ваколлеы,и,бм заряда лри oTicyTCTBiHH сигнала на iBxoде и нал,ИЧИ,и запирающего надряжеиия ,на диоде пр,и подаЧ на вход распределителя оигнала.

При дей|Ств,И|И на входе распределителя сигнала схеМа «И на 1входе формирователя сбрасывает .выходное напряжение до нуля. Находящийся в формирователе диод с н,а.копле|Н,ием заряда запир.ается. В начальный момент запирания обратное оопротквленне его мало ,из-за иаличия на базе диода свободных зарядов.

За счет этих зарядов фор.мируется короткий импульс тока, отдирающий выходную схему «И 2, с выхода «оторой узкий импульс распределя.ется в канал. Одновреме нно с первой схемы «И 1 перепад напряжения подается на эл1емвнт задержки (следующего .каскада, который обеопечнВВет задержку Т2 RC-, где Сг- ем,кость ycTaiHOBO4H;oro Конденсатора в соответствующем элементе.

Последующее продв1ижени1е сигнала повторяет процесс, описанный выше.,На выходах канальных элемантов схе,м «И сигналы распределяются последовательно с задержкой, равной

„ 2( + taX, г 1

где п 1,2,3,...- количество элементов задержки;

t-задержка в t-том элементе; тэ - задержка в логическом элементе. Распределитель .целикам выполнен в .интегральном исполнении за исключени ам .конденсаторов, (Которые подбирают в режиме настрой кй,.

Предмет изобретения

Распределитель и,мпулвсо.в, каждый каскад которого .содержит элемент задержки, отличающийся тем, что, с целью увеличения быстродейств)ия, в ка.ждый каскад введены две схемы «И и формирователь кмпульсов, выполненный, например, на диодах с накоплением заряда, причем вход первой схемы «И подключен к .выходу элем-анта задержки своего -каскада, а ее выход - ко входу формирователя .импульсов 1сво.его каскада и ко входу

элем.еита задержК|И .следующего .каскада, выход каждого формирователя импульсов подключен ко входу второй схемы «И своего к.аскада, выход которой является выходо.м соотввтствующего :Ка.скада устройств,а.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов для управления тиристорами | 1990 |

|

SU1760610A1 |

| ИСТОЧНИК ПИТАНИЯ ДЛЯ ДУГОВОЙ ЭЛЕКТРОСВАРКИ НА ПОСТОЯННОМ ТОКЕ | 1996 |

|

RU2094196C1 |

| РЕЛЕ ВРЕМЕНИ (С ВЫХОДОМ НА СИМИСТОРЕ) | 1992 |

|

RU2130213C1 |

| Многоканальный программируемый коммутатор | 1982 |

|

SU1112555A1 |

| Инвертор | 1987 |

|

SU1504767A1 |

| Формирователь импульсов для управления диодными фазовращателями | 1975 |

|

SU562914A1 |

| Стабилизированный выпрямитель | 1978 |

|

SU748381A1 |

| Устройство для формирования импульсов управления вентилями преобразователя | 1987 |

|

SU1515281A1 |

| Электронный коммутатор системы зажигания | 1990 |

|

SU1774060A1 |

| Одновибратор | 1983 |

|

SU1129716A1 |

Даты

1974-03-25—Публикация

1972-05-31—Подача