1

Изобретение относится к устройствам для электрических измерений и может быть применено в цифровых измерительных приборах, в частности, для установки триггера но сигналу от источника, имеющего емкостный характер.

Известна балансная схема сравнения, выполненная на двух транзисторных каскадах, в которой в зависимости от величины сравниваемых напряжений изменяются входное сопротивление и ток базы транзисторов первого каскада, что особенно нежелательно, когда источники сравниваемых напряжений имеют емкостный характер, так как при этом происходит изменение и величины сравниваемых напряжений. Кроме того, при достаточно быстром изменении сравниваемых напряжений достаточно быстро изменяется ток в балансном трансформаторе и на выходе балансного трансформатора может появиться импульс значительной амплитуды без подачи импульса опроса, что в ряде случаев недопустимо, так как этот импульс помехи может нарушить правильное функционирование устройства, в котором используется схема сравнения. Кроме того, в выходной цепи трансформатора при импульсном опросе образуются во времени два выходных импульса противоположной полярности: первый, когда выходные транзисторы импульсом опроса закрываются, и второй.

когда импульс опроса кончается и выходные транзисторы открываются, что так же нежелательно в ряде случаев, например, при установке выходным и.мпульсом триггера. Целью предлагаемого изобретения является повышение помехоустойчивости.

Это достигается введением в выходной трансформатор дополнительной вторичной оо.мотки, причем вы.ходные обмогки включены

встречно меладу базой и эмиттеро.м соответствуюш,их транзисторов выходного каскада, а коллекторы транзисторов соединены с блоком стробирования. В результате при отсутствии импульса опроса ток как в первом, так и во

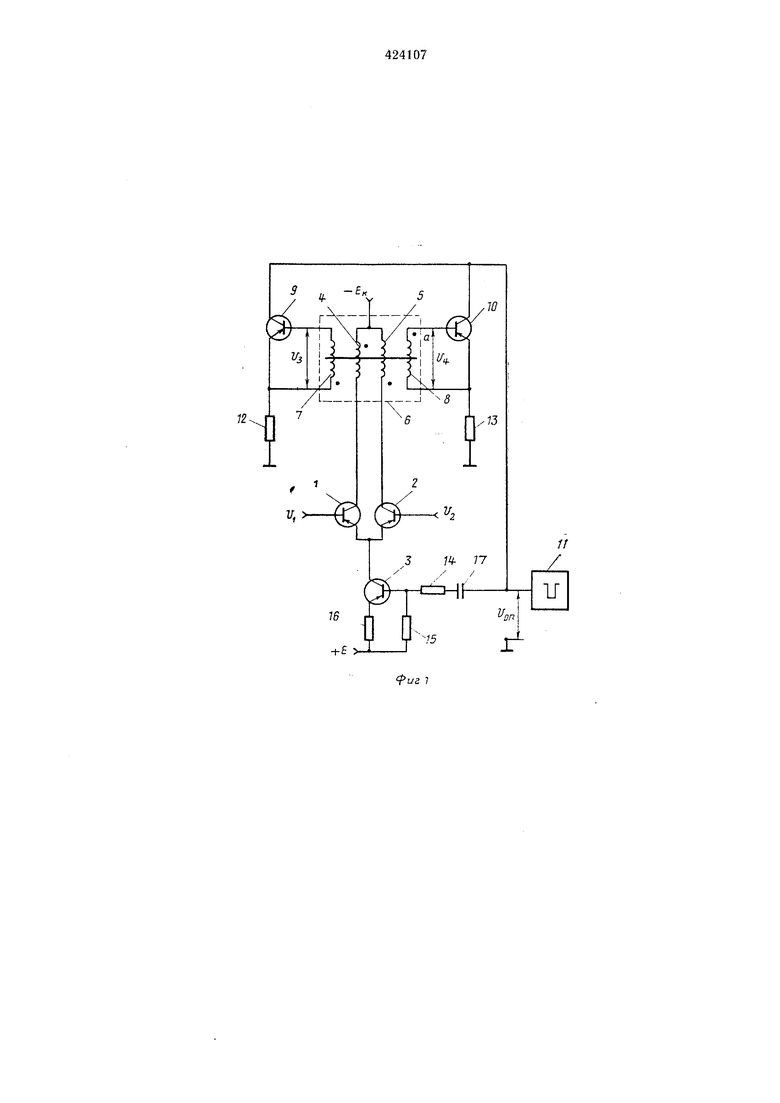

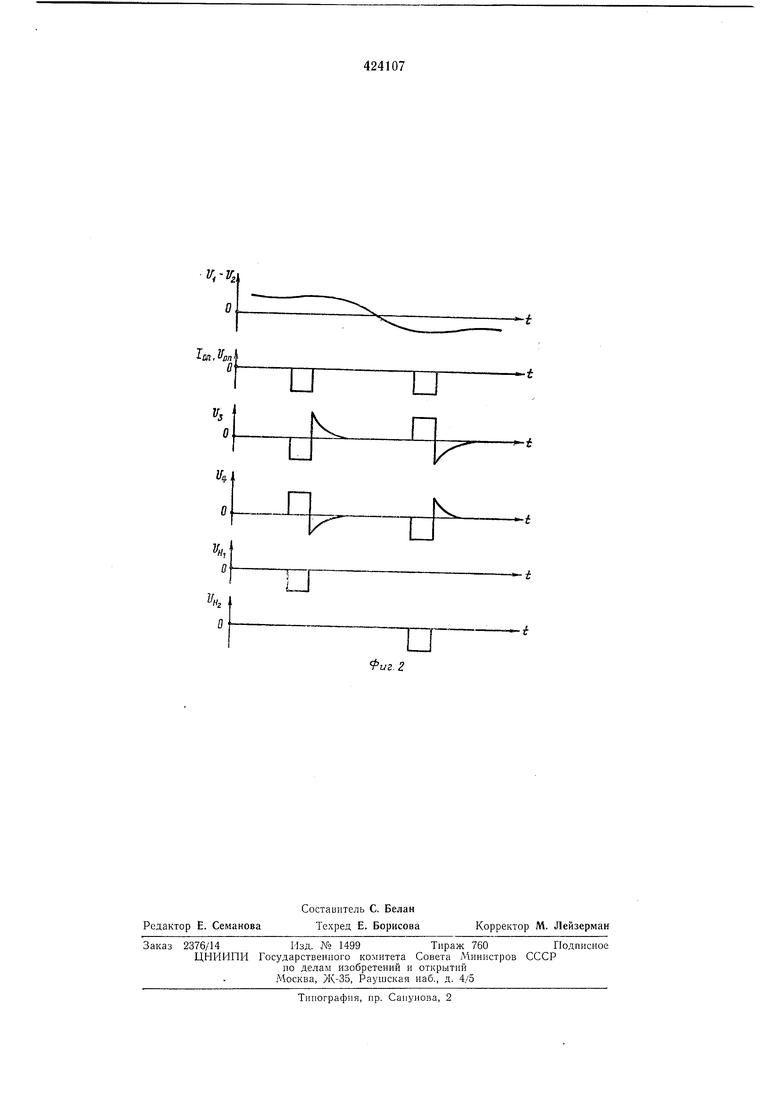

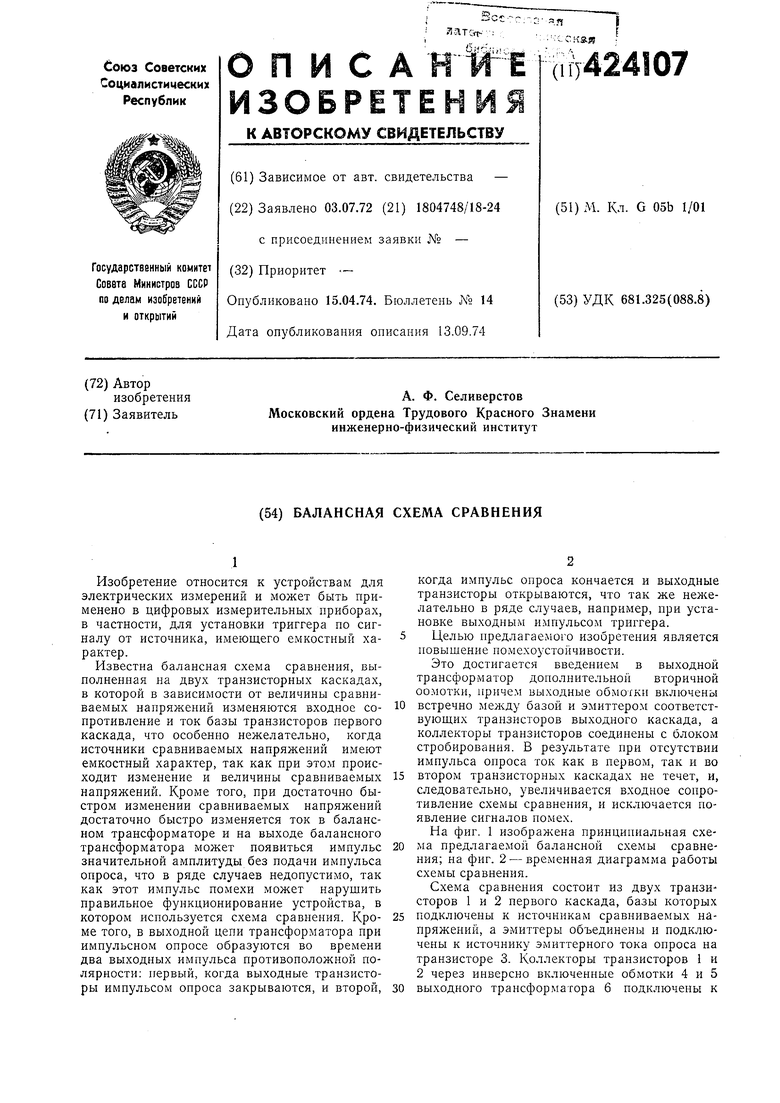

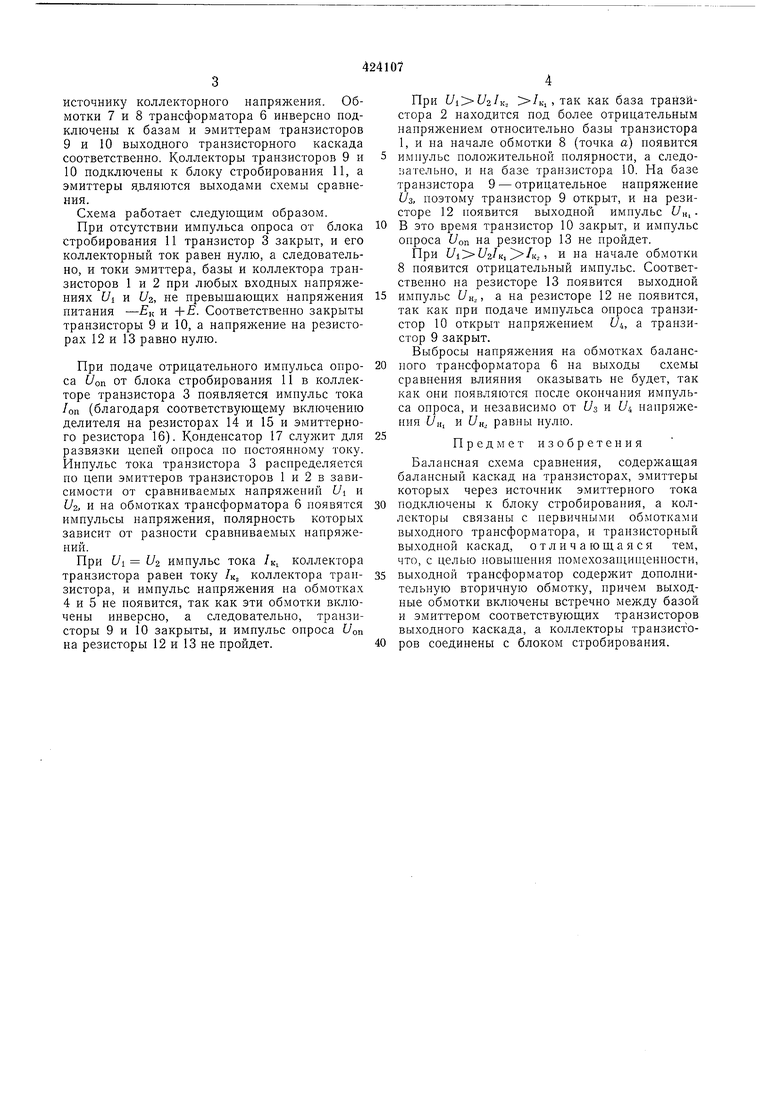

втором транзисторных каскадах не течет, и, следовательно, увеличивается входное сопротивление схемы сравнения, и исключается появление сигналов помех. На фиг. 1 изображена принципиальная схема предлагаемой балансной схемы сравнения; на фиг. 2 - временная диаграмма работы схемы сравнения.

Схема сравнения состоит из двух транзисторов 1 и 2 первого каскада, базы которых

подключены к источникам сравниваемых напряжений, а эмиттеры объединены и подключены к источнику эмиттерного тока опроса на транзисторе 3. Коллекторы транзисторов 1 и 2 через инверсно включенные об.мотки 4 и 5

выходного трансформатора 6 подключены к

источнику коллекторного напряжения. Обмотки 7 и 8 трансформатора 6 инверсно подключены к базам и эмиттерам транзисторов

9и 10 выходного транзисторного каскада соответственно. Коллекторы транзисторов 9 и

10подключены к блоку стробирования 11, а эмиттеры я.вляются выходами схемы сравнения.

Схема работает следующим образом.

При отсутствии импульса опроса от блока стробирования 11 транзистор 3 закрыт, и его коллекторный ток равен нулю, а следовательно, и токи эмиттера, базы и коллектора транзисторов 1 и 2 при любых входных напряжениях f/i и f/2, не превышающих напряжения питания -ЕК и +Е. Соответственно закрыты транзисторы 9 и 10, а напряжение на резисторах 12 и 13 равно нулю.

При подаче отрицательного импульса опроса Uon от блока стробирования 11 в коллекторе транзистора 3 появляется импульс тока /on (благодаря соответствующему включению делителя на резисторах 14 и 15 и эмиттерного резистора 16). Конденсатор 17 служит для развязки цепей опроса по постоянному току. Инпульс тока транзистора 3 распределяется по цепи эмиттеров транзисторов 1 и 2 в зависимости от сравниваемых напряжений Ui и Uz, и на обмотках трансформатора 6 появятся импульсы напряжения, полярность которых зависит от разности сравниваемых напряжений.

При t/i t/2 импульс тока 1к, коллектора транзистора равен току IK, коллектора транзистора, и импульс напряжения на обмотках 4 и 5 не появится, так как эти обмотки включены инверсно, а следовательно, транзисторы 9 и 10 закрыты, и импульс опроса f/on на резисторы 12 и 13 не пройдет.

При (72/Kj /к, , так как база транзй стора 2 находится под более отрицательным напряжением относительно базы транзистора 1, и на начале обмотки 8 (точка а) появится импульс положительной полярности, а следоиательно, и на базе транзистора 10. На базе транзистора 9 - отрицательное напряжение L/S, поэтому транзистор 9 открыт, и на резисторе 12 появится выходной импульс и„. В это время транзистор 10 закрыт, и импульс опроса боп на резистор 13 не пройдет.

При f/i -f/2/K, /к,, и на начале обмотки 8 появится отрицательный импульс. Соответственно на резисторе 13 появится выходной импульс UK,, а на резисторе 12 не появится, так как при подаче импульса опроса транзистор 10 открыт напряжением Ui,, а транзистор 9 закрыт.

Выбросы напряжения на обмотках балансного трансформатора 6 на выходы схемы сравнения влияния оказывать не будет, так как они появляются после окончания импульса опроса, и независимо от Us и U/, напряжения У„, и t/H, равны нулю.

п и

Предмет изобретения

Балансная схема сравнения, содержащая балансный каскад на транзисторах, эмиттеры которых через источник эмиттерного тока

подключены к блоку стробирования, а коллекторы связаны с первичными обмотками выходного трансформатора, и транзисторный выходной каскад, отличающаяся тем, что, с целью повышения помехозащищенности,

выходной трансформатор содержит дополнительную вторичную обмотку, причем выходные обмотки включены встречно между базой и эмиттером соответствующих транзисторов выходного каскада, а коллекторы транзисторов соединены с блоком стробирования.

/;

| название | год | авторы | номер документа |

|---|---|---|---|

| БАЛАНСНАЯ СХЕМА СРАВНЕНИЯ! | 1970 |

|

SU267209A1 |

| УСТРОЙСТВО для СРАВНЕНИЯ | 1970 |

|

SU269223A1 |

| Высоковольтный стабилизатор напряжения постоянного тока | 1981 |

|

SU957188A1 |

| Устройство для сравнения напряжений | 1974 |

|

SU539296A1 |

| Устройство сравнения | 1972 |

|

SU430728A1 |

| УСТРОЙСТВО ПОРОГОВОГО КОНТРОЛЯ НАПРЯЖЕНИЙ | 1973 |

|

SU382012A1 |

| СХЕМА СРАВНЕНИЯ | 1968 |

|

SU221773A1 |

| Стабилизированный источник питания | 1979 |

|

SU888090A1 |

| БИБЛИОТЕИ.,^^ | 1973 |

|

SU376887A1 |

| Стабилизированный источник питания | 1980 |

|

SU951265A2 |

Даты

1974-04-15—Публикация

1972-07-03—Подача