1

Изобретение относится к области измерительной цифровой и вычислительной аналогонифровой техники и может быть использовано в преобразователях напряжение-код с быстродействием 10°-10 нр/сек.

Известно аналоговое заПоминающее устройство, содержап1.ее запоминаюндую емкость и мостовую схему переключателя напряжения.

Однако такое устройство имеет недостаточную точность, и кроме того, для него необходим мощный управляющий сигнал.

Цель изобретения - повышение номехозащйщепности и точности запоминания.

Это достигается путем подключения последовательно соединенных заномипающих конденсаторов, включенных в одну из диагоналей моста, образованного четырьмя транзисторами, между попарно подключенными коллекторами этих транзисторов, к входам соответствующих эмнттерных новторителей, выходы которых соединены с соответствующими входами пассивных суммирующих пеней, другие входы которых подключены к входным клеммам устройства, а выходы соединены с базами транзисторов, образующих мост, включения в другую диагональ моста унравляюи1его транзистора, база которого соединена с источником имнульсов онроса, и подключения общих обкладок запоминающих конденсаторов к шине нулевого потенционала.

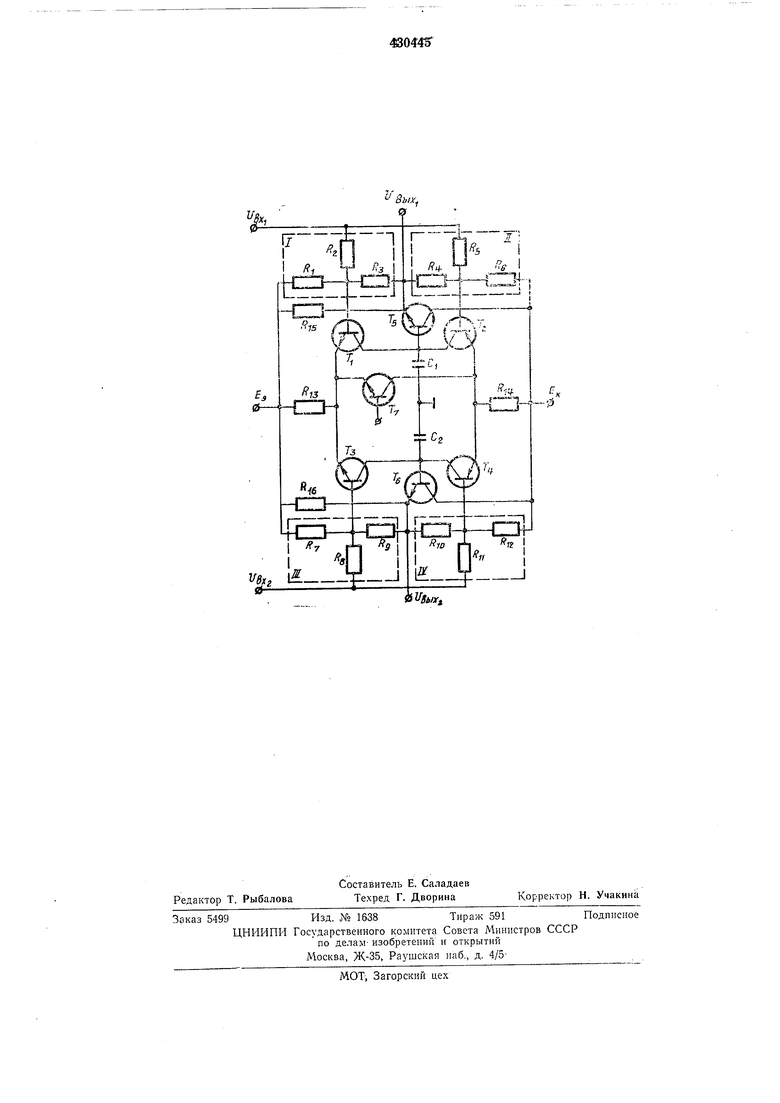

На чертеже показана принципиальная схема предлагаемого устройства.

Запоминающие емкости Ci и Cz включены в диагональ моста между земляной П1иной и попарно соединенными коллекторами транзисторов 7i, Т2 и Гз, Т, образующих мостовую схему, к которым подсоединены также входы эмиттерных повторителей (базы транзисторов Го, Гб), Выходы каждого из эмиттерных повторителей подсоединены к входам двух суммируюпднх нассивных неней на сонротивлениях, другие входы которых нодсоединены к источнику входного сигнала.

Выход эмиттерного повторителя на транзисторе TS подключен к входу суммирующей пассивной пени I (сопротивления Ri, R. Rj), выход которой подсоедипен к базе транзистора Г, и к входу суммирующей пассивной цепи II (сопротивления ,4, Rz, Rs), выход которой подсоединен к базе транзистора Уо. Выход эмиттерного новторителя на транзисторе Гб подключен к входу суммирующей

пассивной цепи III (сопротивления 7, s. , выход которой подсоединен к базе транзистора Гз, и к входу суммирующей пассивной цени IV (сопротивления R, ), выход которой подсоединен к базе транзистора /4.

Эмиттер п коллектор управляющего транзйстора подключены к попарно объединенным эмиттерам транзисторов Т, Тз и Т, Т, т. е. в диагональ моста, а база подключена к выходу источника импульсов заииси. Сопротивления и включены между попарно объединенными эмиттерами транзисторов, образующих мост, и выходами источников питания.

В паузе между импульсами записи управляющий транзистор Tj открыт, транзисторы Гь- Тч, Гз, T закрыты, и напряжение на запоминающих емкостях остается постоянным.

При подаче импульса записи управляющий транзистор ГУ закрывается, транзисторы Г, TZ, TZ, 4 открываются и начинается лерезаряд запоминающих емкостей. Емкость С заряжается разностью коллекторных TOKOR транзисторов Г) и Гг, а емкость Са - раностью коллекторных токов транзисторов Уз, T. По достижении значением напряжения на емкостях значения входного напряжения коллекторный ток транзистора Т становится равным коллекторному току транзистора 72 и, следовательно, оказываются равными коллекторные токи транзисторов Гз и Г4. Токи через запоминающие емкости Ci и Cz становятся равными нулю. По окончании импульса записи управляющий транзистор T открывается, транзисторы Гь TZ, Гз, Г4 закрываются, к заряды на запоминающих емкостях остаются постоянными.

За счет полной симметричности схемы и охвата отрицательной обратной связью схема имеет малую нестабильность и критичносты к помехам по питающим напряжениям.

Предмет изобретения

Аналогое запоминающее устройство, содержащее последовательно соединенные запоминающие конденсаторы, включенные в одну из диагоналей моста, образованного четырьмя транзисторами, между попарно соединенными коллекторами этих транзисторов, отличающееся тем, что, с целью повышения помехозащищенности и точности запоминания, попарно соединенные коллекторы указанных транзисторов подключены также к входам соответствующих эмиттерных повторителей, выходы эмиттерных повторителей соединены с соответствующими входами пассивных суммирующих цепей, другие входы которых подключены к входным клеммам устройства, а

выходы соединены с базами транзисторов, образующих мост; в другую диагональ моста включен управляющий транзистор, база которого соединена с источником импульсов опроса, а общие обкладки запоминающих конденсаторов подключены к шине нулевого потенциала.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ФОРМИРОВАНИЯ БИПОЛЯРНЫХ ИМПУЛЬСОВ УПРАВЛЕНИЯ | 1972 |

|

SU343349A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОЙ СТАБИЛИЗАЦИИ | 1970 |

|

SU284099A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ОТКЛОНЕНИЯЧАСТОТЫ | 1972 |

|

SU453642A1 |

| ПОЛУПРОВОДНИКОВОЕ УСТРОЙСТВО для КОНТРОЛЯ ФИЗИЧЕСКОЙ ВЕЛИЧИНЫ | 1968 |

|

SU208798A1 |

| РЕЛЕЙНЫЙ СТАБИЛИЗАТОР НАПРЯЖЕНИЯ | 1969 |

|

SU246602A1 |

| МУЛЬТИВИБРАТОР | 1972 |

|

SU426308A1 |

| РЕГУЛЯТОР НАПРЯЖЕНИЯ ДЛЯ ГЕНЕРАТОРОВ ПОСТОЯННОГО И ПЕРЕМЕННОГО ТОКА | 1970 |

|

SU277913A1 |

| ИСКРОБЕЗОПАСНЫЙ ИСТОЧНИК ПИТАНИЯ | 1970 |

|

SU286057A1 |

| Коммутатор аналоговых сигналов | 1988 |

|

SU1517125A1 |

| МУЛЬТИВИБРАТОР | 1972 |

|

SU432666A1 |

Даты

1974-05-30—Публикация

1972-07-13—Подача