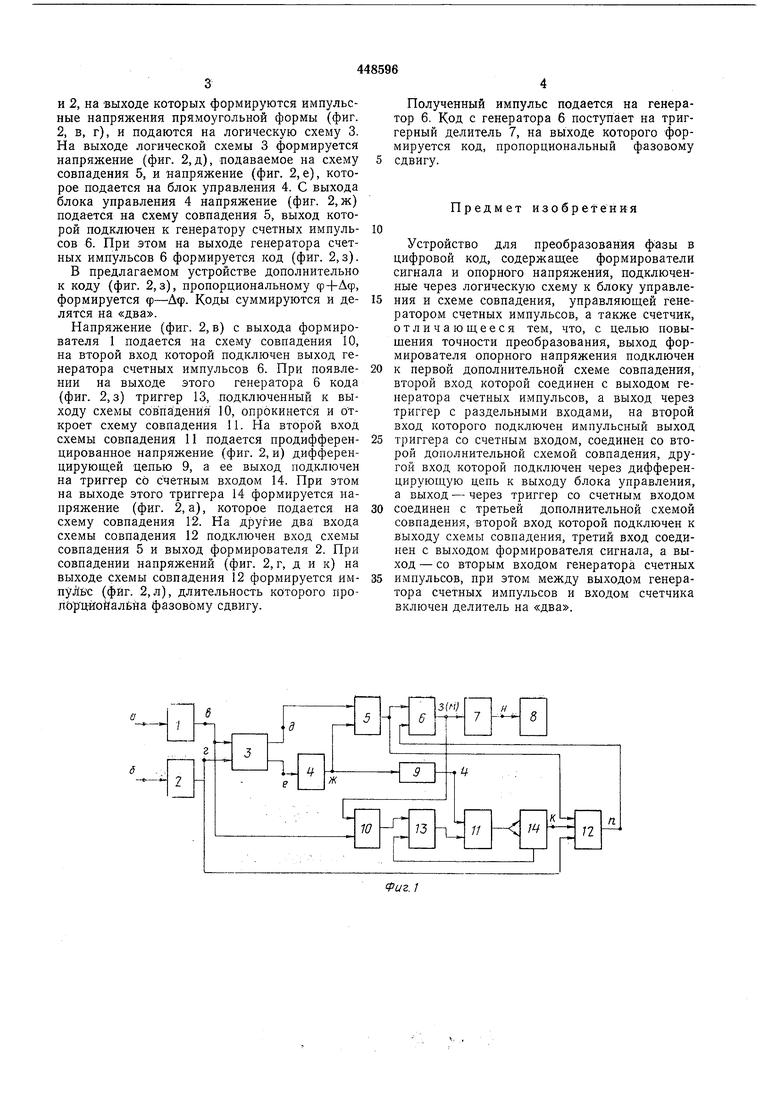

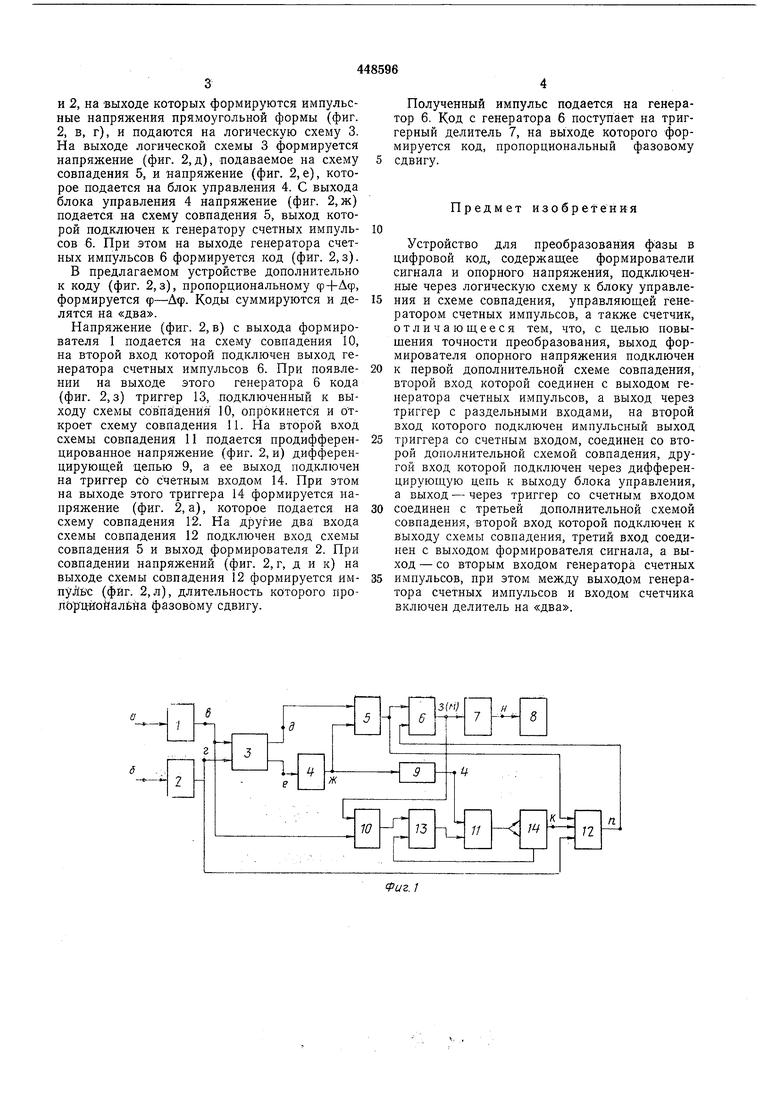

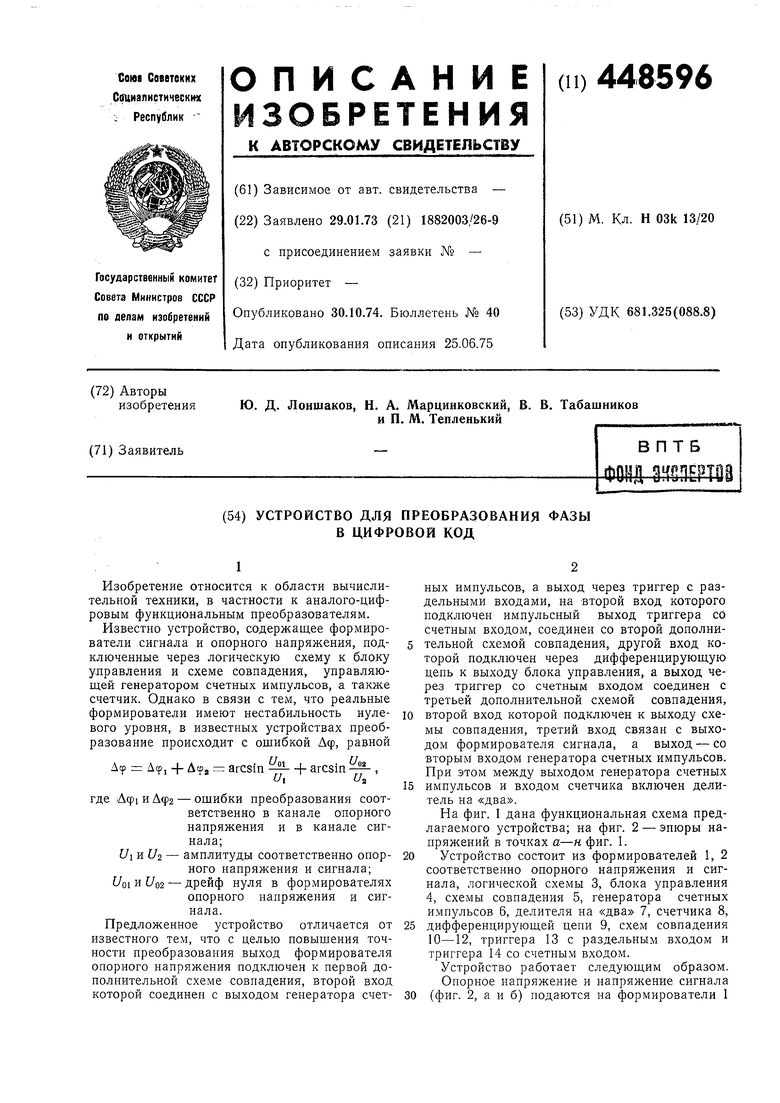

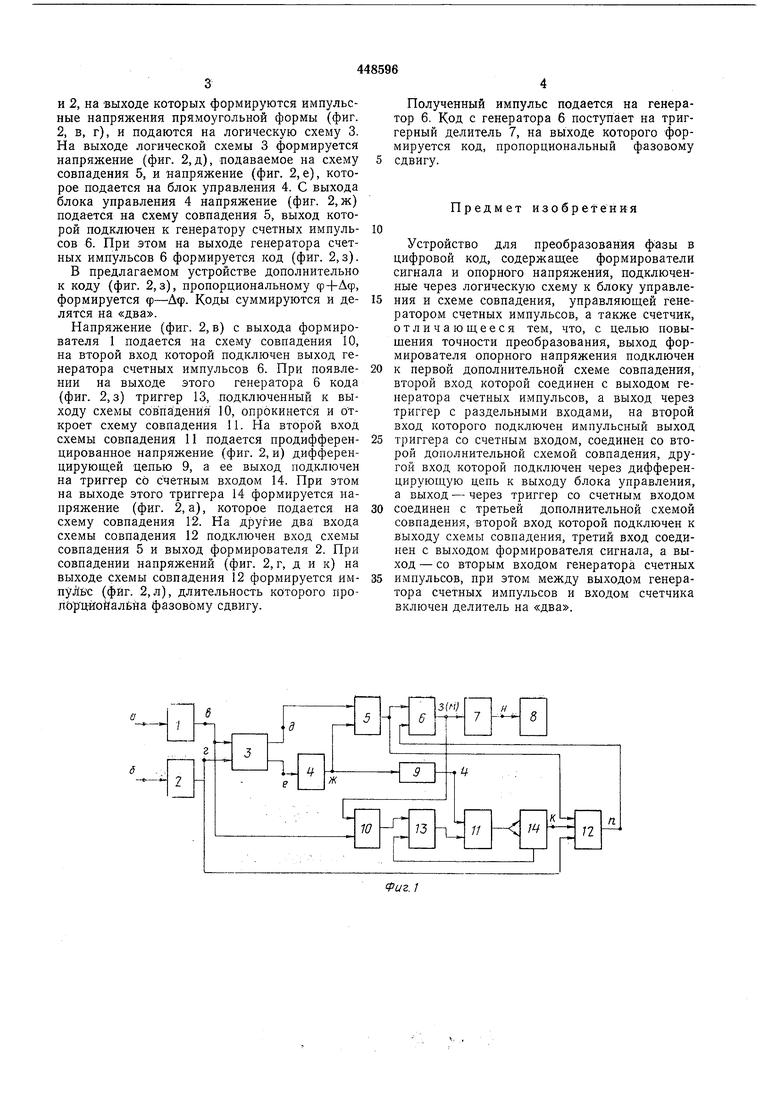

Изобретение относится к области вычислительной техники, в частности к аналого-цифровым функциональным преобразователям. Известно устройство, содержащее формирователи сигнала и опорного напряжения, подключенные через логическую схему к блоку управления и схеме совпадения, управляющей генератором счетных импульсов, а также счетчик. Однако в связи с тем, что реальные формирователи имеют нестабильность нулевого уровня, в известных устройствах преобразование происходит с ошибкой Аф, равной Д(р Дер, + Atp2 - arcsin - + arcsin - , где ДФ1ИДФ2 - ошибки преобразования соответственно в канале опорного напряжения и в канале сигнала;Ll и f/2 - амплитуды соответственно опорного напряжения и сигнала; 01 и С/02 - Дрейф нуля в формирователях опорного напряжения и сигнала. Предложенное устройство отличается от известного тем, что с целью повышения точности преобразования выход формирователя опорного напряжения подключен к первой дополнительной схеме совпадения, второй вход которой соединен с выходом генератора счетных импульсов, а выход через триггер с раздельными входами, на второй вход которого подключен импульсный выход триггера со счетным входом, соединен со второй дополнительной схемой совпадения, другой вход которой подключен через дифференцирующую цепь к выходу блока управления, а выход через триггер со счетным входом соединен с третьей дополнительной схемой совпадения, второй вход которой подключен к выходу схемы совпадения, третий вход связан с выходом формирователя сигнала, а выход - со вторым входом генератора счетных импульсов. При этом между выходом генератора счетных импульсов и входом счетчика включен делитель на «два. На фиг. 1 дана функциональная схема предлагаемого устройства; на фиг. 2 - эпюры напряжений в точках а-н фиг. 1. Устройство состоит из формирователей 1, 2 соответственно опорного напряжения и сигнала, логической схемы 3, блока управления 4, схемы совпадения 5, генератора счетных импульсов 6, делителя на «два 7, счетчика 8, дифференцирующей цепи 9, схем совпадения 10-12, триггера 13 с раздельным входом и триггера 14 со счетным входом. Устройство работает следующим образом. Опорное напряжение и напряжение сигнала (фиг. 2, а и б) подаются на формирователи 1

и 2, на выходе которых формируются импульсные напряжения прямоугольной формы (фиг. 2, в, г), и подаются на логическую схему 3. На выходе логической схемы 3 формируется напряжение (фиг. 2, д), подаваемое на схему совпадения 5, и напряжение (фиг. 2, е), которое подается на блок управления 4. С выхода блока управления 4 напряжение (фиг. 2, ж) подается на схему совпадения 5, выход которой подключен к генератору счетных импульсов 6. При этом на выходе генератора счетных импульсов 6 формируется код (фиг. 2, з).

В предлагаемом устройстве дополнительно к коду (фиг. 2,з), пропорциональному ф+Аф, формируется . Коды суммируются и делятся на «два.

Напряжение (фиг. 2, в) с выхода формирователя 1 подается на схему совпадения 10, на второй вход которой подключен выход генератора счетных импульсов 6. При появлении на выходе этого генератора 6 кода (фиг. 2, з) триггер 13, подключенный к выходу схемы совпадения 10, опрокинется и откроет схему совпадения 11. На второй вход схемы совпадения 11 подается продифференцированное напряжение (фиг. 2, и) дифференцирующей цепью 9, а ее выход подключен на триггер со счетным входом 14. При этом на выходе этого триггера 14 формируется напряжение (фиг. 2,а), которое подается на схему совпадения 12. На другие два входа схемы совпадения 12 подключен вход схемы совпадения 5 и выход формирователя 2. При совпадении напряжений (фиг. 2, г, д и к) на выходе схемы совпадения 12 формируется импуЛьс (фиг. 2,л), длительность которого пропЬрцйоЙалЬйа фазовому сдвигу.

Полученный импульс подается на генератор 6. Код с генератора 6 поступает на триггерный делитель 7, на выходе которого формируется код, пропорциональный фазовому сдвигу.

Предмет изобретения

Устройство для преобразования фазы в цифровой код, содержащее формирователи сигнала и опорного напряжения, подключенные через логическую схему к блоку управлекия и схеме совпадения, управляющей генератором счетных импульсов, а также счетчик, отличающееся тем, что, с целью повыщения точности преобразования, выход формирователя опорного напряжения подключен

к первой дополнительной схеме совпадения, второй вход которой соединен с выходом генератора счетных импульсов, а выход через триггер с раздельными входами, на второй вход которого подключен импульсный выход

триггера со счетным входом, соединен со второй дополнительной схемой совпадения, другой вход которой подключен через дифференцирующую цепь к выходу блока управления, а выход - через триггер со счетным входом

соединен с третьей дополнительной схемой совпадения, второй вход которой подключен к выходу схемы совпадения, третий вход соединен с выходом формирователя сигнала, а выход - со вторым входом генератора счетных

импульсов, при этом между выходом генератора счетных импульсов и входом счетчика включен делитель на «два.

г д р ж

3 и к л м

н

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования фазовой модуляции сигнала в цифровой код | 1975 |

|

SU741460A1 |

| Устройство для измерения коэффициента прямоугольности амплитудно-частотной характеристики радиоприемников | 1990 |

|

SU1755383A1 |

| ПРЕОБРАЗОВАТЕЛЬ ФАЗОВОГО СДВИГА ПЕРЕМЕННЫХ НАПРЯЖЕНИЙ В ЦИФРОВОЙ КОД | 1972 |

|

SU359756A1 |

| Способ исследования колебаний с постоянным периодом и устройство для его осуществления | 1985 |

|

SU1326903A1 |

| ЭЛЕКТРОМАГНИТНЫЙ ДЕФЕКТОСКОП | 1973 |

|

SU386331A1 |

| Преобразователь отклонения частоты от номинального значения в аналоговый сигнал | 1990 |

|

SU1748082A1 |

| Устройство для измерения плотности распределения экстремумов | 1983 |

|

SU1101840A1 |

| Счетно-импульсный преобразователь разности последовательных кодов в параллельный | 1975 |

|

SU612241A1 |

| Устройство для измерения сдвига фаз | 1984 |

|

SU1161894A1 |

| Преобразователь уго-код | 1972 |

|

SU439836A1 |

Авторы

Даты

1974-10-30—Публикация

1973-01-29—Подача