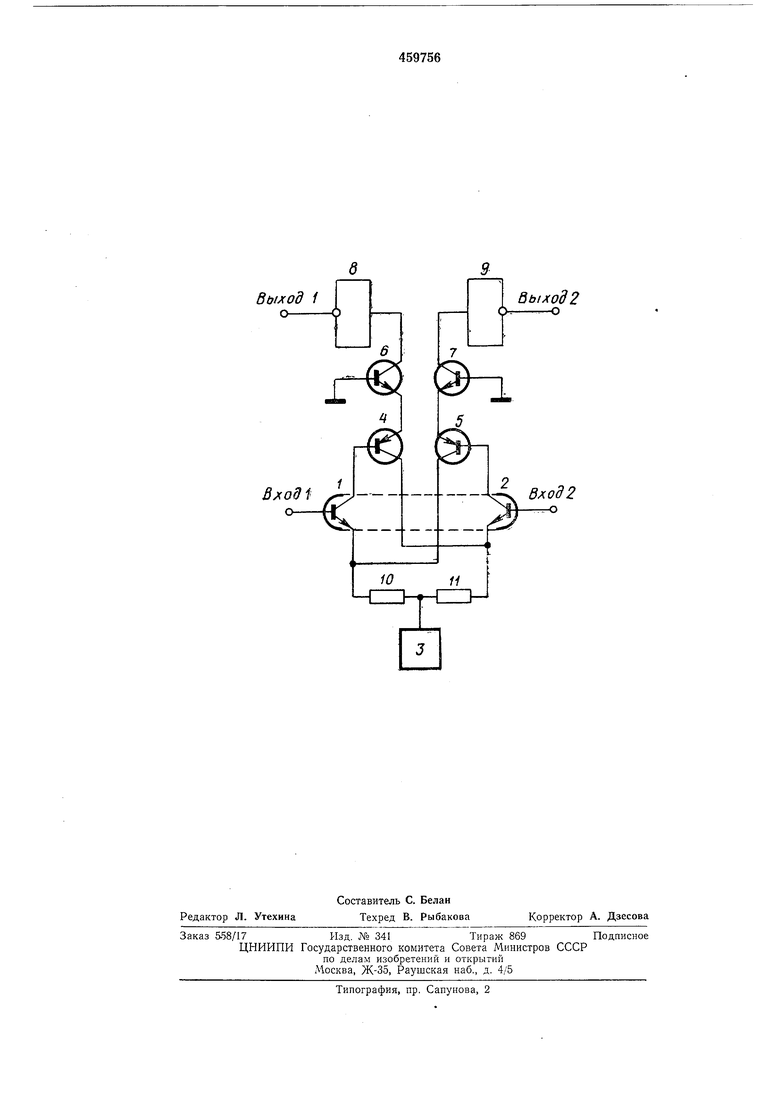

ветствующий транзистор (например, транзистор 1) поступает ток большой величины. Этот ток усиливается дополнительным транзистором 4, и на резисторе 11 формируется падение напряжений, запирающее переход эмиттер-база транзистора 2. Таким образом, весь ток блока опроса 3 поступает в каскад 6 с общей базой и усилитель-формирователь 8. При этом на выходе усилителя-формирователя вырабатывается сигнал, соответствующий логической «1.

Устройство реализует два типа обратных связей:

1)положительную обратную связь с коллектором открывающегося транзистора балансного усилителя на эмиттер второго транзистора БУ через дополнительный транзистор

4 (5);

2)отрицательную обратную связь на эмиттер открывающего транзистора БУ.

Введение обратных связей позволяет увеличить чувствительность за счет увеличения коэффициента усиления усилителя и введения активных обратных связей, увеличить быстродействие за счет уменьшения величин резисторов обратных связей (10, 11), увеличить входное сопротивление за счет исключения обратных связей на базы транзисторов 1 и 2;

снять требование гальванической развязки цепи опроса состояния сравнивающего устройства без снижения входного сопротивления;

снизить тепловой дрейф, вызванный саморазогревом транзисторов и влиянием входных сигналов, пропорционально скважности импульсов опроса состояния сравнивающего устройства. При этом рабочие токи транзисторов выбирают таким образом, чтобы максимально реализовать их частотные и усилительные свойства.

Предмет изобретения

Сравнивающее устройство, содержащее балансный усилитель, выполненный на транзисторах, базы которых подключены к источникам сравниваемых напряжений, а эмиттеры через резисторы - к выходу блока опроса, дополнительные транзисторы, базы которых подключены к коллекторам транзисторов балансного усилителя, и вспомогательные усилительные каскады, выходы которых связаны с формирователями, отличающееся тем, что, с целью повышения быстродействия, точности и чувствительности устройства, коллекторы дополнительных транзисторов перекрестно соединены с эмиттерами транзисторов балансного усилителя, а эмиттеры дополнительных транзисторов подключены ко входам соответствующих вспомогательных усилительных каскадов.

Выход 1

1

Вы ход 2

Вход2

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для СРАВНЕНИЯ | 1970 |

|

SU269223A1 |

| СХЕМА СРАВНЕНИЯ | 1968 |

|

SU221773A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С СИММЕТРИЧНОЙ НАГРУЗКОЙ | 2009 |

|

RU2394361C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ВХОДНЫМ СОПРОТИВЛЕНИЕМ | 2009 |

|

RU2393628C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2012 |

|

RU2504896C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2346386C1 |

| КОМПЛЕМЕНТАРНЫЙ ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2012 |

|

RU2510570C1 |

| Усилитель | 1974 |

|

SU523510A1 |

| Дифференциальный операционный усилитель | 1974 |

|

SU515251A1 |

| БАЛАНСНАЯ СХЕМА СРАВНЕНИЯ! | 1970 |

|

SU267209A1 |

Авторы

Даты

1975-02-05—Публикация

1973-04-26—Подача