1

Изобретение относится к области изм&.рительной техники.

Известен цифровой частотомер, работа которого основана на двухступенчатом

методе измерения низкочастотных сигналов

Известный цифровой частотомер содер- жит декадный счетчик отношения тактовой

:И измеряемой частот, декадный счетчик импульсов тактовой частоты (пересчетная схема), декадный счетчик времени изме; рения импульсов тактовой частоты и умножитель частоты, связанный шинами у№равления с параллельными выходами счетчика отношения частот, частотными вхо- ; дами с выходами счетчика импульсов

тактовой частоты, а выходом - с входом счетчика времени. Счетные входы счетчика отношения частот, счетчика тактовой частоты и выход счетчика времени связаны со схемой синхронизации и управпения,

Недостатками известного частотомера, является довольно узкий частотный диапазон и сложная конструкция.

Для расширения частотного диапазона

и упрощения предлагаемый частотомер снабжен двумя счетчиками - регистрами сдвигающими, декадным управляекоым дв лителем частоты, реверсивным счетчиком с кодером и схемой ИЛИ, причем nejvвый счетчик - регистр сдвигающий, промежуточный регистр с включенными на входах вентилями переноса кодов, декадный управляеклый делитель частоты и счетчик-регистр сдвигающий соедин ены последовательно, выходы счетчиков-р&гистров сдвигающих подключены к входам реверсивного счетчика, выходы ключевых схем соединены с входами счетчиков-регист ров сдвигающих, выход схемы ИЛИ подключен к входу одного из счетчиковрегистров, а входы - к выходу схемы выделения целого числа периодов измеряв мой частоты и к выходу декадного управрляемого делителя соответственно.

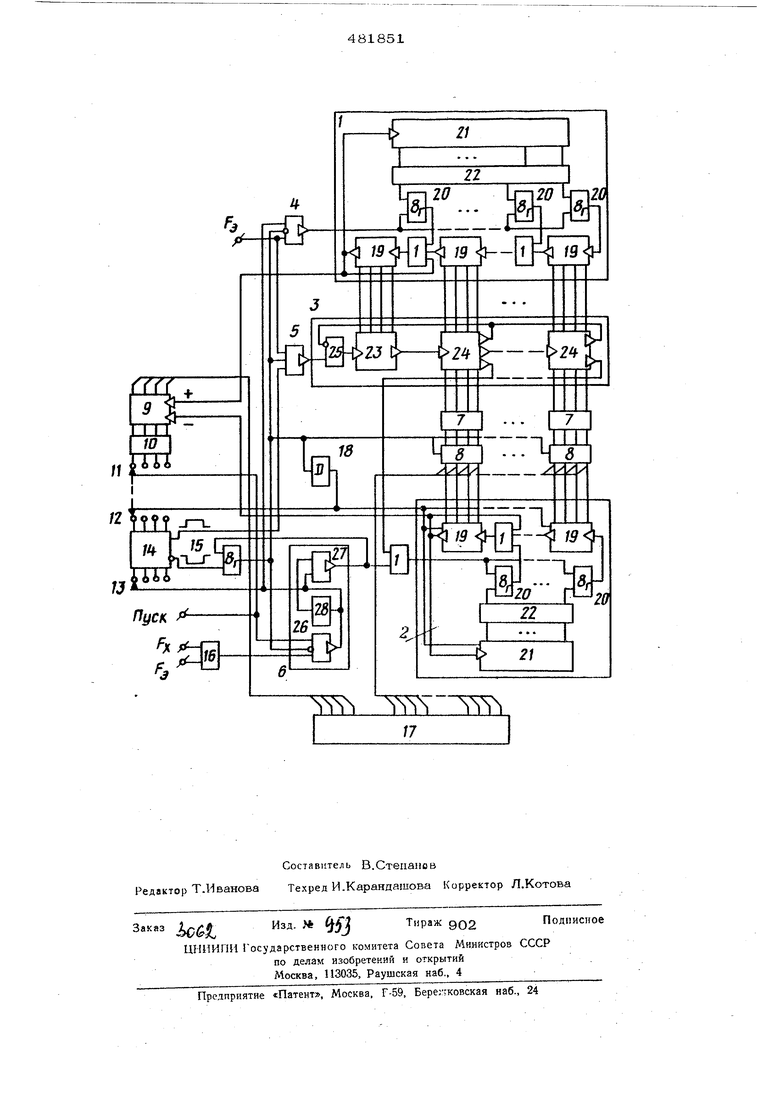

На чертеже приведена функциональная схема цифрового частотомера.

Частотомер состоит из счетчиков-р&гистров 1 и 2 сдвигающих, управляемого делителя 3 ключевых схем 4 и 5, схемы

6 выделения цепого числа периодов измеряемой частоты, промежуточного регистра 7, вентилей 8 переноса кодов, реверсивного счетчика 9, кодера Ю, переключателей 11, 12 и 13, счетчика времени 14, вентиля 15, схемы 16 синхронизации, блока 17 цифровой индикации, результатов измерений и указания положения запятой и элемента 18 задержки. Каждый из счетчиков-регистров сдвигающих содержит декадный счетчик 19, вентили 20, двоичный счетчик 21 и декодер 22. Управляемый делитель содержит однодекадный управляемый делитель 23, декадный умножитель 24 и схему запрета 25. Схема выделения нелого числа периодов содержит ключевые схемы 26,27 и элемент 2 8 задержки (схемы ИЛИ на чертеже обозначены).

Работает частотомер следующим образом. С приходом импульсного сигнала Пуск частотомера открывается ключевая схема 26 схемы 6.выделения целого числа периодов и одновременно в реве| сивиый счетчик 9 с выходов кодера 1О записывается двоичный код числа

R , m-k -г ,

где fn -число десятичных разр5щов счетчика-регистра 2; Ц,, - натуральное число или нуль,

определяемые положением переключателя 11.

Импульсы измеряемой частоты F; с выхода схемы 16 синхронизации начинают поступать через управляемый вход ключевой схемы 26 на выход этой схемы. Схема 16 синхронизации реализует привязку импульсного асинхронного сигнала измеряемой частоты FX к импульсам эталонной частоты Fg , а также обеспечивает синхронную работу основных узлов частотомера. Первый импульс, появившийся на выходе ключевой схемы 26, открывает ключевую схему 27. Так как время задержки импу/пьсных сигналов элементом 28 задержки больше длительности импульсов, поступающих с выхода ключевой схемы 26, первый и myльc на выход ключевой схемы 2 7 не проходит.

Импульсы с выхода ключевой схемы 26 через дополнительный выход схемы

6 выделения целого числа периодов посту-

пают также на управляющий вход ключевой схемы 4 и через пepeключaтeлt 13- а соответствующий вход установки времени- измерения и пуска счетчика 14 времени. Первый импульс, появившийся на ополнительном выходе схемы 6 выделения целого числа периодов, запускаетJ

счетчик 14 времени, открывает ключевую схему 4, с выхода которой на вход счетчика-регистора 1 начинают поступать импульсы эталонной частоты Fg На иин версном выходе счетчика 14 времени . появляется отрицательный импупьснопотенциальный сигнал длительностью

iKi

СТ.

1-10

сек

t,

где К - натуральное число или-нуль.

определяемые положением переключателя 13. Этот сигнал поступает на управляк щий вход вентиля 15, вследствие чего вентиль 15 закрывается. Второй и последующие импульсы частоты р;( с выхода ключевой схемы 26 через упра&ляемый вход ключевой схемы 27 поступают на основной выход схемы выделения целого числа периодов и далее на управляемый вход вентиля 15 и на счетный вход счетчика-регистра 2. По истечении временного интервала Т на инвероном выходе счетчика 14 времени появляется положительный импульсно-потенциальный сигнал, вследствие чего вентиль 15 открывается. Очередной импульс, появивщийся после прекращения работы счетчика времени на осповнок выходе схемы 6 выделения целого числа периодов, проходит через открытый вентиль 15 на запрещающие входы ключевой схемы 4 и схемы 6 выделения целого числа периодов, на первый управляющий вход ключевой схемы 5 и на управляемые входы вентилей 8 переноса кодов, вследствие чего ключевая схема 4 и схема 6 выделения целого числа периодов устанавливаются в исходное состояние, ключевая схема 5 подготавливается к работе и производится перенос содерисимого счет-

чика-регистра 2 в промежуточный регистр 7.Пусть в N/гомент появления импульса на выходе вентиля 15 на вход счетчикарегистра 2 пройдет И импульсов (tt -

число полных периодов частоты , В

этом случае ключевая схема 4 будет от,- крыта, в течение временного интервала t сек, и следовательно, на вход счетчика-регистра 1 пройдет

. N, tr3 n

импульсов эталонной частоты F

Счетчики-регистры 1 и 2 реализуют операции счета импульсов и сдвига результатов счета. В исходном состоянии счетчика-регистра 2 с первого выхода декодера 22 поступает сигнал, соответ ствующнй коду . Вентиль 20, выход которого подключен к входу старщего разряда m - раэрадного декадного счетчика 19, будет открыт, а остальные вентили 2 О будут закрыты сигналами, соот ветствующнми коду О. Импульсы источника счетных импульсов начинают поступать через управляемый вход открытого вентиля на счетный вход старшего разряда декадного счетчика 19. Импульс переполнения декады старшего разряда счетчика 19 поступает на счетный вход этой же декады и на счетный вход счетчика 21. Счетчик 21 фиксирует число переполнений , декады старшего разряда счетчика 19, следовательно, после L -го переполнения декады старшего разряда счетчика 19 источник счетных импульсов будет подклю чен к счетному входу ГЛ-i- го разряда этого счетчика, -Старший разряд любого числа, записанного в счетчике 19, всегда будет находиться в старшем разряде этого счетчика, следовательно, результат счета числа периодов измеряемой частоты F будет представлен в счетчике 19 счетчика-регистра 2 в следующем виде: . р - число десятичных разрядов числа Ц . Так как число десятичных разрядов счетчика-регистра 1 равно (Ш +1), то очевидно, результат счета счетчиком числа периодов эталонной частоты Fn будет пре ставлен в счетчике 19 счетчика-регистра 1 в виде числа nFj г где S - число десят1гчных разрадов числа N , К момеьту окончания работы счетчиков-регистров 1 и 2 с выходов декад старших разрядов этих счетчиков на сум- мируюший и вычи1аюи ий входы реверсиБного счетчика 9 поступит соответственно (S-1) и (Г-1) импульсов, следовательн в реверсивном счетчике 9 будет зафикс1ьровано число ,+ {S-1)-lr-l))7H-s-r-K2,-Z . После переноса числа Q в промежуточный регистр 7 на кодовые входы управляемого делителя 3 будут поступать сигналы, соот ветствующие двоично-десятичным кодам чисел Р и О, . Принцип действия управляемого делите 3, образованного уп1:)авляемым олнодекадным делителем 23 с включенной на входе схекюй 25 запрета, а на выходе последовательно включенными однодекадными умн жителями 24, заключается в следуюшем. Числа, зафиксированные в счетчике-регист ре 1 и промежуточном регистре 7, можно записать в виде многочленов P., 10 -..F, tn-Z10 10 -.., ,lO Mm.. 0«(i49 , где Р-и О- - числа, представленные двоично-десятичными кодами в i -ьсс декадах счетчика-регистра 1 и промежу- точного регистра 7. Каждая декада умножителя имеет два основных и один вспомогательный выходы и реализует следуюшие взаимно независимые коэффициенты умножения, заданные i Правильной дробью Р-К - г-ю Частоты на первом и втором основных и вспомогательном выходах умножителя будут соответственно равны .Г 10 Вх К,Г л I ВХ 10 ВЫХ.Э 3 8Х-10 ВХ где Р - частота на входе однодекадного умножителя. Так как вспомогательный выход каждой предыдущей декады умножителя 24 соединен с входом каждой послсдуюшей декады, а выходы выдачи кодов fn младших разрадов {ТП 1) разрядного счет чика-регистра 1 и выходы выдачи кодов Ш разрядного промежуточного регистра 7 подключены к входам приема кодов соответствуюших декад умножителя, то обшие коэ4)фициенты умножителя будут равны IT1-11 „ ( iitiJO i:ilZili- M- 10 1,io .,.- -aiioMoo a частоты повторения импульсов, поступаюших с объединенных первых и объединенных вторых выходов умножителя, будут соответствовать значениям FflblX. ВЫХ.Д2Э ВЫХ.Д15 вых va va ebixAas ю ,д23

7

где БЫх.Д.23 частота повторения импульсов на выходе однодекадного делителя 23,

Первые выходы декадного умножителя

24подключены к входу запрещения Ьхемы

25запрета, реализующей операцию вычитания частот, следовательно, с выхода запрета на вход однодекадного делителя 23 импульсы будут поступать

с частотой повторения, равной

.F.

, ftK L4fe

.дгэ .yi вх.АЗ Q вы)(.А23,

где РВХ.Д.З - частота повторения импульсов на входе управляемого делителя 3; 5вх.д.23- частота повторения импульсов на входе однодекадного делителя

23.

Так как выходы выдачи кодов декады

старшего разряда счетчика-регистра 1 подключены к входам приема кодов однодекадного управляемого делителя 23, то коэ4|фициент деления делителя 2 3 будет равен числу Pfj , а частота повторения импульсов, поступающих с выхода этого делителя на вход умножителя 24, будет

равна

вх.дгз

вых дгз

m

Hjm, учитывая, что

m

Р-РтЮ

8Х.дЗ

ВЫХ А23

гп

10

МОЖНО записать

,tri

.даз Р вх.дз

Частота повторения импульсов, поступающих и объединенных вторых выходов умножителя 24, т.е. с выхода управляющего делителя 3, будет равна

р- V f- т

.АаЗ

Вых.р,3 .A-i - Р

вх.дз

3 реализует следовательно, делитель

дробный коэффициент деления вида - 1, числитель и знаменатель которого пре-д- ставлены двоичко-десятичными кодами. Очевидно, что после переноса в промежуточный регистр 7 содержимого счетчикарегистра 2, коэффициент деления управляемого делителя 3 автоматически устанав Гэ .

K-L-ii

ливается равным

n Выходной импульсный сигнал вентиля 15 через элемент 18 задержки поступает также на выходы гашения декад счетчикарегистра 2 и через переключатель 12 на .выходы установки времени измерения и пуска счетчика времени 14. Счетчик8

регистр 2 устанавливается в исходное положение и запускается счетчик врюмени, причем на прямом выходе счетчика времени появляется положительный потен- Шiaльн -иvпyльcный сигнал длительностью

-IS о

где к„ - натуральное

число или нуль, определяемые положением переключателя 12. Этот сигнал поступает на второй управляющий вход ключевой 10 схемы 5, вследствие чего источник эта- лонной частоты через управляемый вход этой схемы подключается к :&ходу управляемого делителя 3. Очевидно, что частота повторения импульсов, поступающих 15 с выхода управляемого делителя 3 на вход счетчика-регистра 2, будет равна

РЭ О,s-r-1

Вых.АЗ к7 р fЭ FX

0 Ключевая схема 5 находится в открытом соегоянии в течение временного интерваiia , следовательно, на вход счетчикарегистра 2 пройдето п I- 1 (У -Т Г -Т 1Л -а вых.A3 л

5 импушзсов. Результат счета в счетчикерегистре 2 фиксируется в виде числа .- )-г fS-1

N3 Ю .

где t - число десятичных разрядов числа 0 NO моменту окончания работы счет-чика-регистра 2 с выхода декады старшего разряда этого счетчика на вычитаюший BSSOJ реверсивного счетчика 9 поступит ( I - 1) импульсов, вследствие чего в реверсивном 5 счетчике 9 будет зафиксировано число

() s-l-Ki-f-l .

Так как кодовь1е выходы счетчикарегистра 2 и реверсивного счетчика 9

0 подключены к входам приема кодов блока 17 индикации результатов измерений и указания, положения запятой, резуль таты измере1Шй частоты F будут представлены на цифровом табло блока 17

5 индикации в виде десятичного кода числа

m-i-s-i-Kz

FX-IO

X VJ

а положение заляч1;й будет зафиксировано перед ( fTi-bfi - L- - f - 1 ) младшими разрядами этого же .числа.

0 Частотомер позволяет производить измерения с точностью до S - (Г- 1) знака после запятой, причем положение старщего разряда результата измерений фиксируется в старшем разряде блока циф5 ровой индикации.

Предмет изобретения

Цифровой частотомер, содержащий переключатели, переключаемый счетчик

времени, блок цифровЪй индикации разута татов измерений и указания положения запятой, схему выделения целого числа периодов измеряемой частоты, схему синхронизации, промежуточный регистр , с включенными на входах вентилями переноса кодов, две ключевые схемы, ; вентиль и элемент задержки, от ли- чающийся тем, что, с целью раог ширешш функциональных возможностей и упрощения, он снабжен двумя сче-р чикам№ регистрам0 сдвигающими, декад ным ущшвляемым Целителем частоты, реверсивным счетчиком с кодером и схемой ИЛИ, причем первый счетчик

регистр сдвигающий, хфомеядггочный регистр с включенными на входах вен-, тилями переноса кодов, декадный управляемый делитель частоты и второй счетчикрегистр сдвигающий соединены последовательно, выходы счётчиков-регистров сдви гающих подключены к входам реверсивного счетчика, выходы ключевых схем соединены с входами счетчиков-регистров сдвигающих, выход схемы ИЛИ подклю- чен к входу одного из счетчиков-регис-пров, а входы-к выходу схемы выделения целого числа цериодов измеряемой чаототы и к выходу декадного управляемого делителя частоты соответственно. Т .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления логарифмов | 1972 |

|

SU479110A1 |

| Цифровой частотомер | 1973 |

|

SU447637A1 |

| Цифровой измеритель средней частоты | 1977 |

|

SU705360A1 |

| Устройство для контроля метрологических характеристик средств измерений | 1982 |

|

SU1117592A1 |

| Аналого-цифровой преобразователь считывания | 1977 |

|

SU677097A1 |

| Цифровой измеритель средней частоты | 1980 |

|

SU920555A2 |

| УПРАВЛЯЕМЫЙ ДЕКАДНЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1970 |

|

SU270354A1 |

| ВСЕСОЮЗНАЯ | 1973 |

|

SU370702A1 |

| ЦИФРОВОЙ ЛИНЕЙНО-КРУГОВОЙ и ЭЛЛИПТИЧЕСКИЙ | 1966 |

|

SU184528A1 |

| Устройство для измерения отношения частот | 1983 |

|

SU1147997A1 |

Авторы

Даты

1975-08-25—Публикация

1973-10-05—Подача