1

Изобретение относится к области импульсиой техники, а именно, к преобразователям кода в аналог и может найти применение в вычислительной технике и в коитрольно-измерительиой аппаратуре.

Известио устройство для преобразования цифрового кода во временной интервал, содер кан1ее генератор кванту1ОН1ей последовательности, схему «ИЛИ и схему совпадепия, к входам которой подключены счетчик и регистр кода, а к выходу - линия задержки.

Иедостатком такого устройства является низкая точность преобразования кода во временной интервал.

С целью повышения точности нреобразова1П1Я в устройство введен многоканальный входной блок, содержап1,ий секционированиую линию задержки и в каждом канале схему «И, два триггера и схему «ИДИ, причем 15ыход генератора кваптуюн1ей последовательности подключеп к первому входу схемы «И первого капала и к входу секционироваипой лииии задержки, выходы которой соединепы с первыми входами схем «И других каналов, второй Н третий входы схем «И каждого каиала нодключепы соответственно к прямому выходу первого триггера и инверсному выходу второго триггера этого же капала, первые входы триггеров всех капалов соедппены с клеммой «Сброс преобразователя, вторые

входы первых триггеров всех капалов подключепы к клемме «Запуск устройства, второй вход второго триггера каждого капала через схему «ИЛИ этого же капала соедииеп с выходами схем «И других каналов, приче.м выходы схем «И всех капалов подключены к входу счетчика через схему «ИДИ.

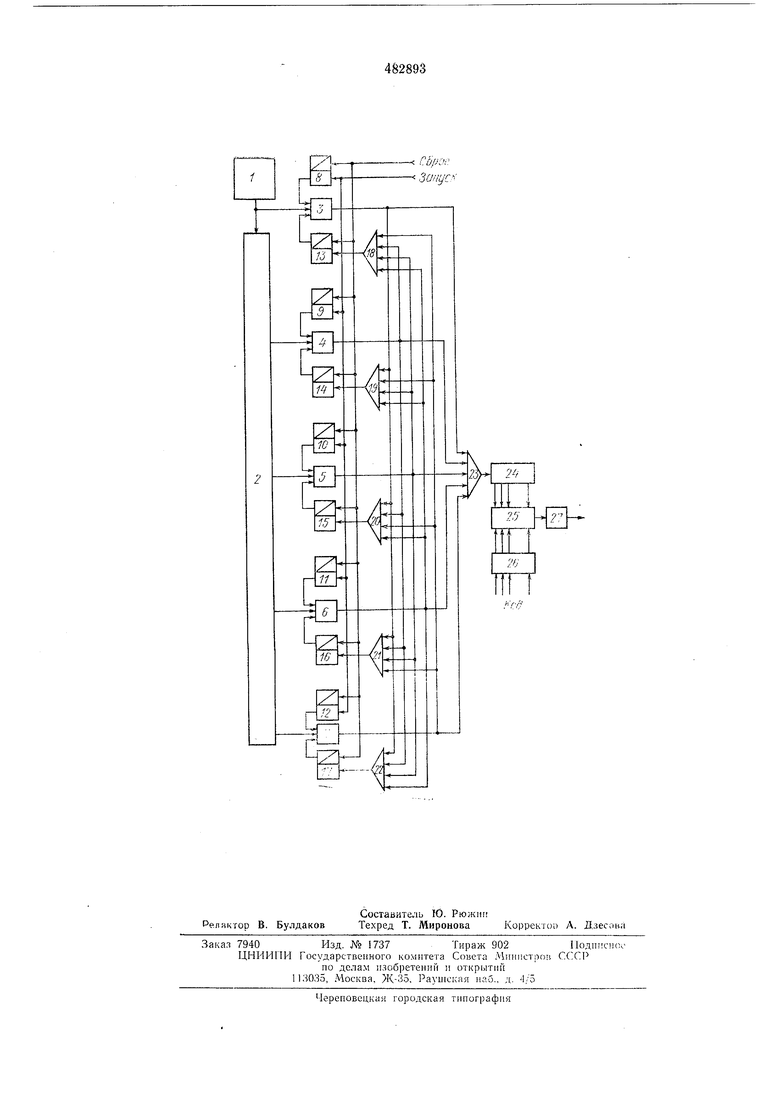

Фупкциопальпая схема преобразователя цифровой код-вpe eнlioй иитервал представлена па чертеже.

Преобразователь содержпт генератор 1 квантующей последовательпостп, выход которого непосредствеппо и через отводы лииии задержки 2 подключен к первым входам

схем «И 3-7 многоканального входного блока. Вторые и третьи входы схем «И 3-7 управляются двумя группами трнггеров 8-12 и 13-17. Ири этом в каждом каиале второй вход схемы «И соединен с прямым выходом

триггера первой группы 8-12, соответствующего данному каналу, а третпй схемы ипверсиым выходом соответствующего триггера второй группы 13-17. Все триггеры первой группы 8-12 управляются по иервым

входам импульсами «Сброс, а по вторым входам-импульсами «Запуск преобразователя. В триггерах второй группы 13-17 все первые входы управляются импульсами «Сброс, а второй вход триггера каждого капала подключеп к выходу одпой пз схем «ИЛИ 18-22, соответствующей данному каналу. В каждом канале схем «ИЛИ 18-22 соединены с выходами схем «И 3-7 другнх каналов. Выходы всех схем «И 3--7 объединены также схемой «ИЛИ 23, выход которой нодключеи к счетному входу счетчнка 24 импульсов. Разрядные выходы счетчнка 24 соединены с входами схемы 25 совнадения, другие входы которой нодключены к разрядным выходам регистра 26, хранянгего нреобразуемый код. 13ыход схемы 25 совнадения соединен с входо.м рег лируемой линин задержки 27. Иреобразователь работает следующим образом. Генератор I квантующей носледовательиости совместно с секционированной .п-пшей задержки 2 фор.мируют на своих выходах носледовательности импульсов, сдвинутые во времени друг относительно друга на дискрет преобразования. Эти последовательности импульсов, число которых равно числу каналов входного блока, поступают на нервые входы соответствующих схем «И 3-7. В исходно.м состоянии схемы нреобразователя, в которое она устанавливается и.мпульсом «Сброс, на все схемы «И 3-7 с нрямых выходов триггеров нервой группы 8 - 12 подаются сигналы запрета, а с инверсных выходов триггеров второй груниы 13-17 -- сигналы разрешения. Следовательно, все схемы «И 3-7 ие пропускают импульсные последовательности, поступающие на их первые входы. В момент нодачи нмпульса «Запуск триггеры первой группы 8-12 переключаются н дают разрещение на все схемы совпадения 3-7. После первого же совнадения в любом из каналов, т. е. после появления первого же импульса на выходе схемы «И любого капала, на выходах схем «ИЛИ 18-22 остальных каналов формируются импульсы, которые переключают соответствующие им триггеры второй группы 13-17 и, следовательно, устанавливают на входах соответствующих схе.м «И 3-7 сигналы занрета. Такнм образом, происходит выбор канала, в которо.м совпадение во времени импульса «Запуск и нмпульса кваитующей последовательиостн произошло с точностью не хуже дискрета нрсобразования. Выходные импульсы выбранного кана.1а через схему «ИЛИ 23 поступают на счетный вход счетчнка 24 и.мнульсов. В момент равенства содержимого счетчика 24. и регистра 2() схема 25 совпадення формирует и.мпульс, который проходит через линию задержки 27 и является выходным импульсом преобразователя. Интервал времени между имнyльco «Запуск и выходным импульсом преобразователя пропорционален преобразующему коду. Иосле выдачи преобразователем В1 1ходного импульса иа вход преобразователя поступает импульс «Сброс, который устанавливает схему в исходное состояние для очередного преобразования. Дальнейшее увеличение точности нреобразоваиия в предложенно.м преобразователе достигается за счет увеличения чнсла капало входного блока. И р е д м е т изобретения Иреобразователь цифровой код - временной интервал, содержащий генератор квантующей последовательности, схему «ИЛИ и схему совпадения, к входам которой подключены счетчик и регистр кода, а к выходу - задержки, отличающийся тем, что, с целью повышения точности преобразования, в него введен многоканальный входной блок, содержащий секционированную линию задержки и в кажодм канале схему «И, два триггера и ехему «ИЛИ, причем выход генератора квантующей последовательности подключен к нервому входу схемы «И первого канала и к входу секционированной линии задержки, выходы которой соедииены с первыми входами схем «И других каналов, второй и третий входы схем «И каждого канала подключены соответственно к прямому выходу первого триггера и инверсному выходу второго триггера этого же канала, нервые входы триггеров всех каналов соединены с клеммой «Сброс преобразователя, вторые входы иервых триггеров всех кана,дов подключены к клемме «Запуск устройства, второй вход второго триггера каждого канала через ехему «ИЛИ этого же капала соединен с выходами схем «И других каналов, причем выходы ехем «И всех каналов подк,гпочены к входу счетчика через схему «ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель однократных временных интервалов | 1974 |

|

SU571787A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В ЦИФРОВОЙ КОД | 1966 |

|

SU189628A1 |

| УСТРОЙСТВО для ОТНОСИТЕЛЬНОГО ПЕРЕКОДИРОВАНИЯ | 1972 |

|

SU331496A1 |

| Устройство для передачи информации с обратной связью | 1986 |

|

SU1322356A1 |

| Дискретный умножитель частоты следования импульсов | 1973 |

|

SU446879A1 |

| Устройство задержки | 1974 |

|

SU606199A1 |

| Многоканальный генератор импульсов | 1974 |

|

SU516183A1 |

| УСТРОЙСТВО для РАСЧЕТА СЕТЕВЫХ ГРАФИКОВ И МОДЕЛИРОВАНИЯ СЕТЕЙ МАССОВОГО ОБСЛУЖИВАНИЯ | 1970 |

|

SU284435A1 |

| АДАПТИВНЫЙ КОММУТАТОР СИСТЕМЫ ТЕЛ ЕИЗМЕРЕН ИИ | 1973 |

|

SU407376A1 |

| ЦИФРОВОЙ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU297071A1 |

Авторы

Даты

1975-08-30—Публикация

1973-03-21—Подача