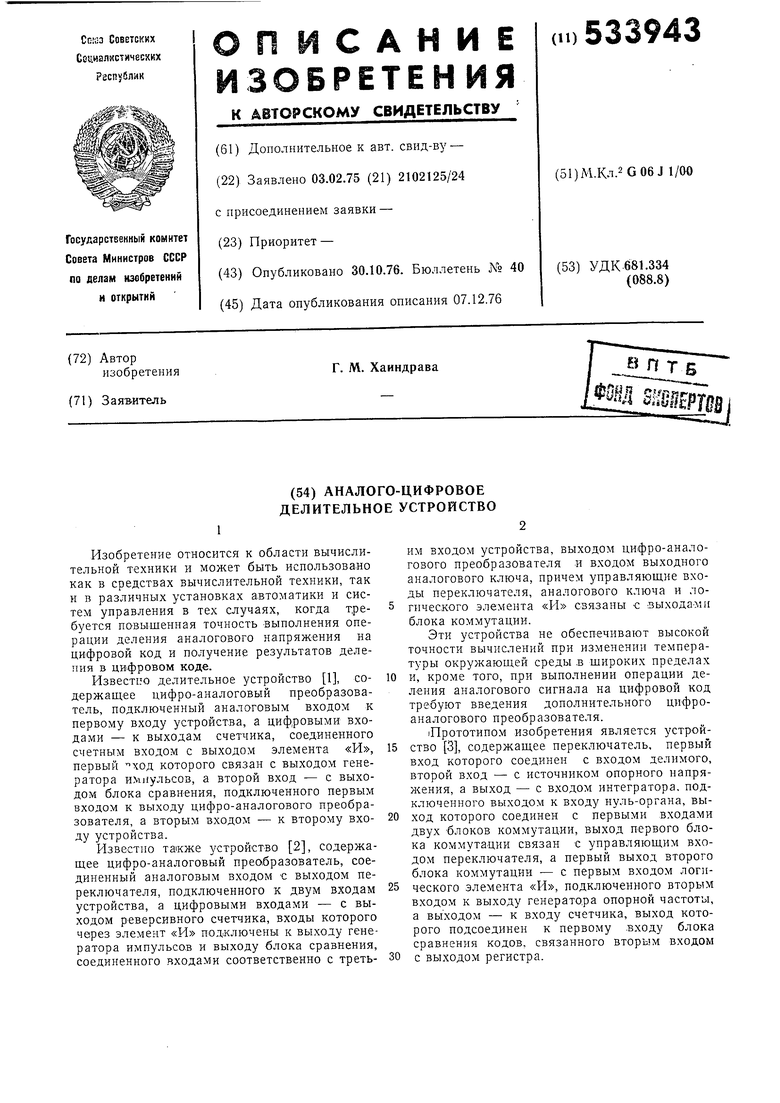

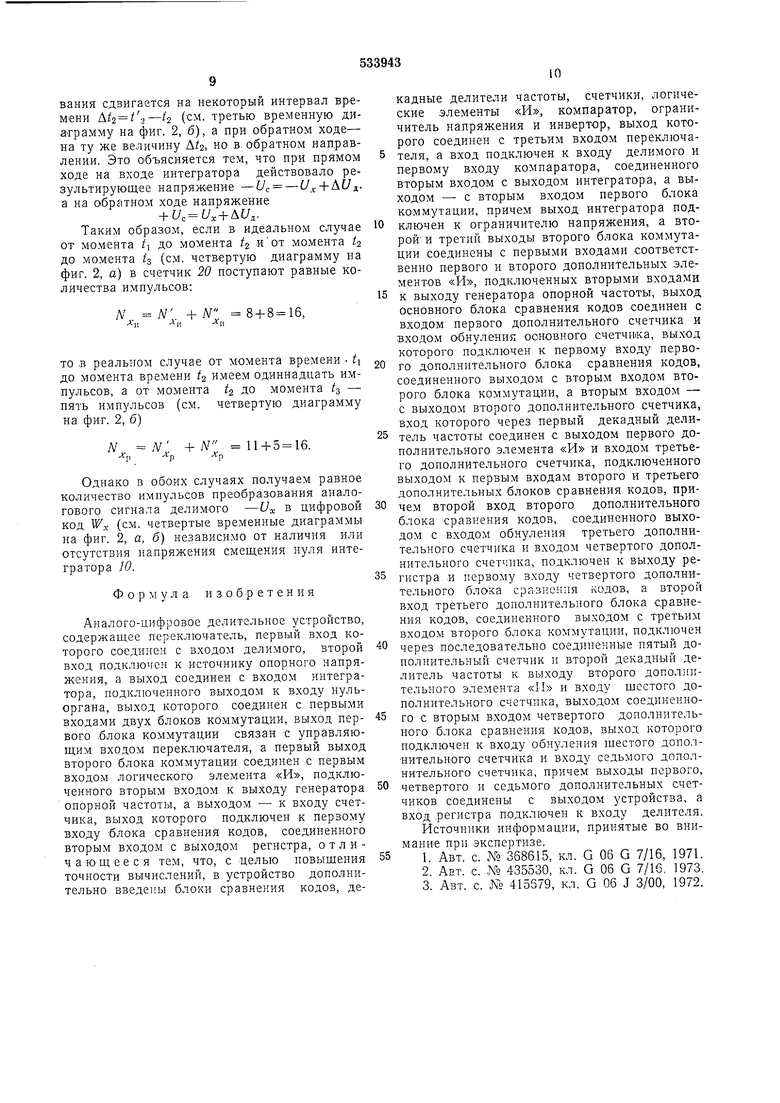

Такое устройство та,кже не позволяет повысить тоЧ:НОсть вычислений лрн изменении температуры окружающей среды в широких пределах и требует для ввода сигнала делителя в цифровой форме дополнительного цифро-аналогового преобразователя. Цель Изобретения - повышение точности вычислений. Это достигается тем, что в аналого-цифровое дел.ительное устройство допол.нительно введены блоки сравнения кодов, декадные делители частоты, счетчи.ки, логические элементы «И, компаратор, ораничитель напряжения и инвертор. Выход инверто ра подключен к третьему входу переключателя, а вход - к .входу делимого и первому входу компаратора, соединенного вторым входом с выходом интегратора, а выходом - с вторым входом первого блока коммутации. Выход интегратора подключен к ограничителю напряжения, а второй и третий выходы второго блака коммутации - К первыМ входам соответственно первого ,и второго дополнительных элементов «И, связанных вторыми входами с выходОМ генератора опорной частоты. Выход основного блока сравнения кодов соединен с входом первого дополНительного счетчика и входом обнуления основного счетчика, выход которого подключен к нервОМу входу первого дополнительного блока сравнения кодов, соединенного выходом с вторым входом второго блока коммутации, а вторым входом - с выходом второго дополнительного счетчика, вход .которого через первый декадный делитель частоты связан с .выходо-м перового допол.нительного элемента «И ,и входом третьего дополнительного .счетчкка, нод1ключенного выходом к нервЫМ входа м второго н третьего дополнительных блоков сравнения кодов. Второй вход второго дополнительного блока сравнения кодов, соединенного выходом с входом обнуления третьего дополнительного счетчика и входом четвертого дополнительного счетчика, подключен к выхо.ду регистра и первому входу четвертого дополнительного блока сраВНе1г.ия кодов, а второй вход третьего допол:нительного блока сравнения .кодов, соединенного выходом с третьим входом второго блока KOMiMyTauHM, через последовательно соединенные нятый дополнительный счетчик и второй декадный делитель чаетоты - к выходу второго дополнительного элемента «И и входу шестого дололпительного счетчика, выходом соединенного с вторым входом четвертого дополнительного блока сравнения кодов, выход которого лодключен к Входу обнуления шестого дополнительного счетич.ка и входу седьмого донолнительното счетчика. Выходы нервого, четвертого и седьмого дополнительных счетчико.в соединены с выходом устройства, а вход регистра подключен к входу делителя. На фиг. 1 представлена функциональная схема аналого-цифрового делительного устройства; на фиг. 2 - временные диаграммы, поясняющие осуществленпе термоко-мпенсаЦ;Ии В устройстве. Ана.лого-|Цифровое делительное устройство (см. фиг. 1) содержит переключатель /, первый вход-1колтакт 2 переключателя, клемму 3 для -подключения источ-ни.ка Онорного напряжения (постоянного то;ка положительной поляр.ности), второй .вход-контакт 4 переключателя, вход 5 делимого, компаратор 6, инвертор 7, третий вход-контакт cS переключателя, подвнжиый контакт 9 (управляющий ВХОД) переключателя, интегратор 10, ограничитель // нанряжен.ия, .клемму 12 для подключения источника напряжения смещения (постоянного тока отрицательной полярности), нуль-орган 13, первый 14 и второй /5 блоки коммутации, осно.вной логический элемент «И 16, первый 17 и второй 18 дополнительные логические элементы «И, генерятор 19 опорной частоты, основные счетчик 20 и блок 21 сравнения кодо.в, регистр 22, клеммы 23 для параллельного ввода цифрового кода делителя, первые дсшолнительные счетчнк 24 и блок 25 сравнения кодов, второй дополнительный счетчик 26, первый декадный делитель 27 частоты, третий дополнительный счетч.ик 28, второй 29 .и третий 30 дополнительлые блоки сравнения кодов, четвертые дополнительные счетчик 31 и блок 32 сразпения кодов, пятый дополнительный счетчик 33, второй декадный делитель 34 частоты, шестой 35 и седьмой 36 дополнительные счетчики, б ток 37 цифровой индикации, клеммы 38 для вывода цифровых кодов результата (частного), клемму 39 для вывода сигнала «Конец цикла решения, клемму 40 для ввода импульса «Пуск и 1ХНОПКУ 41 «Сброс. Контакт 2 лереключателя / соеди;1еп с клем1мой 3 для подключения источника опорного папряження, а контакт 4 - с входом 5 делимого, с первым входом компаратора 6 и с входом инвертора 7, выход которого связан с третьим входом (контактом) 8 переключателя }. Подвижный контакт (управляющий вход) 9 .иереклгочателя 1 подключен к входу интегратора 10. Выход интегратора 10 одновременно связаи с вторым входом ко.мпаратора 5 и с ограпичителем // иапряжения, состоящего из полупроводннкового диода и клеммы 12 для подключения источника иапряжения смешения (постоянного тока отрицательной полярности), а также входом нульоргана 13. Выход нуль-органа подключен к первым входам блоков 14 и 15 :KOMмутации, а выход компаратора 6 - к второму входу блока 14, выход (которого связан с лодвижньгм контактом 9 переключателя 7. Первый выход блока 15 соединен с первым входом основного логического элемента «И 16, а второй и Третий выходы - с первыми входами дополнительных логических элементов «И 17 и 18. Вторые входы логических элементов «И 16, 17 и 18 подключены к выходу генератора 19 о.иорной частоты, выход условного логического элемента «И 16 - к входу основого Счетчика 20, а выход этого -счетчика - К первому входу основного блока 27 сравнения кодов, соединенного -вторым входом с выходом регистра 22, к .входу которого доключены клеммы 23 для параллельного Ввода цифрового кода делителя. Выход основного блока 21 сравнения -кодов соединен с входом дололнительного счетчика 24 и выходом обнуления основного счетчика 20, выход которого подключен к первому входу дополнительного блока 25 сравнения кодов, .соединенного выходом с вторым входом блока 15 коммутации, а вторым входом - .с .выходом дополнительного счетчика 26. Вход счетчика 26 через декадный делитель 27 частоты связан с выходом дополнительного логического элемента «И 7-7 и входом дополнительного счетчика 28, а выход счетчика 25 с первыми .входами дополнительных блоков 29 и 30 сравнения кодов.

iBTOpoft вход дополнительного блока 29 сравиепия кодо.в, соединенного выходом с входом обнуления дополнительного счетчика 28 и входом дополнительного счетчика 31, подключен к .выходу регистра 22 и первому входу дополнительного йлока 32 сравнения кодов, а второй вход дополнительного блока 30 сравнения кодов, соединенного выходом с третьим входо-м блока ,15 коммутации, через последовательно соединенные дополн.ительный счетчик 33 .и декадный делитель 34 частоты - к выходу дополнительного логического элемента «И 18 и входу дополнительного счетчика 55. Выход счетчика 55 связа-н с вторым входом блока 32 сравнения кодов, выход которого подключен к .входу обнуления счетчика 35 и вхо-ду счетчика 36, а выходы счетчиков 24, 31 и 36 - с блоком 37 цифровой .индикации и клеммами 38 для вывода цифровых .кодов результатов (частных). Выход блока 30 сравнения кодов подсоединен к кле.мме 39 для вывода сигнала «Конец цикла решения. Клемма 40 ввода импульса «.Пуск подсоединена к третьему входу блока J4 коммутации и к шинам обнуления счетчиков 20, -.24, 26, 28, 31, 33, 35, 36, а кнопка 41 подключена к входам :блоков 14 и 15 коммутации.

.Аналого-цифровое делительное устройство работает следуюшим образом.

После включе}1ия источников питания и однократйого нажатия на кнопку «Сброс схема устройства ириходит в исходное состояние, при котором подвижный контакт 9 переключателя 1 находится в соприко-сновении с контактом 2 и опорное напряжение +t/on подается на вход .интегратора 10. На выходе интегратора с помошью ограничителя // напряжения поддерживается уровень отрицательного напряжения -Ьс.,- Данное напряжение действует на вход компаратора и на вход нуль-органа 13, на выходах которых по-ддерживаются нулевые уровни -напряжения.

Цикл деления начинается после прихода

через клемму 40 .импульса «Пуск под действием которого счетчики сбрасываются в нулевое состояние, а блок 14 коммутации переключает подвижный Контакт 9 с контакта 2

на контакт 4, в результате чего на вход интегратора 10 с входа 5 делимого лостулает аналоговый сигнал делимого отрицательной полярности - Их- На выходе интегратора напряжение начинает увеличиваться. В момент

пересечения нулевой оси интегрирующим напряжением на выходе нуль-органа 13 образуется иашульс, .который воздействует на входы блоков 14 и 15. На .выходе блока 14 под действием .данного импульса сиг;1ал не образуется, а иа первом выходе блока /5 появляется сигнал, который воздействует на первый вход элемента «11 16 и отп1фает его. С выхода генератора 19 опорной частоты через элемент «Н 16 и вход «Счет в счетчик

20 проходят импульсы. После очередного сра.внения записанного числа в счетчике 20 с Ц1:фровым кодом, записанным в регистре 22, на выходе блока 2/ сравнения кодов образуются импульсы, которые с одной стороны

подаются на -шину об-нуления счетчика 20 и сбрасывают его, а с другой стороны - на счетный вход счетчика 24, где они накаиливаются.

Напряжение положительной полярности

на выходе интегратора 10 линейно нарастает до уровня напряжения отрицательной полярности си-гнала дел 1мого -f/., который сравнивается на входе компаратора 6 с напряжением с выхода интегратора 10. В момент разенства - L/д. -f Ь-,,,,.,.(/) на выходе компаратора 6 образуется импульс, который подается на вход блока 14 коммутации. На выходе его вырабатывается сигнал, воздеи-:твуюший на подвижный контакт 9 переключателя 1, который переключается с второго входа (4) на третий вход (8). С выхода инвертора 7 напрял с;;ие делимого положитель.ьой полярности + L/д- подастся на вход интегратора 10. В результате направление процс-:са

интегрирования меняется на противоположное.

В момеит пересече-ния -выходным напря ;-;ением интегратора 10 :1улевой оси на выходе

нуль-органа 13 снова поя.вляется )1мпульс, который, воздействуя на вход блока 14 коммутг-ции, переключает подвижный контакт .9 переключателя / с третьего входа (8) на П .рвый (2), а воздействуя на вход блока 15 коммутяции, запирает элемент «П 16. На втором выходе блока 15 .появляется сигнал, который отпирает элемент «Н 17, и импульсы с выхода генератора 19 опорной частоты начинают поступать на счетные входы декадпого делителя 27 частоты и счетчика 28. Частота импульсов, деленная на десять, с выхода -делителя 27 подается по счетному входу в счетчик 26, -ВЫХОДНОЙ код которого в блоке 25 сравнивается с кодом, записанным в счетчике

20, являюшимся первым остатком деления.

7

Аналого-цифровое делительное устройство выполняет операцию деления аналогового сигнала L.v на цифровой код Wy согласно выражению:

,,

.

и,.

где х , - цифровой код, нропорциональный аналоговому сигналу делимого /л-;

/С - коэффициент нропорциональности.

Таким образом, устройство ироводит цреобразование аналогового сигнала делимого -Ux в саределенное .количество НМиульсов , KOTCipbie последовательно залисываются в счетчик 20 и с иомощью сравнения в блоке 21 с цифровым кодом делителя Wy делятся на него. Macriroe от деления накапливается в счетчике 24, а в конце первого этапа деления в счетчике 20 может записаться первый остаток от деления.

Для дальнейшего ведения процесса деления необходимо первый остаток увеличить в десять раз и снова разделить на Wy рассмотренным способом. Для этого в ко;1це первого этапа запирается элемент «И 16 и отпирается элемент «И /7 и с помощью декадного делителя 27 частоты и счетчика 26 отсчитывается количество импульсов, равное первому остатку, увеличенному в десять раз. Это количество импульсов снова делится на W,/ с помощью счетчика 28 блока 29 сравнения кодов, а и.мпульсы десятой части частного Wг накапливаются в счетчике 31.

В комце второго этапа деления на выходе блока 25 сразнения кодов образуется импульс, который воздействует на второй вход блока 15 коммутации, в результате чего запирается элемент «И 17 и отпирается элемент «И 18. В счетчике 28 в конце второго этапа процесса деления записывается второй остаток деления.

Сотая часть частного от деления формируется аналогичным образом на основе использования декадного делителя 34 частоты, счетчика 33, блока 30 сравнения кодов, счетчика 35 и блока 32 сравнения кодов. Результаты деления второго остатка на цифровой коа делителя записываются з счетчп1хе 36.

Лосле отсчета количества импульсов, равного второму остатку, увеличенному в десять раз, на выходе блока .30 сравнения кодов образуется импульс «Конец цикла решения, который, воздействуя на третий вход блока 15 коммутации, ириводит его в исходное состояние, при этом прекращается подача импульсов с генератора опорной частоты в счетчики.

Результат деления записан в счетчиках 24, 31, 36, в счетчике 24 - целая часть частного.

8

в счетчике 31 - десятая часть частного, а в счетчике 35 - сотая часть частного.

Погрешность деления в основном обуславливается аналоговой частью устройства. Как известно, к колебанию температуры окружающей среды наиболее чувствителен интегратор W, от изменения параметров которого существенно меняются результаты преобразования аналс/ового сигнала делимого -Ux в

цифровой код IF-..

При 113;менепии температуры окружающей среды на входе iniTerpaTOipa 10 появляется дополн.ительцый ток положительной или отрицательной Полярности («сдвиг .нуля и ггегрирующего усилителя), который либо складывается, либо вычитается из така лреобразуе.мого аналогового сигнала делимого. iB резуль. тате получаем погреш ость в интегрировании и, следовательно, в преобразовании аналогового силнала .делимого в цифровой код.

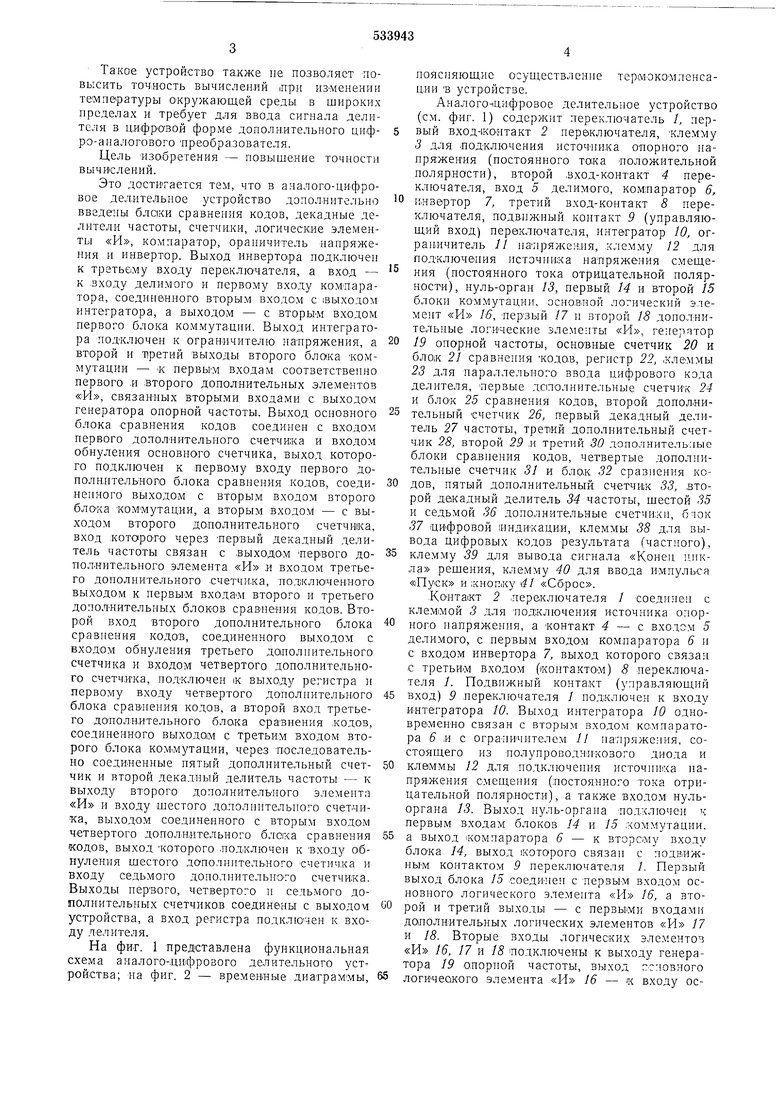

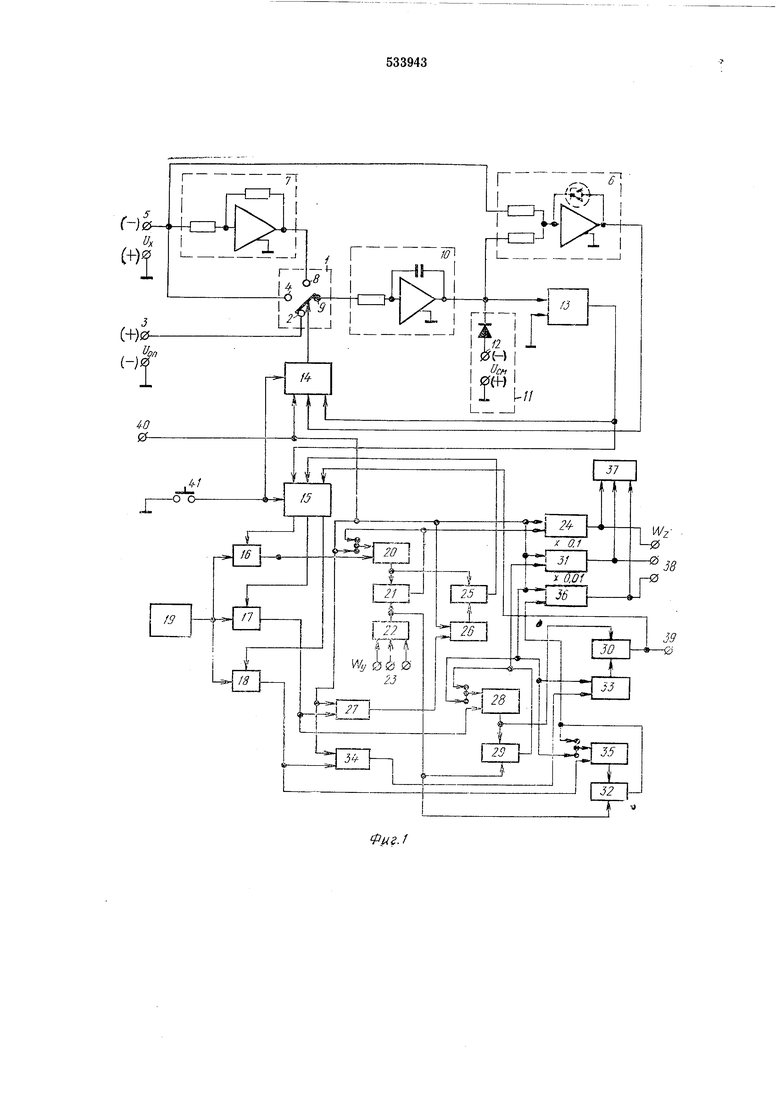

Тер.моко.миепсаЦия аналоговой части устройства осуш,ествляется следующим образом. Рассмотри. идеальный случай, когда отсутствует входное донолиительиое папряженпе Af7,r. сдвига нуля шггегратора 10. На первой и второй диаграммах фиг. 2, а изображены гра.фики напряжения а.налогового сигнала делиМОГО на входе -U и выходе -г бд. инвертора 7.

На третьей диаграмме фиг. 2, а показана кривая изменения напряжения на выходе интегратора 10. Пусть -6. const, тогда на выходе интегратора напряжение начинает линейно нарастать и в момент времени /i иересечения нулевой оси на выходе нуль-органа 13 появляется :л пульс, под дейстБ)(ем которого через блок 15 коммутации элемент «И 16 отпирается и начинается цикл преобразования аналогового сигнала в цифровой код.

В момент /2 равенства напряжения положительной полярности на выходе интегратора с напряжением делимого отрицательной полярноети -Ux изменяется направление интегрирования на противоположное. При обратном

пересечении выходным напряжением интегратора нулевой оси (момент времени з) на выходе нуль-органа 13 епова появляется импульс, под действием которого прекращается подача импульсов в счетчик 20, и цикл преобразования аналогового сигнала делимого в цифровой код заканчивается (см. четвертую диаграмму на фиг. 2, а).

Рассмотрим реаль; Ь Й случай, когда при изменении температуры окружающей среды

ка входе интегратора появилось дополнительное напряжение сдвига нуля положительной полярности +Л0д. Данное напряжение на входе интегратора вычитается из отрицательного напряже)ия делимого -U и складывается с положительным напряжением +Uy (ем. первую и вторую временные диаграммы на фиг. 2, б).В результате момент BpeMeiiii сравнения напряжения сигнала делимого с напряжением интегратора на входе компаратора 6 при прямом ходе процесса иитегрирования сдвигается на некоторый интервал вр емени А/2 2-i-2 (см. третью временную диаграмму на фиг. 2, б), а при обратном ходе- на ту же величину Д/г, но в. Обратном направлении. Это объясняется тем, что при прямом ходе на входе интегратора действовало результирующее напряжение -U -(Уд. + АС7д. а на обратном ходе напряжение

+ + .

Таким образом, если в идеальном случае от момента t до момента t иот момента tz до момента /з (см. четвертую диаграмму на фиг. 2, а) в счетчик 20 поступают равные количества импульсов:

N. + N 8 + ,

Л

то .в реальном случае от момента времени i до момента времени t имеем одиннадцать импульсов, а от момента 2 ДО момента /з - пять импульсов (см. четвертую диаграмму на фиг. 2, б)

Л N + N .

Однако в обоих случаях получаем равное количество импульсов преобразования аналогового сигнала делимого -U в цифровой код (см. четвертые временные диаграммы на фиг. 2, а, б) независимо от наличия или отсутствия напряжения смещения нуля интегратора 10.

Формула изобретения

Аналого-цифровое делительное устройство, содержащее переключатель, первый вход которого соединен с входом делимого, второй вход подключен к источнику опорного напряжения, а выход соединен с входом интегратора, подключенного выходом к входу нульоргана, выход которого соединен с первыми входами двух блоков коммутации, выход первого ,блока коммутации связан с управляющим входом переключателя, а первый выход второго блока коммутации соединен с первым входом логического элемента «И, подключенного вторым входом к выходу генератора опорной частоты, а выходом - к входу счетчика, выход которого подключен к первому входу блока сравнения кодов, соединенного вторым входом с выходом регистра, отличающееся тем, что, с целью повыщения точности вычислений, в устройство дополнительно введены блоки сравнения кодов, декадные делители частоты, счетчики, логические элементы «И, компаратор, ограничитель напряжения и инвертор, выход которого соединен с третьим входом переключателя, а вход подключен к входу делимого и первому входу компаратора, соединенного вторым входом с выходом интегратора, а выходом - с вторым входом первого блока коммутации, причем выход интегратора под10 ключей к ограничителю напряжения, а второй- и третий выходы второго блока коммутации соединены с первыми входами соответственно первого и второго дополнительных элементов «И, подключенных вторыми входами

15 к выходу генератора опорной частоты, выход основного блока сравнения кодов соединен с входом первого дополнительного счетчика и входом обнуления ооновлого счетчика, выход которого подключен к первому входу первого дополнительного блока сравнения кодов, соединенного выходом с вторым входом второго блока коммутации, а вторым входом - с выходом второго дополнительного счетчика, вход которого через первый декадный делитель частоты соединен с выходом первого дополнительного элемента «И и входом третьего дополнительного счетчика, подключенного выходом к первым входам второго и третьего дополнительных блоков сравнения кодов, причем второй вход второго дополнительного блока сравнения кодов, соединенного выходом с входом обнуления третьего дополнительного счетчика и входом четвертого дополнительного счетчика, подключен к выходу регистра и первому входу четвертого дополнительного блока сравнения кодов, а второй вход третьего дополнительного блока сравнения кодов, соединенного выходом с третьим входом второго блока коммутации, подключен

0 через последовательно соединенные пятый дополнительный счетчик л второй декадный делитель частоты к выходу второго ДОПОЛЩтельного элемента «II и входу щестого дополнительного счетчика, выходом соединенного с вторым входом четвертого дополнительного блока сравнения кодов, выход которого подключен к входу обнуления щестого дополнительного счетчика и входу седьмого дополнительного счетчика, причем выходы первого,

0 четвертого и седьмого дополнительных счетчиков соединены с выходом устройства, а вход регистра подключен к входу делителя. Источники информации, принятые во внимание при экспертизе.

5 1. Авт. с. .Ко 368615, кл. G 06 G 7/16, 1971.

2.Авт. с. ДСо 435530, кл. G 06 G 7/16, 1973.

3.Авт. с. № 415S79, кл. G 06 J 3/00, 1972.

/

(-b)J

Г

rft

| название | год | авторы | номер документа |

|---|---|---|---|

| ЧАСТОТОМЕР ДЛЯ ПРОМЫШЛЕННЫХ ЭЛЕКТРИЧЕСКИХ СЕТЕЙ | 2006 |

|

RU2326390C1 |

| Цифровой измерительный прибор | 1980 |

|

SU892309A1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СОПРОТИВЛЕНИЙ И ПРИРАЩЕНИЯ СОПРОТИВЛЕНИЯ | 2003 |

|

RU2249223C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ КОРРЕКЦИИ ПОГРЕШНОСТИ ЧАСТОТЫ ТАКТОВОГО ГЕНЕРАТОРА МИКРОКОНТРОЛЛЕРА (ВАРИАНТЫ) | 2008 |

|

RU2390786C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕЦИЗИОННЫЙ ЧАСТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ | 2006 |

|

RU2333501C1 |

| ЧАСТОТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ | 2006 |

|

RU2326391C1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1800616A1 |

| Устройство для дискретной записи и воспроизведения функций | 1981 |

|

SU982034A1 |

| ИЗМЕРИТЕЛЬ ОТНОСИТЕЛЬНЫХ АМПЛИТУДНО-ЧАСТОТНЫХ ХАРАКТЕРИСТИК | 2015 |

|

RU2584730C1 |

| АВТОМАТИЗИРОВАННОЕ ЗАРЯДНОЕ УСТРОЙСТВО | 1999 |

|

RU2159492C1 |

П

J 1

L-МГГ

J5

29

r-el.

i-)L x-const

Авторы

Даты

1976-10-30—Публикация

1975-02-03—Подача