1

Изобретение относится к автоматике и вы числительной технике и может быть использовано при реализации технических средств цифровых систем контроля и управления.

Известны устройства для сравнения двоичных чисел с допусками по принципу меньше, норма, больше, содержащие блоки сравнения, блоки памяти, логические элементы. В этих устройствах не предусмотрена классификация измеряемого значения па-

раметра по зонам (градациям).

Недостатком этих устройств является их малое быстродействие и сложность.

Известно также устройство для сравнения двоичных чисел с допусками, содержащее двоичные счетчики, элементы И, ИЛИ, блоки сравнения, блок памяти, причем управляющая щина подключена ко входам управления первого элемента И, первого двоичного счетчика и ко входу блока памяти, выходы которого соединены со входами первого блока сравнения, другие входы Ko-foporo подключены к выходам второго двоичного счетчика, вход установки в нулевое состояние которого соединен с выходом первого блока сравне-

ния, а информационный вход - с информационым входом первого двоичного счетчика и с выходом первого элемента И, другоА вход которого через элемент ИЛИ подключен к выход/ второго элемента И, входы которого соединены с выходами первого двоичного счетчика.

В этом устройстве производится Сравнение изменяющегося от нуля значения кода второго двоичного счетчика с кодом первой градации, поступающим из блока памяти. При равенстве этих кодов сигнал с выхода блока сравнения управляет позиционным распределителем и из блока памяти в блок сравнения поступает код, соответствующий второй градации и так до тех пор, пока код во втором двоичном счетчике не достигнет значения кода измеряемой величины, о чем свидетельствует наличие сигнала на выходе второго элемента И, который поступает на закрывающий вход первого элемента И.

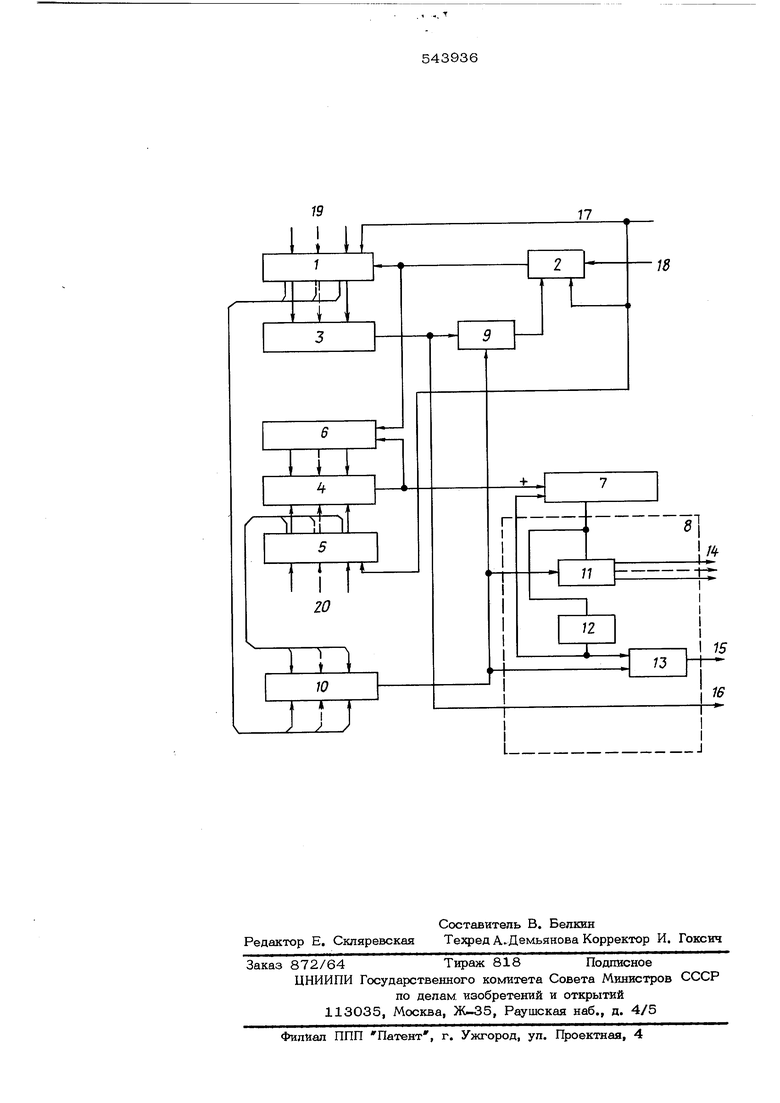

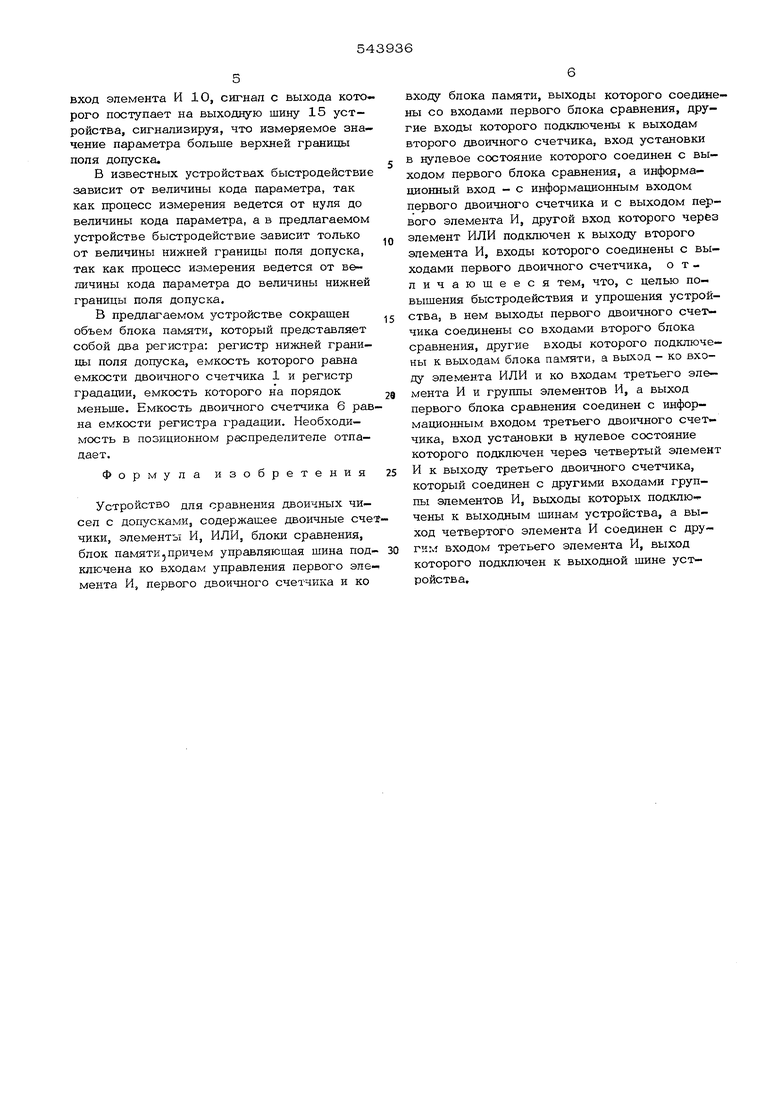

Блок памяти состоит из ( Я +1) регистров и блока вывода кодов границ градаций на блок сравнения, где J - количес во градаций.на которое разделено попе допуска. Емкость каждого регистра равна емкос первого двоичного счетчика, емкость которого равна количеству разрядов в коде измеряемого (текущего) значения параметра. Блок памяти, выполненный подобным образом, должен иметь большой объем, и сложный блок управления, Целью изобретения является повышение быстродействия и упрощение устройства. Это достигается тем, что в устройстве Выходы первого двоичного счетчика соедине ны со входами второго блока сравнения, другие входы которого подключены к выходам блока памяти, а выход - ко входу элемента ИЛИ и ко входам третьего элемента И и группы элементов И, а выход первого блока сравнения соединен с информационным входом третьего двоичного счетчика, вход установки в нулевое состояние которого подключен через четвертый эл мент И к выходу третьего двоичного счетчика, который соединен с другими входами группы элементов И, выходы которых подкл чены к выходным шинам устройства, а выхо четвертого элемента И соелинен с другим, входом третьего элемента И, выход которог подключен к выходной шине устройства. На чертеже изображена блок-схема устройства. Устройство содержит двоичный счетчик 1, элементы И 2, 3, блок сравнения 4, блок памяти 5, двоичные счетчики 6, 7, элементы И 8, 9, 1О, элемент ИЛИ 11, блок сравнения 12 j элемент И 13. Устройство имеет выходы: выходные шины код градации 14 больше 15, меньше 16, входные шины 17, 18, 19, 20, Устройство работает следующим, образомИнформация об измеряемом значении параметра в виде кода, поступающая на вхо ные шины 19, записывается в прямом коде в двоичный счетчк 1 сигналом, поступающим по входной шине 17. Этим же сигналом открывается элемент И 2, а также записываю ся в блок памяти 5 коды, соответствующие Млгей границе допуска парам.етра и вели чине одной градации, поступающие по входлым шинам 20, Последовательность тактируюших импульсов по входной шине 18 чер открытый элемент И 2 поступает на инфор мационный вход двоичного счетчика 1, работающего на вычитание, результат которо го уменьшается и сравнивается в блоке сравнения 12 с кодом нижней границы допуска параметра, поступающим из блока памяти 5. Последовательность тактирующих импульсов, поступающая на информационный вход двоичного счетчика 1 одновременно поступает на информационный вход двоичного счетчика 6, работающего на сложение, результат которого периодически сравнивается в блоке сравнения 4 с кодом одной градации, поступающим из блока памяти 5, Результат сравнения кодов с выхода блока сравнения 4 поступает на информационный вход двоичного счетчика 7 и на вход установки в нулевое состояние двоичного счетчика 6, Этот процесс повторяется периодически до тех пор, пока на информационном входе двоичного счетчика б существует последовательность тактирующих импульсов, которая прекращается когда закрьшается элемент И 2 сигналом сравнения кодов с выхода блока сравнения 12 (при достижении нижней границы поля допуска), который проходит Через элемент ИЛИ 9 на закрывающий вход элемента И 2. Одновременно сигнал с выхода блока сравнения 12 поступает на один из входов элементов И 8, на второй вход которых поступает код двоичного счетчика 7 и при их совпадении код соответствующий градации,поступает на выходные шины 14 устройства при нахождении измеряемого значения параметра в пределах поля допуска, В случае; когда код измеряемого значения параметра меньше ниж;1ей грйницы допуска, сравнение кодов в блоке сравнения 12 не происходит, результат двоичного счетчика 1 уменьшается до значения ООО...О(111.,.1), срабатывает элемент И 3 и выдает сигнал, поступающий через элемент ИЛИ 11 на закрывающий вход элемента И 2, тем самым прекращая поступление последовательности тактирующих импульсов на информационный вход двоичного счетчика 1 и одновременно на выходную щи- ну 16 устройства, сигнализируя, что измеряемое значение параметра меньше нижней границы поля допуска. В случае, когда код измеряемого значения параметра больше верхней границы допуска, двоичный счетчик 7 считает количество градаций и, когда код двоичного счетчика 7 будет соответствовать числу (П +1), где 11 - количество градаций, на котс)рое разделено поле допуска, срабатывает элемент И 9, сигнал с выхода которого закрывает двоичный счетчик 7 по входу (счет в третьем двоичном счетчике 7 прекращается) и открывает элемент И 10, В результате. сравнения кодов в блоке сравнения 12 (при достижении нижней границы поля допуска) сигнал с его выхода проходит через элемент ИЛИ 9 на закрывающий вход элемента И 2, закрывая его, и одновременно на второй вход элемента И 10, сигнал с выхода кото рого поступает на выходную шину 15 устройства, сигнализируя, что измеряемое значение параметра больше верхней границы поля допуска. В известных устройствах быстродействи зависит от величины кода параметра, так как процесс измерения ведется от нуля до величины кода параметра, а в предлагаемом устройстве быстродействие зависит только от величины нижней границы поля допуска, так как процесс измерения ведется от величины кода параметра до величины нижней границы поля допуска. В предлагаемом устройстве сокращен объем блока памяти, который представляет собой два регистра: регистр нижней границы поля допуска, емкость которого равна емкости двоичного счетчика 1 и регистр градации, емкость которого на порядок меньше. Емкость двоичного счетчика 6 рав на емкости регистра градации. Необходимость в позиционном распределителе отпадает. Формула изобретения Устройство дпя сравнения двоичных чисел с допусками, содержащее двоичные сче чики, элементы И, ИЛИ, блоки сравнения, блок памяти,причем управляющая шина под ключена ко входам управления первого эпе- мента И, первого двоичного счетчика и ко входу блока памяти, выходы которого соединены со входами первого блока сравнения, другие входы которого подключены к выходам второго двоичного счетчика, вход установки в нулевое состояние которого соединен с выходом первого блока сравнения, а информационный вход - с информационным входом первого двоичного счетчика и с выходом первого элемента И, другой вход которого через элемент ИЛИ подключен к выходу второго элемента И, входы которого соединены с выходами первого двоичного счетчика, отличающееся тем, что, с целью повышения быстродействия и упрощения устройства, в нем выходы первого двоичного счет чика соединены со входами второго блока сравнения, другие входы которого подключены к выходам блока памяти, а выход - ко входу элемента ИЛИ и ко входам третьего элемента И и группы элементов И, а выход первого блока сравнения соединен с информационным входом третьего двоичного счетчика, вход установки в нулевое состояние которого подключен через четвертый элемент И к выходу третьего двоичного счетчика, который соединен с другими входами группы элементов И, выходы которых подключены к выходным шинам устройства, а выход четвертого элемента И соединен с другим входом третьего элемента И, выход которого подключен к выходной шине устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнений двоичных чисел с допусками | 1977 |

|

SU708347A1 |

| Устройство для сравнения чисел с допусками | 1979 |

|

SU769533A1 |

| Устройство для сравнения чисел с допусками | 1978 |

|

SU750480A1 |

| Устройство для сравнения чисел с допусками | 1981 |

|

SU960798A1 |

| Система контроля параметров | 1984 |

|

SU1190364A1 |

| Устройство для сравнения чисел | 1979 |

|

SU830373A1 |

| Устройство контроля качества датчиков времени | 1986 |

|

SU1422218A1 |

| Устройство допускового контроля частоты | 1974 |

|

SU521526A2 |

| Устройство для сравнения двоичных чисел | 1980 |

|

SU943706A1 |

| Устройство для допускового контроля частоты | 1990 |

|

SU1781633A1 |

Авторы

Даты

1977-01-25—Публикация

1975-02-04—Подача