ром Л соединен с входом управления «Запись без сравнения (/С+1)-ой п входом управления «Запись со сравнением (/С4-2)-ой ступени матрицы ячеек выделения максимального сигнала, вход управления «Запись со сравиеиием второй ступени, вход управления «Запись без сравнения первой ступени и вход первого делителя частоты подключеиы к первому выходу управляющего устройства, второй выход управляющего устройства соединен с входом синхронизации коммутатора и входом счетчика модулятора яркости, а выход переполнения этого счетчика соединен с входом запуска генератора развертки.

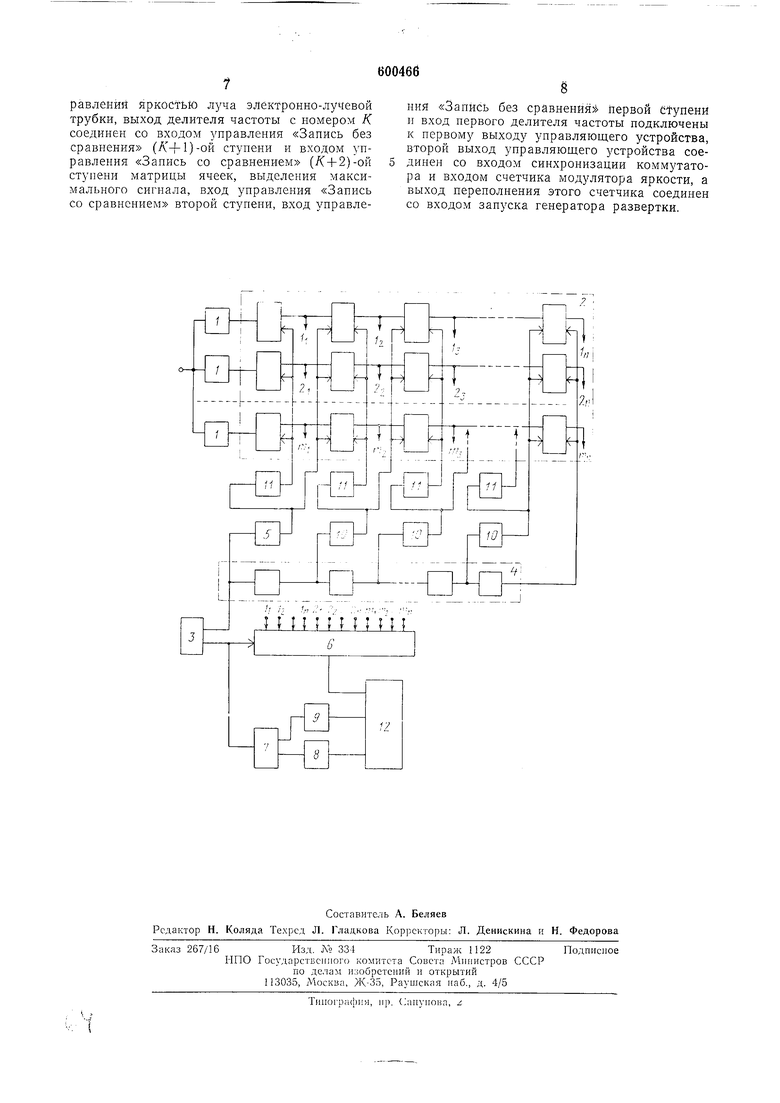

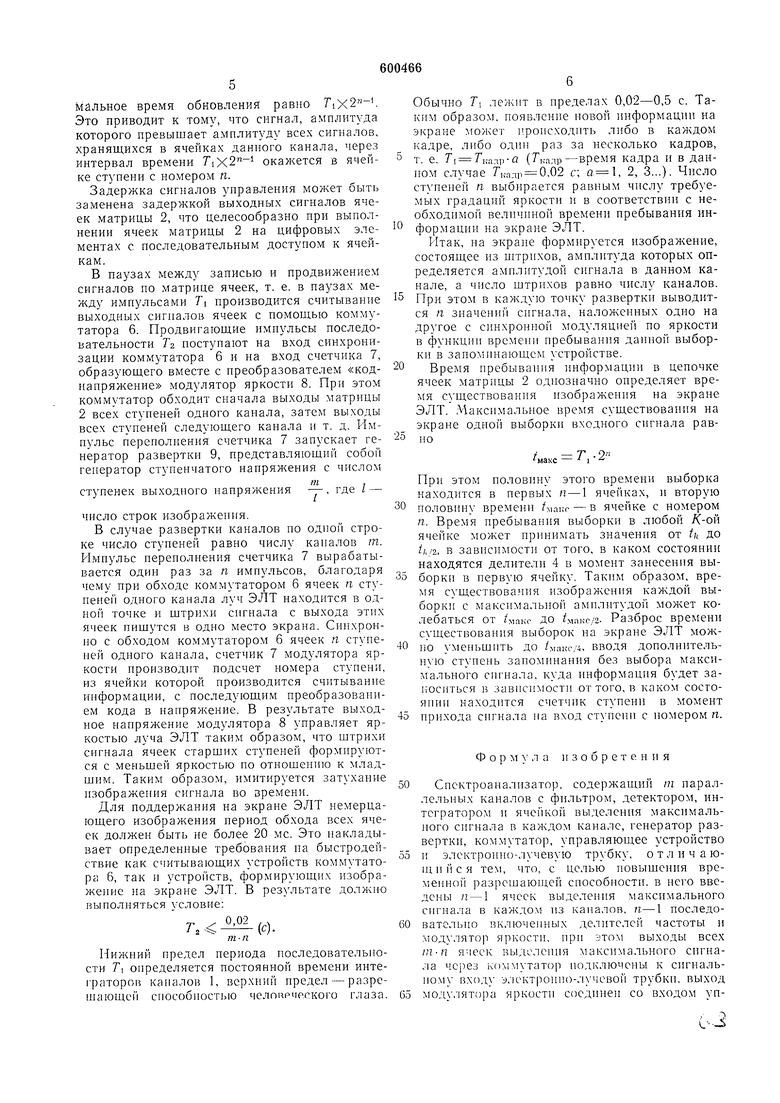

На чертеже изображена структурная электрическая схема спектроапализатора, содержащая каиалы 1 с фильтром, детектором и интегратором, матрицу 2 с т-п ячейками выделения максимального сигнала, управляющее устройство 3, делители частоты 4, элемент задержки 5, коммутатор 6 считывания, счетчик 7 и модулятор 8 яркости в виде преобразователя «код-напряжение, генератор развертки 9, элемент задержки 10, дополиительпые элементы задержки 11, электронно-лучевую трубку 12.

Спектроанализатор работает следующим образом.

Сигнал, подлежащий анализу, поступает на входы капалов I и после детектирования и интегрирования - на входы ячеек нервой ступеин матрицы 2. Управляющее устройство 3 вырабатывает две несовпадающие имиульспые последовательности Ti и TZ с различными периодами, причем Tt Tz-m-n. Импульсы Ti поступают на вход первого из делителей частоты 4 и на входы управления ячеек первой и второй ступеней. Если первые Р делителей частоты находятся в состоянии заполнения, то очередной импульс Т( вызовет появление выходных импульсов этих делителей частоты, п произойдет перепое импульса счета в Р+1 делитель частоты. Одновременное появление выходных сигналов сразу па Р выходах, где Р циклически прпнимает значение от О до п-1, делает необходимым разиесеиие этих импульсов во времени на входах управления ячеек матрицы 2 (ть Т2, тз... Tn-i) с номощью элементов задержки 5, 10 и 11. При этом должно выполняться следующее неравенство TI Т2 тзТп-1. Время То элементов задержки 11 определяется только величиной скорости записи ячеек.

Ячейки матрицы 2 представляют собой пиковые детекторы с цепями управления записью и стираиием. Матрица 2 может работать в двух ре/кимах записи. Первый режим- запись со сравнением, когда в ячейку нронзводнтся заннсь выборки входного сигнала f/,при выполиепии условия .i, где - значение заиисаипой в ячейке иредыдущей выборки. При Ui Ui--i в ячейке остается старое значение сигнала.

При втором режиме работы в ячейку матрицы 2 записывается новое значение сигиа, ь

ла при любом значении его амплитуды. В зависимости от конкретной схемы ячейки запись нового значения сигнала может производиться как с предварительным стирапием старой информации, так и без иего. И в том, и в другом случае можно конструктивно выделить два входа управления, которые в дальпейшем будут именоваться «Запись без сравнепия и «Запись со сравнением.

При появлении импульса на входе /С-го делителя частоты 4 происходит следующее. Через интервал времени тл этот импульс поступит на вход «Занись со сравиением ячеек матрицы 2 (/С+1)-ой ступени, в результате

чего в ячейки этой стуиени будет произведена запись сигналов U/,i при выполнении условия ,i (Uki - значепие сигнала в ячейке К-ои ступени t-oro канала, ,i - то же в ячейке (/С+1)-ой ступени).

Через время r/j-f то импульс делителя частоты поступит на вход управления «Запись без сравнения ячеек /С-ой ступепи, в результате чего в эти ячейки будет переписана информация из ячеек (К)-ой ступеин. Аналогичные процессы будут происходить во всех предыдущих ступенях, вплоть до первой. Выходной импульс (К-1)-ого делителя частоты через время Тй-1 поступит па вход управления «Занись со сравнением ячеек К-оп ступени, что не вызовет измеиеиий в ее состоянии так как сигнал с выхода ячеек матрицы 2 (/(-1)-ой ступени уже переписан в ячейки /С-ой ступени матрицы 2 по команде импульса с входа

К-го делителя частоты. Через время (т/,-1-Ь -Ьто) входной импульс (К-1)-го делителя частоты поступит па вход «Запись без сравнения ячеек матрицы ()-ой ступени, в результате чего в эти ячейки будет занесена информация с выхода ячеек (К-2)-ой ступени и т. д.

Таким образом, нри ноявлении на входе делителя частоты с номером К в ячейках всех ступеней от нервой до ступени с номером /(

произойдет продвижение информации на одну ступень, а в ячейки с номером /C+l новая информация с выхода ячеек К-ой ступени будет записана только в том случае, если Uhj C//,. В результате произойдет выделение максимального сигнала на интервале времени, определяемом периодом выходных импульсов делителей частоты данной ступени Tj,, причем

Т - Т . ak-i , g ,

где q - коэффициент пересчета делителей частоты.

В даииом случае 9 2. Аналогичные процессы происходят в ячейках других ступеней.

В результате информация в ячейках первой ступеии обповляется один раз за время Гь в ячейках второй ступени - не реже, чем один раз за время 27), в ячейках третьей ступе1п- - не реже, чем один раз за время 4Г1 н

т. д. В ячейках ступепи с номером п максимальное время обновления равно . Это приводит к тому, что сигнал, амплитуда которого превышает амплитуду всех сигналов, хранящихся в ячейках данного канала, через интервал времени TiX2 окажется в ячейке ступени с номером п.

Задержка сигналов унравления может быть заменена задержкой выходных сигналов ячеек матрицы 2, что целесообразно при выполнении ячеек матрицы 2 на цифровых элементах с последовательным доступом к ячейкам.

В паузах между записью и продвижением сигналов по матрице ячеек, т. е. в паузах между импульсами Ti производится считывание выходных сигналов ячеек с помощью коммутатора 6. Продвигающие импульсы последовательности 2 поступают на вход синхронизации коммутатора 6 и на вход счетчика 7, образующего вместе с нреобразователем «коднапряжение модулятор яркости 8. При этом коммутатор обходит сначала выходы матрицы 2 всех стуненей одного канала, затем выходы всех ступеней следующего канала н т. д. Имнульс переполнения счетчика 7 запускает генератор развертки 9, представляющий собой генератор ступенчатого нанряжения с числом

да.

ступенек выходного напряжения -, где i -

чнсло строк изображения.

В случае развертки каналов но одной строке число стуненей равно числу каналов т. Имнульс нереполнения счетчика 7 вырабатывается один раз за п импульсов, благодаря чему при обходе коммутатором 6 ячеек п ступеней одного канала луч ЭЛТ находится в одной точке и щтрихи сигнала с выхода этих ячеек пишутся в одно место экрана. Синхронно с обходом коммутатором 6 ячеек п ступеней одного канала, счетчик 7 модулятора яркости нронзводит подсчет номера ступени, из ячейки которой производится считывание информации, с последующим преобразованием кода в нанряженне. В результате выходное напряжение модулятора 8 управляет яркостью луча ЭЛТ таким образом, что штрихи сигнала ячеек старших ступеней формируются с меньшей яркостью по отношению к младшим. Таким образом, имитируется затухание изображения сигнала во времени.

Для ноддержания на экране ЭЛТ немерцающего изображения нернод обхода всех ячеек должен быть не более 20 мс. Это накладывает определенные требования на быстродействие как считывающих устройств коммутатора 6, так и устройств, формирующих изображение на экране ЭЛТ. В результате должно выполняться условие:

0,02

(с).

Т,

Пижннй предел периода последовательности Т определяется постоянной времени интеграторов каналов 1, верхний нредел-разреН1ающей способностью челоирческого глаза.

Обычно 7i лежит в нределах 0,02-0,5 с. Таким образом, появление новой информацни на экране может происходить либо в каждом кадре, либо один раз за несколько кадров,

т. е. 71 7калр-а (Ткадр-время кадра и в данном случае 7кадр 0,02 с; , 2, 3...). Чнсло стуиеней /г выбирается равным чнслу требуемых градаций яркостн и в соответствии с необходимой величиной времени нребывания информации на экране ЭЛТ.

Итак, на экране формируется изображение, состоящее из штрихов, амплнтуда которых определяется амплитудой сигнала в данном канале, а чнсло штрихов равно числу каналов.

При этом в каждую точку развертки выводится п значений сигнала, наложенных одно на другое с синхронной модуляцией по яркости в функции времени нребывания данной выборки в запомннаюшем устройстве.

Время пребывапия информации в цепочке ячеек матрицы 2 одиозначно оиреде,яяет время сушествования изображения на экране ЭЛТ. Максимальное время существования на экране одной выборки входного снгнала равно

/ - Г . 9 макс - 1

При ЭТОМ ноловнну этого времени выборка находится в первых п - 1 ячейках, н вторую

половииу времени /мак-с - в ячейке с номером п. Время пребывапня выборки в любой /С-ой ячейке может нринимать значения от tu до ti,/2, В завнсимости от того, в каком состоянии находятся делители 4 в момент занесения выборкн в первую ячейку. Таким образом, время существования изображения каждой выборки с максимальной амплитудой может колебаться от /макс до макр/2. Разброс времени существования выборок на экране ЭЛТ мож}jo уменьшить до /макс/, вводя дополнительную ступень запоминания без выбора максимального снгнала, куда информация будет заноситься в зависимости от того, в каком состоянии находится счетчик ступени в момент

прихода сигнала на вход ступени с номером п.

Фор м у л а изобретения

Снектроанализатор, содержащий т нараллельиых каналов с фильтром, детектором, интегратором и ячейкой выделения макснмального сигнала в каждом канале, генератор развертки, коммутатор, управляющее устройство

и электронно-лучевую трубку, отлнчаюHU1 и с я тем, что, с целью повыщення временной разрешаюн1,ей снособности. в него введены п - 1 ячеек вы.а,е,1ения максимального снгнала в каждом из каналов, п-1 последовательно включенных делителей частоты и модулятор яркости, нрн этом выходы всех п-п ячеек выдолення максимальиого сигнала через коммутатор нодключсны к сигнальному входу электронно-лучевой трубки, выход

модулятора яркостн соединен со входом управленин яркостью луча электронно-лучевой трубки, выход делителя частоты с номером /С соединен со входом управления «Запись без сравнения (Л+1)-ой ступени и входом управления «Запись со сравнением (/С + 2)-ой ступени матрицы ячеек, выделения максимального сигпала, вход управления «Запись со сравнепием второй ступени, вход управления «Запись без сравнения первой CtyncHH н вход первого делителя частоты подключены к первому выходу управляющего устройства, второй выход управляющего устройства соединен со входом синхронизации коммутатора и входом счетчика модулятора яркости, а выход переполнения этого счетчика соединен со входом запуска генератора развертки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Спектроанализатор | 1979 |

|

SU822074A1 |

| Спектроанализатор | 1979 |

|

SU866494A1 |

| Устройство для индикации | 1984 |

|

SU1236540A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1354242A1 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1987 |

|

SU1525726A1 |

| Устройство для отображения информации на экране видеоконтрольного блока | 1988 |

|

SU1562954A1 |

| Устройство для преобразования сейсморазведочной информации | 1987 |

|

SU1497599A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1980 |

|

SU938310A1 |

| Устройство для отображения радиолокационной информации на экране электронно-лучевой трубки | 1989 |

|

SU1691880A1 |

| Устройство для ввода и вывода цветной графической информации | 1986 |

|

SU1348873A1 |

п п п п пп

Авторы

Даты

1978-03-30—Публикация

1975-01-15—Подача