1

Изобретение относится к измеритепьной технике, в частности, к дискриминаторам импульсов, использующимся для отбора импульсов по амплитуде.

Известен дискриминатор импульсов, содер жаший резистор, соединенный последовательно с выводом источника входного сигнала, дифференциальный усилитель на двух транзисторах.эмиттеры которых соединены с генератором тока.а коллекторы транзисторов днфференциального усилителя подключены через резисторы к выводам второго источника питания, при этом база первого транзистора дифференциального усилителя соединена с коллектором транзистора цепи отрицательной обратной связи, эмиттерный переход зашунтирован диодом, база транзистора цепи отрицательной обратной связи соединена с коллектором второго транзистора дифференциального усилителя, а эмиттер транзнстора цепи отрицательно обратнойсвязи подключен к выводу первого источника питания 11.

Однако, у известного дискриминатора недостаточно высокая точность и завышенное время восстановления.

Цель изобретения - повышение точности дискриминатора и уменьшение времени восстановления.

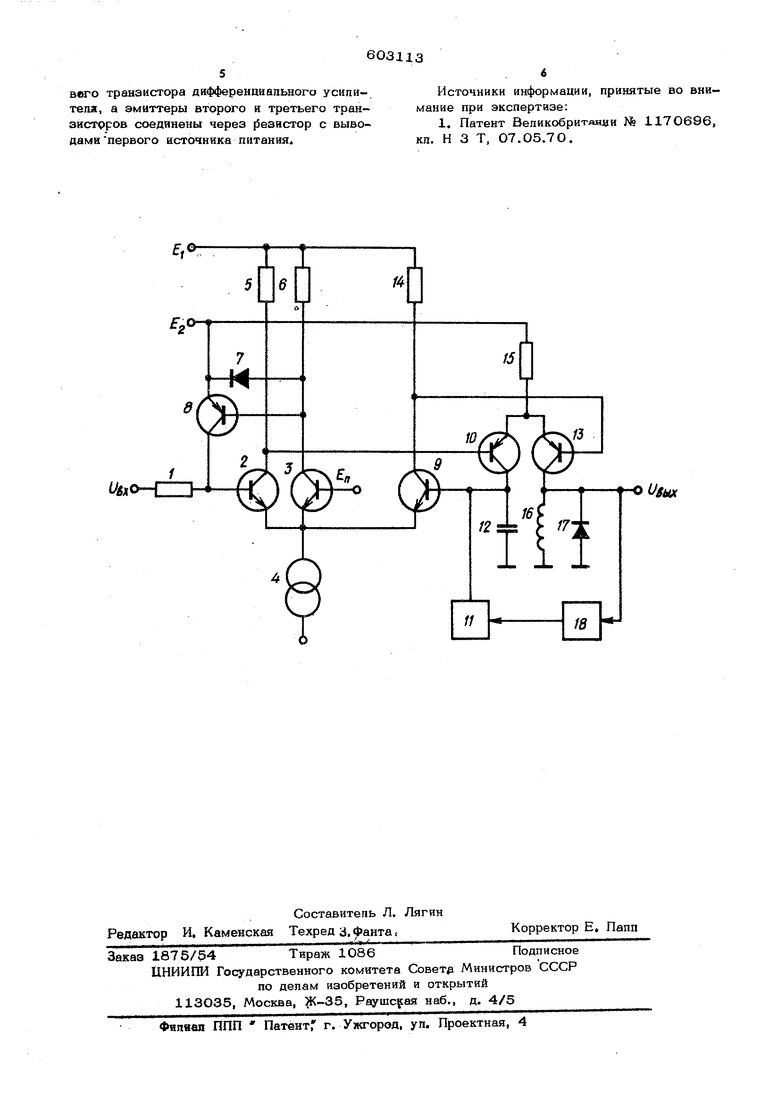

Это достигается тем, что в предлагаемый дискриминатор импульсов введены три транзистора, два резистора, конденсатор, индуктивность, диод, разрядное устройство и элемент задержки, причем эмиттер первого транзистора соединен с эмиттерами транзисторов дифференциального усилителя, база первого транзистора соединена с коллектором второго транзистора и с конденсатором, а через последовательно соединенные „элемент задержки и разрядное устройствос коллектором третьего транзистора, к которому подключены параллельно соединенные индуктивность и диод, при этом коллектор первого транзистора подключен к базе третьего транзистора и через резистор к выводам второго источника питания, база второго транзистора соединена с коллектором первого транзистора дифференциального усилителя, а эмиттеры второго и третьего транзисторов соединены через резистор с выводами первого источника пчтания. ,На чертеже показана схема предлагаемю го дускрнмннатора. Входной сигнал поступает через резистор 1, второй конец которого соединен с базой транзистора 2 дифференциапьного уси тепя , база транзистора 3 дифференциального усилителя соединена с источником Ен, задающим пороговое напряжение, В цепи эмитт ров транзисторов 2 и 3 включей генератор 4 тока, в коллекторных цепях - нагрузки 5, 6. Диод 7 шунтирует эмиттерный переход транзистора 8, эмиттер которого соединен с источником питания, база - с коллектором транзистора 3, а коллектор - с резистрром 1и базой транзистора 2. Транзистор 9 соединен эмиттером с эмиттерами тр.анзисторов 2 и 3, базой - с коллектором транзист ра 10, разрядным устройством 11 и конден сатором 12. Коллектор транзистора 9 соединен с базой транзистора 13и через ре- зистоо 14 с источником питания Е{.:.аза транзистора 10 соединена с коллектором транзистора 2. Э|Литтеры транзисторов 10 и 13 соединены через р 4зистор 15 с источником питания Н-. Коллектор транзистора 13 соединен с нагрузкой, состоящей из индуктивности 16 и диода 17, и элементом 18 задержки. В исходном состоянии входное напряжение меньше напряжения на базе, транзистора 3, однако за счет обратной связи через транзистор. 8 напряжение на базе транзистора 2устанавливается близким к напряжению н базе транзистора 3, а за счет обратной связи через транзистор Ю таким же образом устанавливается напряжение на базе транзистора 9, при этом ток коллектора транзистора 10 равен сумме токов базы транзистора 9 и разрядного устройств1а 11. Через транзисторы 2, 3 и 9 протекают одинаковые токи.. При возрастании входного напряжения до величины напряжения порога ток через резистор 1 падает до нуля, при этом транзистор 8 запирается и выключает отрицателы{ую обратную связь с коллектора транзистора 3 на базу транзистора 2. Дальнейшее возрастание входного напряжения приводит к увеличению тока через транзистор 2 и соответственно к запиранию тра зистора 3. Возрастание тока через транзистор 2 приводит к увеличению тока через транзистор 10, в результате чего напряжение на конденсаторе 12 возрастает вместе с входным сигналом, В момент вр мени, соответствующий верщине входного икшульса, токи через транзисторы 2 и 9 близки по величине. При уменьшении входного напряжения, происходит перераспре деление токов: транзистор 2 закрывается, а транзистор 9 еще сильнее открывается,соответственно закрывается транзгсстор 10 и открывается транзистор 13,. Импульс тока в цепи коллектора транзистора 13 в момент перехода входного напряжения через максимум образует на индуктивности 1.6 выходной сигнал. Диод 17 шунтирует выброс обратной полярности. Транзисторы 2 и 3 остаются закрыты- ми, пока конденсатор 12 не разрядится ао( напряжения порога, причем, первым открывается транзистор 3, а затем по мере открывания транзистора 8 возрастает до первоначального значения и ток транзистора 2 -. л , :.- ./ / С Целью уменьшения и нормализации времени восСтанЬвления схемы введен элемент задержки. 13ыходной сигнал дискриминатора задерживается: на этом элементе и запускает разрядное устройство. Ф 6 р м у. па и 3 о б р е те НИН Дискриминатор импуиьсов, срдерясаший резистор, соединеннь1Й последовательно с выводом источника входного cHrnanai дифференциальный усилитель на двух транзисторах,эмиттеры соединены с рат(Ч)ом тока, а коллектсфы транзисторов дифференциального усилителя подключены через резисторы к выводам второго источника питания, при этом база первого транзистора дифференцийальнрго усилителя соединена с коллектором Транзистора цепи отрицательной обратной связи, эмиттерный переход которого 1зашунтирован диодом, база транзистора цепи отрицательной обрат- ной связи соединена с коллектором второго транзистора дифференциального усилителя, а .эмиттер транзистора цепи отрицательной обратной связи подключен к выводу первого Источника питания . т л и ч а ю ш и йс я тем, что с целью повышения точности дискриминатора и уменьшения времени восстановления, в него введены, три транзистора, два резистора, конденсатор, индуктивность, диод, разрядное устройство и элемент задержки, причем эмиттер первого транзистора соединен с эмиТтерами транзисторов дифференциального усилителя, база первого транзистора. соедине на с коллектором второго транзистора и с конденсатором, а через последовательно соединенные элемент задержки и разрадное устройство - с кол- лектором третьего транзистора, к которому подключены параллельно .соединенные индуктивность и диод, при этом коллектор первого транзистора подключен к базе третьего транзистора и через резистор к выводам второго источника питания, база второго транзистора соединена с коллектором перввго транзистора дифференциального усипитепя, а эмиттеры второго и третьего транзисях ров соединены через {Зезистор с выводами первого источника питания.

Источники информации, принятые во внимание при экспертизе:

1. Патент Велнкобритяици № 1170696, кл. Н 3 Т, 07,О5,7О.

| название | год | авторы | номер документа |

|---|---|---|---|

| Амплитудно-временной преобразователь | 1974 |

|

SU849484A1 |

| Амплитудный дискриминатор | 1985 |

|

SU1298709A1 |

| СИСТЕМА ЗАЖИГАНИЯ С НАКОПЛЕНИЕМ ЭНЕРГИИ НА КОНДЕНСАТОРЕ | 1992 |

|

RU2020259C1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| Транзисторный ключ переменного тока | 1990 |

|

SU1791927A1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1994 |

|

RU2114500C1 |

| Стабилизатор напряжения с самозащитой | 1982 |

|

SU1046751A1 |

| УНИВЕРСАЛЬНОЕ ЗАРЯДНОЕ УСТРОЙСТВО АГАТ-Ц-УЗУ И СПОСОБ ГРАДУИРОВКИ ИЗМЕРИТЕЛЯ НАПРЯЖЕНИЯ, ПОДКЛЮЧАЕМОГО ДЛЯ КОНТРОЛЯ НАПРЯЖЕНИЯ НА ВЫХОДЕ УНИВЕРСАЛЬНОГО ЗАРЯДНОГО УСТРОЙСТВА | 1992 |

|

RU2042247C1 |

| Транзисторный инвертор | 1990 |

|

SU1757069A1 |

| Устройство электронной защиты | 1982 |

|

SU1136133A1 |

ОбЛ4Г IZ}

Авторы

Даты

1978-04-15—Публикация

1974-11-04—Подача