(54) СТ.ЛБИЛИЗ.ЛТОР ПОСТОЯПНОГО Н.ЛПРЯЖЕППЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство электронной защиты | 1980 |

|

SU974358A1 |

| Устройство электронной защиты | 1982 |

|

SU1136133A1 |

| Стабилизатор постоянного напряжения | 1982 |

|

SU1051518A1 |

| СПОСОБ СТАБИЛИЗАЦИИ СТАТИЧЕСКОГО РЕЖИМА ЭМИТТЕРНЫХ ЦЕПЕЙ НИЗКОВОЛЬТНЫХ ТРАНЗИСТОРНЫХ КАСКАДОВ | 2009 |

|

RU2386205C1 |

| СТАБИЛИЗАТОР НАПРЯЖЕНИЯ | 2011 |

|

RU2472202C1 |

| Полупроводниковый стабилизатор напряжения | 1973 |

|

SU506841A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2346386C1 |

| СИНХРОННЫЙ ГЕНЕРАТОР С ПРЕЦИЗИОННОЙ СИСТЕМОЙ УПРАВЛЕНИЯ | 2005 |

|

RU2295192C1 |

| Ключевой стабилизатор | 1987 |

|

SU1467398A1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2411636C1 |

1

Изобретение относится к области электротехники И может быть использовано в цепях питания различной радиотехнической аппаратуры.

Известен стабилизатор постоянного напряжения, содержащий регулирующий элемент И цепь обратной связи, состояп1ую из делителя выходного напряжения, усилителя рассогласования и источника опорного напряжения 1 .

Наиболее близким к предложенному по технической сущности является стабилизатор, содержащий регулируюп1ИЙ элемент, включенный в одну из силовых щин, токостабилизирующий элемент, включенный в общую эмиттерную цепь параллельно-баланеного каскада, первый вход которого подключен к источнику опорного напряжения, второй вход - к выходу первого делителя, подключенного к выходным выводам, а выход параллельно-балансного каскада подключен к конденсатору и ко входу регулирующего элемента 2.

Недостатком таких стабилизаторов является невысокое быстродействие при больших скачках тока в нагрузке или при переходе с одного уровня стабилизируемого

напряжения на другой. Здесь и дгкчее под параметрами быстродействия будем понимать время установления переходного ирчцесса И скорость нарастания выходного напряжения.

Целью изобретения является иовыиюние быстродействия стабилизатора напряжения. Это достигается тем, что в предложенный стаби.чизатор постоянного напряжения дополнительно введены второй и третий делители напряжения, каждый из которых выполнен на резисторе п диоде, причем второй делитель включен параллельно источнику опорного напряжения, третий делитель включен между общей щиной и выходом первого делителя, а выходы третьего и второго делителей соединены через встречно вк,тюченные до110Л1П1тельно введенные диоды, общая точка которых подключена к общей э.миттерной цепи паралле,чьно-ба.-1ансного каскада через дополнительно введенный резпстор. Кроме того, между дополнительным резистором И общей точкой донолннте,1ьных ДИОДОВ может быть включен эмиттер-базовый иереход дополнительного транзисЮ, коллектор которого соединен с обн1ей HiHHoii.

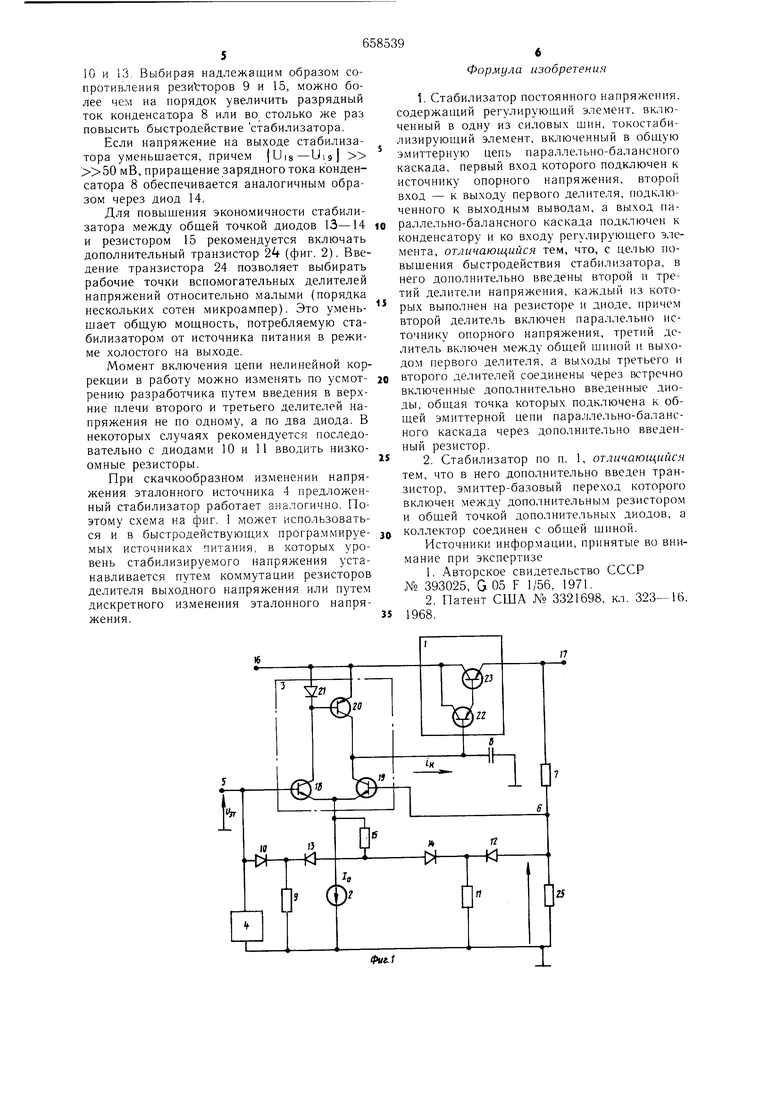

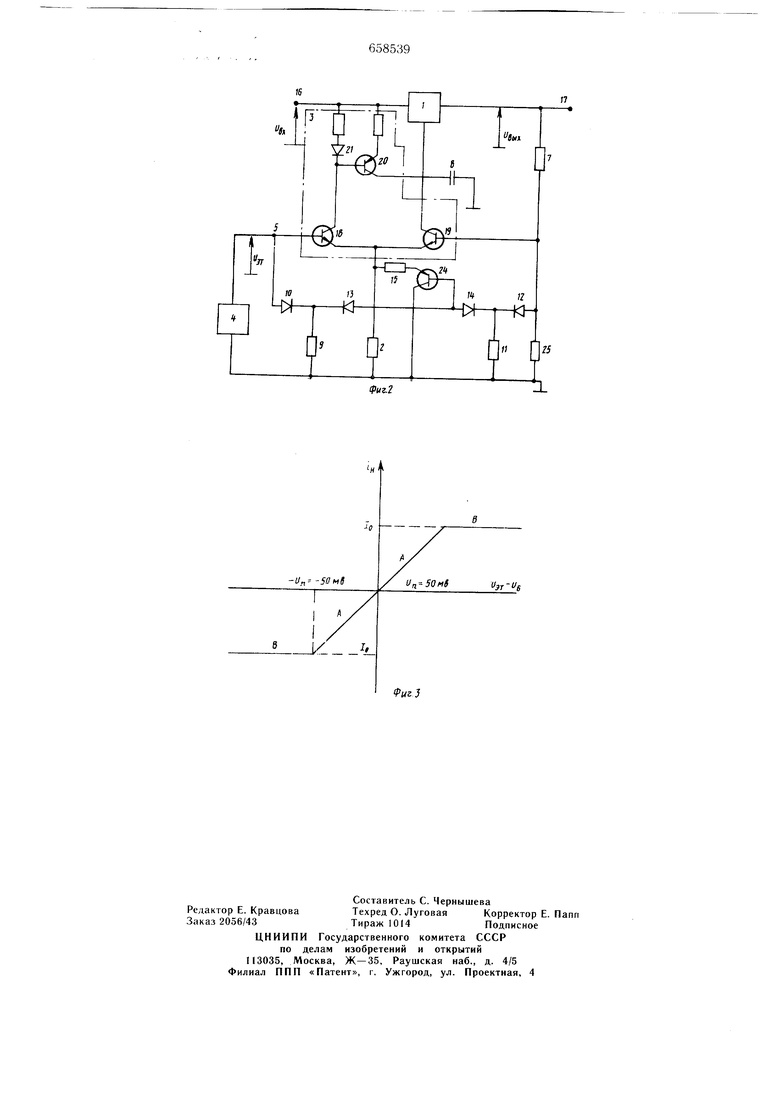

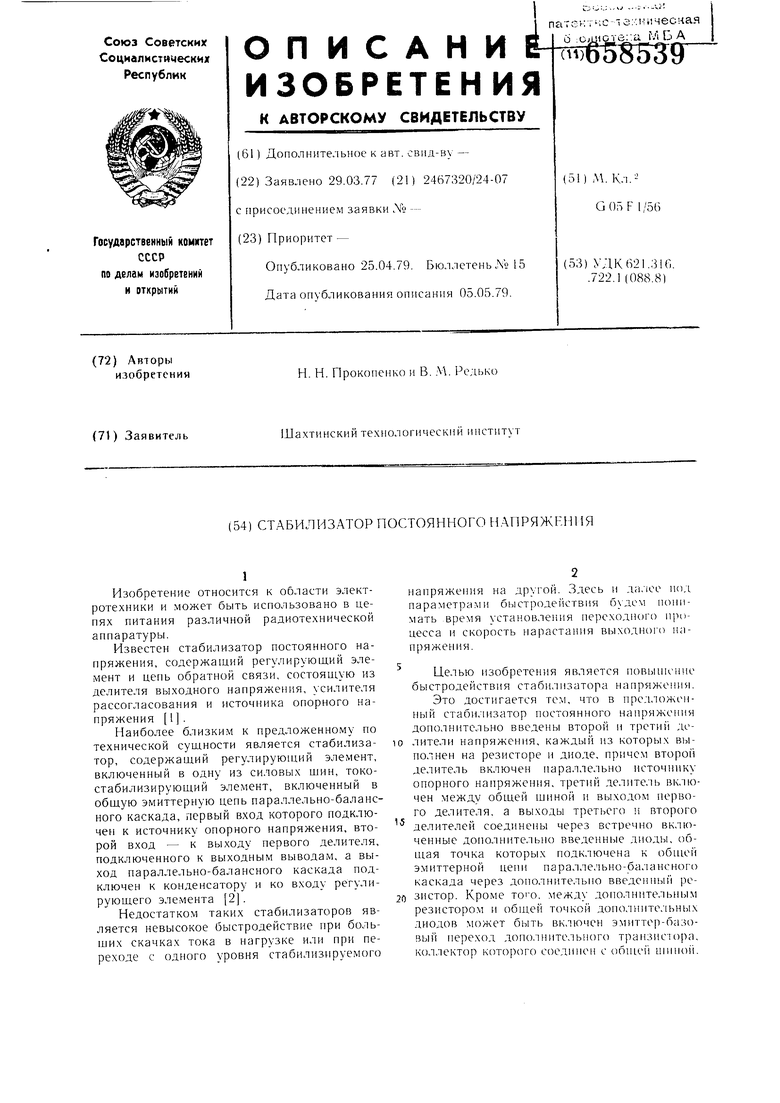

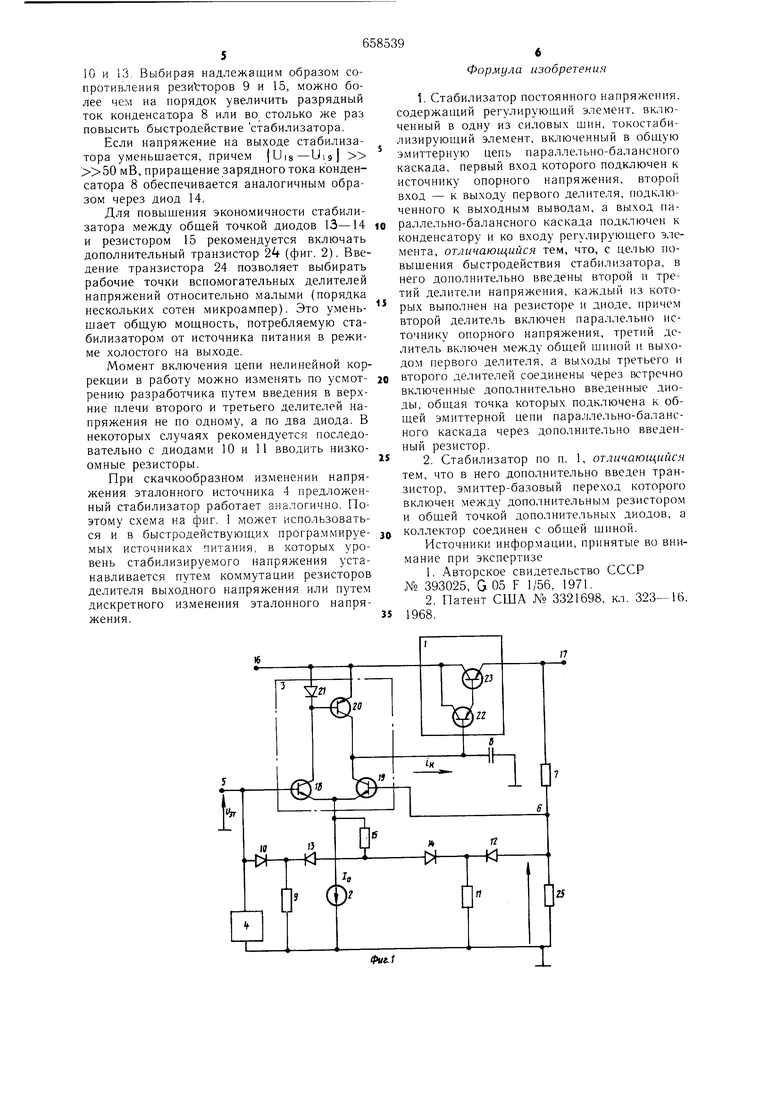

Схема предложенного стабилизатора приведена на фиг. 1; на фиг. 2 - то же, вариант; на фиг. 3 показана зависимость тока нагрузки усилителя сигнала рассогласования (параллельно-балансного каскада) от входного напряжения.

Стабилизатор напряжения содержит регулирующий элемент 1 и токостабилизирующий элемент 2 в общей эмиттерной цепи параллельно-балансного каскада 3. Каскад 3 играет роль усилителя сигнала рассогласования. Источник опорного напряжения 4 связан с первым входом 5 каскада 3, второй вход 6 которого подключен к первому делителю напряжения. Резистор 7 образует верхнее плечо данного делителя. Выход каскада 3 соединен с корректирующим конденсатором 8 и входом регулирующего элемента 1. К-источнику Ц опорного напряжения подключен второй делитель напряжения, выполненный на резисторе 9 и диоде 10. К выходу 6 первого делителя напряжения подключен третий делитель, содержащий резистор 11 и диод 12. Выходы второго и третьего делителей соединены через встречно включенные диоды 13 и 14. Общая точка диодов 13 и 14 подключена к токостабилизирующему элементу 2 через дополнительный резистор 15. К выводу 16 присоединяется источник напряжения постоянного тока, вывод 17 является выходом стабилизатора. Параллельно-балансный каскад 3 выполнен на транзисторах 18, 19, 20 и диоде 21. Регулирующий элемент 1 содержит транзисторы 22 и 23.

Стабилизатор, показанный на фиг. 2, построен в соответствии со вторым пунктом формулы изобретения. Последовательно с дополнительным резистором 15 включен эмиттерно-базовый переход дополнитель:ного транзистора 24. Нижнее плечо делителя выходного напряжения выполнено в виде резистора 25.

В установивщемся режиме напряжения на втором входе 6 параллельно-балансного каскада 3 приблизительно равно напряжению на эталонном источнике 4 (). Для устранения самовозбуждения в области высоких частот в схему введен корректирующий конденсатор 8. Он вносит уменьшение усиления по петле обратной связи с весьма низких частот (единицы-десятки Герц). В то же самое время транзисторы, применяемые в типовых стабилизаторах, имеют граничные частоты, измеряемь е сотнями мегагерц. Поэтому конденсатор 8 является самым инерционным элементом в схеме компенсационного стабилизатора.

Основной особенностью параллельно-балансного каскада, определяющей быстродействие стабилизатора, является то, что он име ет узкий динамический диапазон. Если модуль напряжения между базами транзисторов 18-19 в переходном режиме превыщает 50 мВ (|Ui9 -Ц si мВ), выходной

ТОК каскада (i ) являющийся зарядным (разг рядным) током конденсатора 8, ограничивается (фиг. 3).

Предположим, что ток в нагрузке стабилизатора уменьшается, причем приращение тока имеет прямоугольную форму. Это приводит к скачкообразному изменению напряжения на выводе 17, которое через резистор 7 поступает на базу транзистора 19 (LJi9 возрастает). Стабилизатор отрабатывает появившийся сигнал рассогласования .между Uig и Ui. При этом наибольший интерес представляют два случая. Первый, когда сигнал рассогласования мал Ui9-Uig мВ), второй - когда сигнал рассогласования велик (Uig-Uig Un 50.мВ),где Un - пороговое напряжение каскада 3.

В первом случае параллельно-балансный каскад работает на участке А проходной характеристики iH. .f(U(9 -U|8 ) фиг. 3. Стабилизатор ведет себя как линейная система

0 автоматического регулирования. Время установления выходного напряжения - tye, как и любой линейной системы первого порядка, минимально и не превышает величины 3 + 4/2nf5p, где fcp - частота единичного усиления по петле обратной связи.

Во втором случае, когда (Ui9i-Uigj мВ, параллельно-балансный каскад входит в режим ограничения. Между его выходнь м током 1ц и сигналом рассогласования Uig-Uig нарушается пропорциональность (фиг. 3, участок В). Конденсатор 8 перезаряжается сравнительно небольшим по величине током, численно равным току 1о двухполюсника 2. Напряжение на конденсаторе 8 и, следовательно, на выходе стабилизатора изменяется по линейно.му закону. Время установления переходного процесса стабилизатора в данном режиме как и любой нелинейной системы, имеющей сопутствующую нелинейность во входной цени, в десятки раз превышает tuc рассчитанное для линейного режима работы.

В стабилизаторе повышение быстродействия при больших скачках тока в нагрузке достигается за счет форсирования процесса перезарядки конденсатора 8 с по.мощью цепи нелинейной коррекции,состоящей из элементов 9-15. Цепь нелинейной коррекции не влияет на работу стабилизатора, если сигнал рассогласования мал, и наоборот, начинает функционировать при перегрузке

Q параллельно-балансного каскада, когда |и,9-и,в| мВ.

Если Ui3-Ui8 50 мВ, транзистор 16 входит в отсечку, а напряжение на эмиттере транзистора 19 начинает повторять изменение Ui9 . Это приводит к увеличению наS пряжения на диоде 13. Последний открывается, что обуславливает увеличение тока эмиттера транзистора 19 за счет перераспределения тока резистора 9 между диодами

10 и 13. Выбирая надлежащим образом сопротивления резисторов 9 и 15, можно более чем на порядок увеличить разрядный ток конденсатора 8 или во столько же раз повысить быстродействие стабилизатора.

Если напряжение на выходе стабилизатора уменьшается, причем (Dig-Uisj 50 мВ, приращение зарядного тока конденсатора 8 обеспечивается аналогичным образом через диод 14.

Для повыщения экономичности стабилизатора между общей точкой диодов 13-14 и резистором 15 рекомендуется включать дополнительный транзистор 24 (фиг. 2). Введение транзистора 24 позволяет выбирать рабочие точки вспомогательных делителей напряжений относительно малыми (порядка нескольких сотен микроампер). Это уменьшает общую мощность, потребляемую стабилизатором от источника питания в режиме холостого на выходе.

Момент включения цепи нелинейной коррекции в работу можно изменять по усмотрению разработчика путем введения в верхние плечи второго и третьего делителей напряжения не по одному, а по два диода. В некоторых случаях рекомендуется последовательно с диодами 10 и 11 вводить низкоомные резисторы.

При скачкообразном изменении напряжения эталонного источника 4 предложенный стабилизатор работает аналогично. Поэтому схема на фиг. 1 .может использоваться и в быстродействующих программируемых источниках питания, в которых уровень стабилизируемого напряжения устанавливается путем коммутации резисторов делителя выходного напряжения или путем дискретного изменения эталонного напряжения.

Формула изобретения

. Стаби.тизатор постоянного напряжения, содержащий регулирующий элемент, включенный в одну из силовых щин, токостабилизирующий элемент, включенный в общую эмиттерную цепь параллельно-балансного каскада, первый вход которого подключен к источнику опорного напряжения, второй вход - к выходу первого делителя, подключенного к выходным выводам, а выход параллельно-балансного каскада подключен к конденсатору и ко входу регулирующего элемента, отличающийся тем, что, с целью повышения быстродействия стабилизатора, в него дополнительно введены второй и третий делители напряжения, каждый из которых выполнен на резисторе и диоде, причем второй делитель включен параллельно источнику опорного напряжения, третий делитель включен между общей щиной и выходом первого делителя, а выходы третьего и второго делителей соединены через встречно включенные дополнительно введенные диоды, общая точка которых подключена к общей эмиттерной цепи параллельно-балансного каскада через дополнительно введенный резистор.

Источники информации, принятые во внимание при экспертизе

ft

-у„ -SUM

Un-SOMiЩ-f-Us

Авторы

Даты

1979-04-25—Публикация

1977-03-29—Подача