1

Изобретение относится к преобразовательной технике, в частности для систем управления тиристорными преобразователями частоты, питающимися от автономных электрических источников соизмеримой мощности, с частотой напряжения, изменяющейся в щироких пределах.

Известны системы управления преобразователями, питаюпдимися от источника с постоянной частотой напряжения питания, в которых для исключения искажений напряжения питающей сети в цепь синхронизации включают фильтры 1.

Однако в случае питания тиристорных преобразователей от автономных электрических источников соизмеримой мощности, частота напряжения которых может меняться в достаточно щироких пределах, исключить влияние искажения питающего напряжения на работу системы управления с помощью фильтров невозможно.

Наиболее близким техническим решением к данному является синхронизирующее устройство для систем управления тиристорными преобразователями частоты, питающимися от автономного энергетического источника соизмери.мой мощности, содержащее

трансформатор, ко вторичной обмотке которого подключены базы транзисторных ключей, эмиттеры которых объединены и подключены к средней точке трансформатора, и R-S триггер 2. Назначение таких формирователей синхронизирующих импульсов состоит в приведении напряжений питания, искаженных коммутационными процессами, к прямоугольным синхронным с ними импульсам. Высокая чувствительность таких схем обеспечивает отсутствие фазового сдвига между питающим напряжением и прямоугольным, соответствующим этому напряжению.

Однако при возрастании токов нагрузки коммутационные искажения напряжения питающей сети возрастают. Вследствие наличия емкости и индуктивности в контуре

5 коммутации, а также из-за наличия паразитных емкостей и индуктивностей рассеяния согласующих трансформаторов, на входе триггерных схем появляются высокочастотные помехи, которые вызывают ложное срабатывание формирователей синхронизирующих импульсов. Это значительно снижает надежность управления преобразователем.

Цель изобретения заключается в повышении надежности путем предотвращения срабатывания R-S триггера от помех, возникающих при коммутации тиристоров.

Поставленная цель достигается тем, что в синхронизирующее устройство для систем управления тиристорными преобразователями частоты, питающимися от автономного энергетического источника соизмеримой мощности, содержащее формирователь синхронизирующих импульсов, который состоит из трансформатора, к концам вторичной обмотки которого подключены базы транзисторных ключей, эмиттеры которых объединены и подключены к средней точке трансформатора, и R-S триггера, дополнительно введены четыре логических элемента И-НЕ, логический элемент ИЛИ-НЕ, датчик состояния тиристоров, блок формирования импульсов по перепаду, причем к коллектору каждого из транзисторных ключей попарно подключены соединенные последовательно логические элементы И-НЕ, выходы последних логических элементов И-НЕ соединены со входом R-S триггера, выход которого через последовательно соединенные блок формирования импульсов по перепаду и одновибратор подключен к одному из входов логического элемента ИЛИ-НЕ, выход которого подключен ко вторым входам последних попарно соединенных логических элементов И-НЕ, а второй вход соединен с выходом блока наличия коммутации, на вход которого подключен датчик состояния тиристоров.

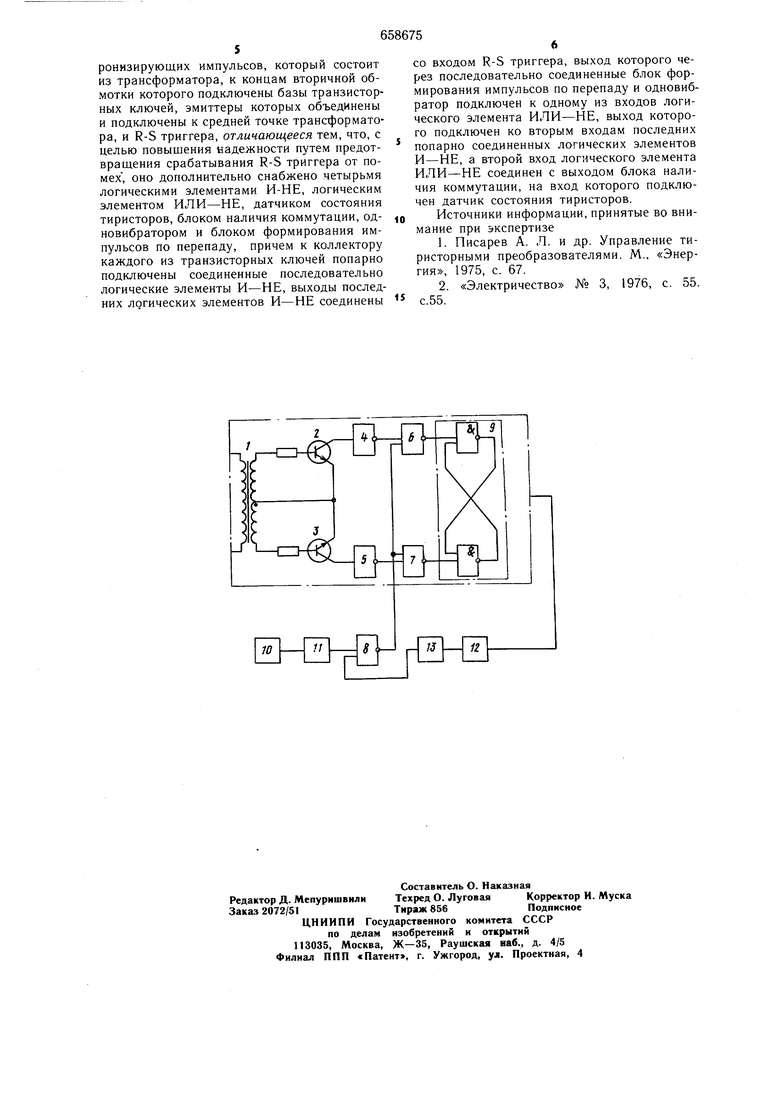

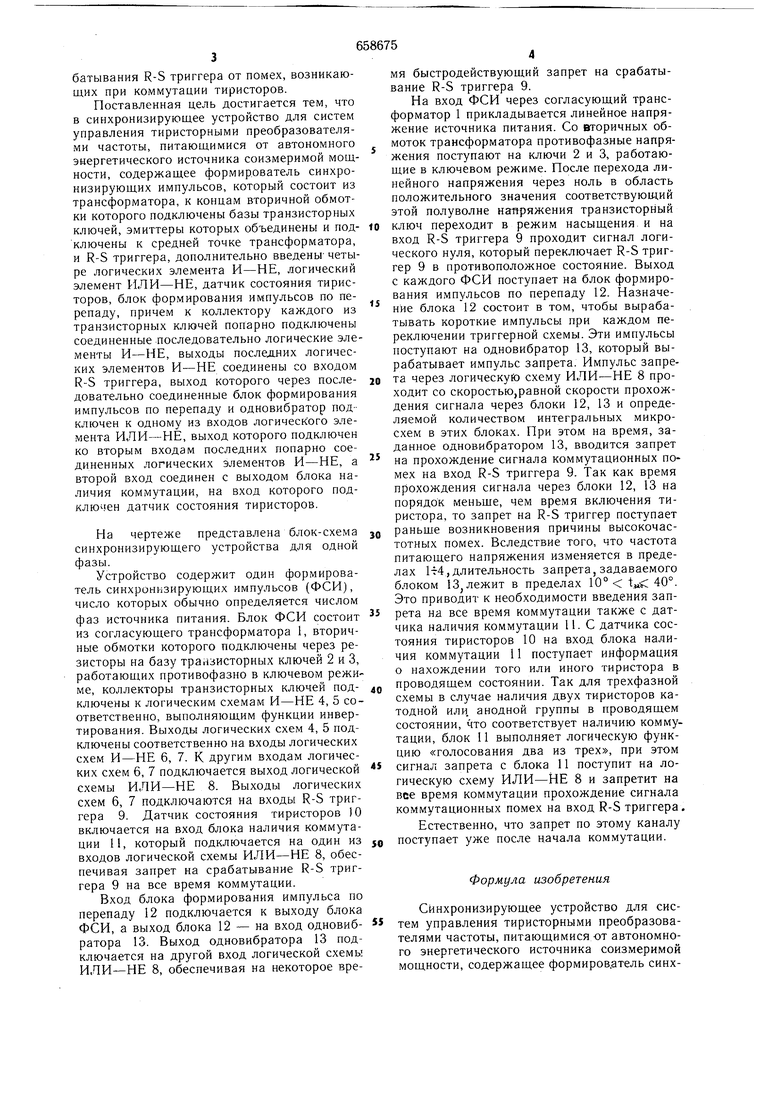

На чертеже представлена блок-схема синхронизирующего устройства для одной фазы.

Устройство содержит один формирователь синхронизирующих импульсов (ФСИ), число которых обычно определяется числом фаз источника питания. Блок ФСИ состоит из согласующего трансформатора 1, вторичные обмотки которого подключены через резисторы на базу транзисторных ключей 2 и 3, работающих противофазно в ключевом режиме, коллекторы транзисторных ключей подключены к логическим схемам И-НЕ 4, 5 соответственно, выполняющим функции инвертирования. Выходы логических схем 4, 5 подключены соответственно на входы логических схем И-НЕ 6, 7. К другим входам логических схем 6, 7 подключается выход логической схемы ИЛИ-НЕ 8. Выходы логических схем 6, 7 подключаются на входы R-S триггера 9. Датчик состояния тиристоров 10 включается на вход блока наличия коммутации 11, который подключается на один из входов логической схемы ИЛИ-НЕ 8, обеспечивая запрет на срабатывание R-S триггера 9 на все время коммутации.

Вход блока формирования импульса по перепаду 12 подключается к выходу блока ФСИ, а выход блока 12 - на вход одновибратора 13. Выход одновибратора 13 подключается на другой вход логической схемы ИЛИ-НЕ 8, обеспечивая на некоторое время быстродействующий запрет на срабатывание R-S триггера 9.

На вход ФСИ через согласующий трансформатор 1 прикладывается линейное напряжение источника питания. Со вторичных обмоток трансформатора противофазные напряжения поступают на ключи 2 и 3, работающие в ключевом режиме. После перехода линейного напряжения через ноль в область положительного значения соответствующий этой полуволне напряжения транзисторный 0 ключ переходит в режим насыщения и на вход R-S триггера 9 проходит сигнал логического нуля, который переключает R-S триггер 9 в противоположное состояние. Выход с каждого ФСИ поступает на блок формирования импульсов по перепаду 12. Назначение блока 12 состоит в том, чтобы вырабатывать короткие импульсы при каждом переключении триггерной схемы. Эти импульсы поступают на одновибратор 13, который вырабатывает импульс запрета. Импульс запрета через логическую схему ИЛИ-НЕ 8 проходит со скоростью,равной скорости прохождения сигнала через блоки 12, 13 и определяемой количеством интегральных микросхем в этих блоках. При этом на время, заданное одновибратором 13, вводится запрет на прохождение сигнала коммутационных помех на вход R-S триггера 9. Так как время прохождения сигнала через блоки 12, 13 на порядок меньше, чем время включения тиристора, то запрет на R-S триггер поступает

0 раньще возникновения причины высокочастотных помех. Вследствие того, что частота питающего напряжения изменяется в пределах 1т4,длительность запрета,задаваемого блоком 13 лежит в пределах 10° tjisC 40°. Это приводит к необходимости введения запрета на все время коммутации также с датчика наличия коммутации 11. С датчика состояния тиристоров 10 на вход блока наличия коммутации 11 поступает информация о нахождении того или иного тиристора в

g проводящем состоянии. Так для трехфазной схемы в случае наличия двух тиристоров катодной или. анодной группы в проводящем состоянии, что соответствует наличию коммутации, блок 11 выполняет логическую функцию «голосования два из трех, при этом

s сигнал запрета с блока 11 поступит на логическую схему ИЛИ-НЕ 8 и запретит на все время коммутации прохождение сигнала коммутационных помех на вход R-S триггера. Естественно, что запрет по этому каналу

поступает уже после начала коммутации.

Формула изобретения

Синхронизирующее устройство для систем управления тиристорными преобразователями частоты, питающимися от автономного энергетического источника соизмеримой .мощности, содержащее формиров.атель синхронизирующих импульсов, который состоит из трансформатора, к концам вторичной обмотки которого подключены базы транзисторных ключей, эмиттеры которых объединены и подключены к средней точке трансформатора, и R-S триггера, отличающееся тем, что, с целью повышения надежности путем предотвращения срабатывания R-S триггера от помех, оно дополнительно снабжено четырьмя логическими элементами И-НЕ, логическим элементом ИЛИ-НЕ, датчиком состояния тиристоров, блоком наличия коммутации, одновибратором и блоком формирования импульсов по перепаду, причем к коллектору каждого из транзисторных ключей попарно подключены соединенные последовательно логические элементы И-НЕ, выходы последних лдгических элементов И-НЕ соединены со входом R-S триггера, выход которого через последовательно соединенные блок формирования импульсов по перепаду и одновибратор подключен к одному из входов логического элемента ИЛИ-НЕ, выход которого подключен ко вторым входам последних попарно соединенных логических элементов И-НЕ, а второй вход логического элемента ИЛИ-НЕ соединен с выходом блока наличия коммутации, на вход которого подключен датчик состояния тиристоров. Источники информации, принятые во внимание при экспертизе 1.Писарев А. Л. и др. Управление тиристорными преобразователями. М., «Энергия, 1975, с. 67. 2.«Электричество № 3, 1976, с. 55. с.55.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронизирующее устройство | 1978 |

|

SU687543A1 |

| Трехфазный тиристорный ключ | 1979 |

|

SU851777A1 |

| Устройство для управления тиристорным инвертором | 1978 |

|

SU767933A1 |

| Устройство для управления тиристорными преобразователями | 1977 |

|

SU666625A1 |

| Динамический Д-триггер | 1982 |

|

SU1019593A1 |

| Устройство для коммутации переменного напряжения | 1985 |

|

SU1272369A1 |

| Устройство для управления реверсивным тиристорным широтноимпульсным преобразователем | 1976 |

|

SU657568A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ МИНИМАЛЬНЫХ УГЛОВ УПРАВЛЕНИЯ | 2019 |

|

RU2709026C1 |

| Устройство для управления циклоконвертором с прямоугольным управляющим напряжением | 1973 |

|

SU588611A1 |

| Способ управления циклоконвертором и устройство для его осуществления | 1974 |

|

SU570182A1 |

п

Авторы

Даты

1979-04-25—Публикация

1977-03-05—Подача