ного и бесперебойного питания потребителей электроэнергии через преобразователь.

Целью изобретения является повышение на.дежности преобразователя.

Достигается это тем, что в способе управления тиристорным преобразователем, состоящем в том, что формируют управляющие импульсы длятй ристоров с помощью основдай или резервной системы импульсно-фазового управления (СИФУ), формируют сигнал на вклкшение преобч разователя в работу, отключение и автоматическое повторное включение (АПВ) с помощью логических блокйв формирования уровней разрешающих или запрещающих работу СЙФУ и блоков АПВ, фиксируют момент времени неуспещного АПб и формируют сигнал на вклчение резервной СИФУ, осзшествляют успещности переключения на резервную СИФУ и формируют сигнал, отказ в случае неуспешного переключений, а также неуспешного АПВ при работе преобразователя от резервной СИФУ включают преобразователь после устранения отказа. --- .;.. -....-. :. :

Устройство для осуществления способа управления тиристориьгм преобразователем, содержащее основной и резервньгй блоки импульснофазового управления (СЙФУ), основной и резервный логические блоки формирования уров ней, разрешаюидих или запрещающих работу СИФУ, каждьтй из которьрс содержит по два логических элемента ИЛИ, вьосбдкгТёоТорйх .подключены к входу триггера, а выход триггера подключен соответственно к СИФУ основного и р1езервногр блоков, основной и резервный блоки автоматКетеского повторного включе ния АПВ, цепи сигналов на включение,на отключение и защиты, причем вход основного блока АПВ соединен с входом одного нз элементов ИЛИ основного блока формирования уровней, а выход основногс блока АПВ - с входом другогоэлемента илитого же блока, выход резервного блока АПВ иодКЛ1очен к входу первого логического .элемента ИЛИ резервного блока формирования уровней, дополнительно снабжено первым и вторым элемента ми задержки, триггером Т-типа, логическим дв)о;входо:вым элементом ИЛИ, тремя даухвходовыми логическими элементами И ifa° Bxoдах каждого логического блока формирования уровнен разреищошего или залрещающего работу СИФУ и блоком контроля переключения, а основные н резервные фюйи автоматического повторного вклгэчения АПВ снабжены цепями сигаала о неуспешном АПВ, при«ЙгмвЖШи atopbrb эпемеятов задержки соединены с цепью сигнал о неуспешном АПВ основного узла АПВ, выход первого элемента задержки соединен с входом триггера, выходы которого соединены с

входами логических элементов И соответственно основного и резервного блоков формирования уровней, разре иающих или запрещающих работу СИФУ, второй вход первого элемента И основного блока формирования уровней подключен к цепи сигнала на включение преобразователя, вторые входы вторых элементов И соответствующих блоков подключены к цепи сигнала на выключение преобразователя, вторые входы третьих элементов И соответстующиХ блоков - к цепи сигнала зашиты преобразователя, выход второго элемента задержки под ключен к одному Входу логического элемента ИЛИ, второй вход которого подключен к цепи сигнала на включение преобразователя, а выход соединен с вторь1м входом первого логического элемента И резервного блока формирования уровней разрешающего или запрештбщего работу СИФУ, выходы первых элемеетов И соединены соответственно каждый с одним иэ входом первых элементов ИЛИ б.г1оков формирования уровней, а выходы вторых и третьих элементов И с входами вторых элементов ИЛИ указанных блоков. При это1Й блок контроля переключения содержит одновибратор, первый и второй логические двуХвХоДоBbie элементы И, логический элемент НЕ и логический двухвходовои элемент ИЛИ, причем вход одновифатора соерлнен с цепью сигнала о неуспешном АПВ основного блока АПВ, выход одновибратора соед}шен С входом логического элемента НЕ и с одним входом первого логткескбго элемента И, на второй вход которого, соединенного с одаим входом второго логического элемента И, подключена цепь сигнала защиты с выхода одного нз логических элементов И резервного блока формирования уровней разреишощего или запрещающего работу СИФУ, выход первого логического элемента И соединён с входом резервного блока АПВ, втйрой вход второго логического элемента И соединен с выходом логического элемента НЕ, выход второго логического элемента И соединёй с входом лопгческого элемента ИЛИ, на второй вход которого подключена цеп сигнала о неуспеилном АПВ резервного блока АПВ, а выход логического элемента ИЛИ соеданёя с iJieftfiiR) яндикашта сигнала Отказ.

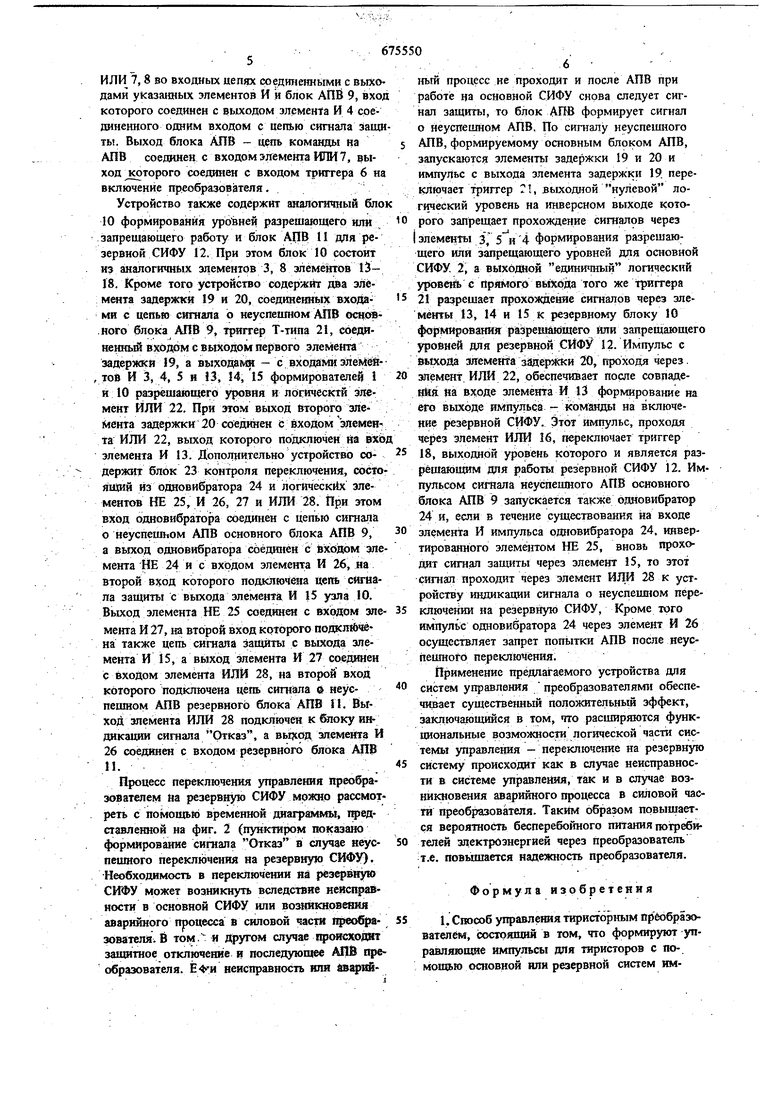

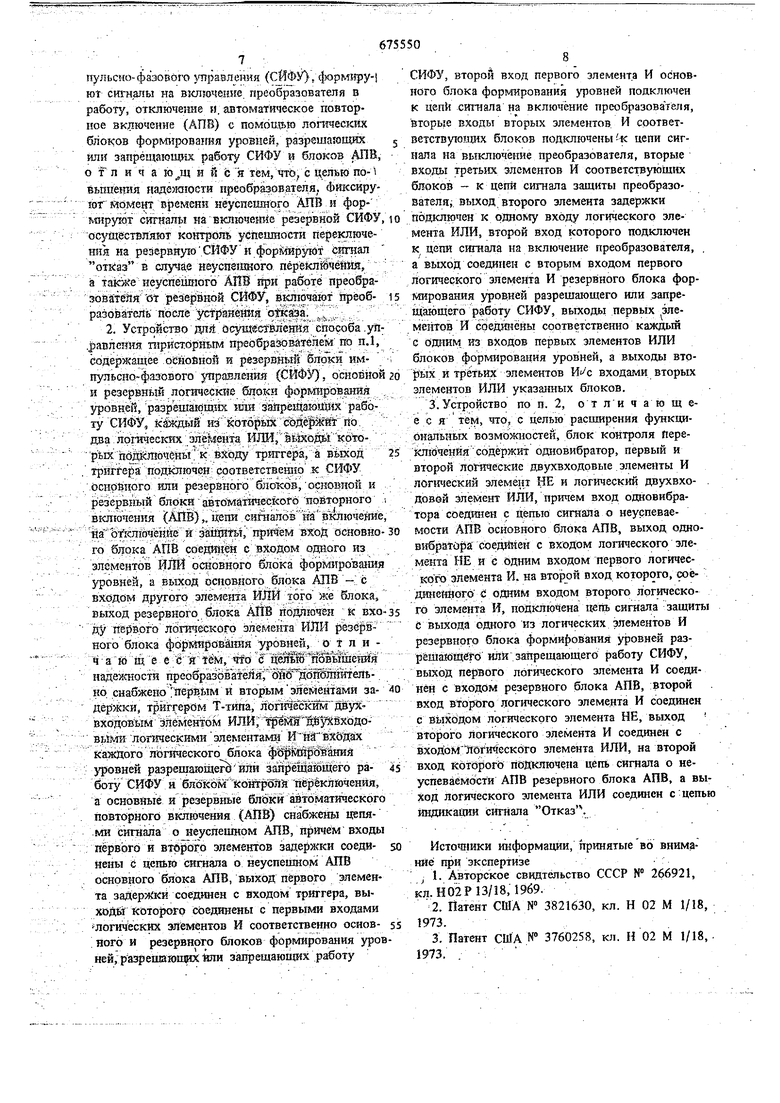

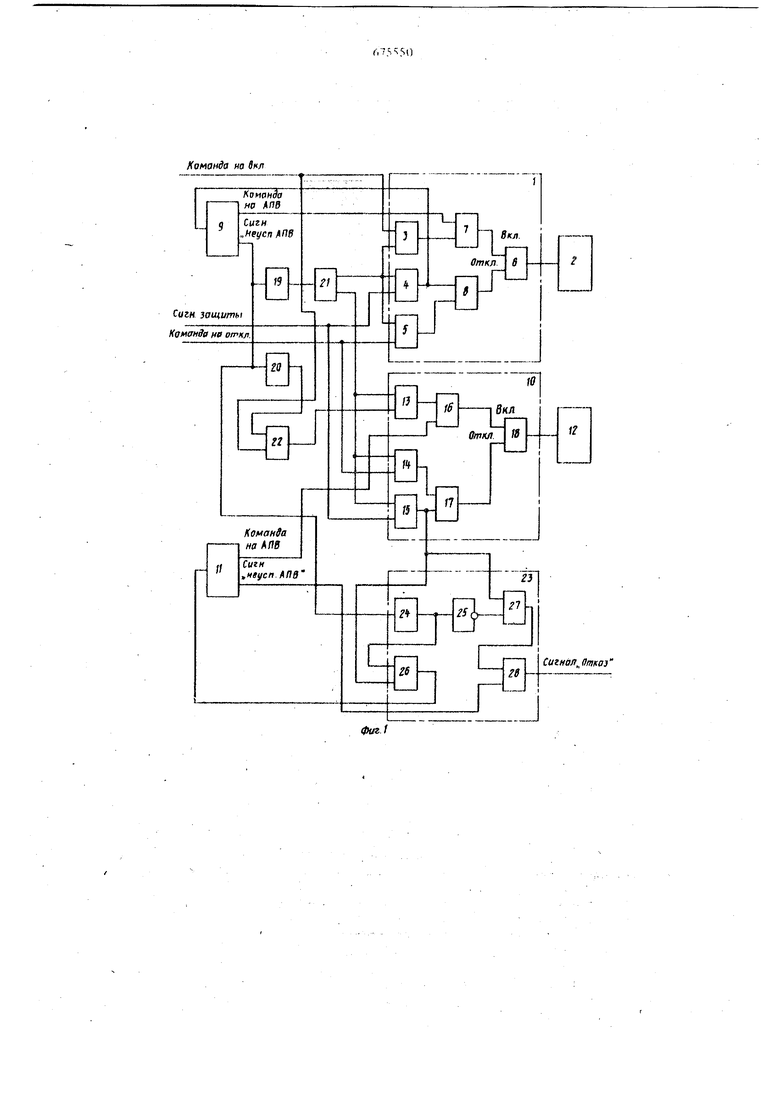

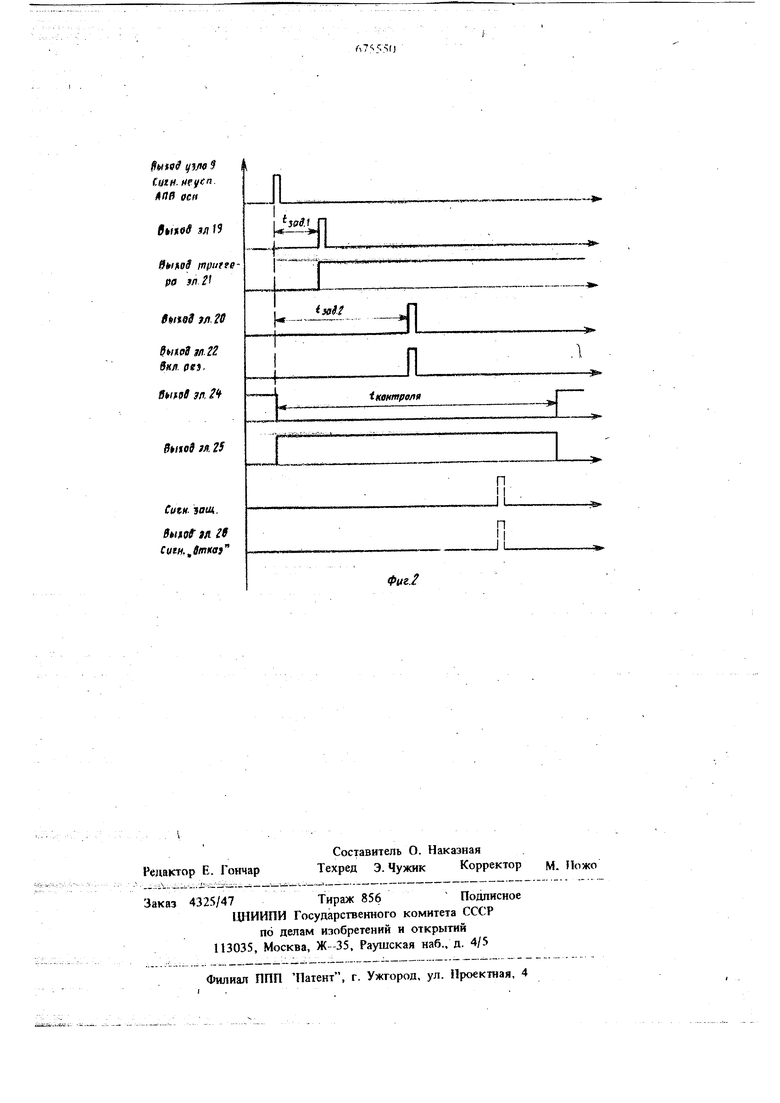

На фиг. i приведена функциональная схема устройства для реализации предлагаемого способа, на фиг. 2 - временные диаГракаол.

Устройство содержит блок 1 формирования уровней разрешающего или запрещающего работу основиой СИФУ 2, состоящий из трех двухвходовых логических элементов И 3, 4, 5, связаннь1Х однями входами с цепями сигнала на включение шш отключение преобразователя и триггера 6 с разделительными входами и двумя jCByxBXoScffliJMH логическими элементами ИЛИ 7, 8 во входных цепях ооедииенными с выхо дами указанных элементов И и блок АПВ 9, вхо которого соединен с выходом элемента И 4 соединенного одним входом с цепью сигнала защи ты. Выход блока АПВ цепь командь на АПВ соединен с входом элемеига ИЛИ 7, выход jcoroporo соединен с входом триггера 6 на включение преобразователя. Устройство также содержит аналогичный бло 10 формирования уровней разрешающего или запрещающего работу и блок АЦВ 11 для резервной СИФУ 12. При этом блок 10 состоит из аналогичных элементов 3, 8 элёме нтов ISIS. Кроме того устройство содержит два элемента задержки 19 и 20, соединешп.1Х входами с цепью сигнала о неуспешном АПВ основ.ного блока АПВ 9, триггер Т-тина 21, соединенный входом с выходом первого элемента задержки 19, а выходами - с входами эДемёйтоВ И 3, 4, 5 и 3, 14, 15 формирователей 1 и 10 разрешающего уровня и лосическтй элемент Й.ПЙ 22. При этом вьрсод Второго элемента задержки 20 соединен с входомэлемента ИЛИ 22, выход которого подключен на вхо элемента И 13. Дополнительно устройство содержит блок 23 контроля переключения, состо ящий из одновиёратора 24 и логических элементов НЕ 25, И 26, 27 и ИЛИ 28. При этом вход одновибратора соединен с цепью сигнала о неуспешном АПВ основного блока АПВ 9, а выход одновибратора соединен с взсОдом эле мента НЕ 24 и с входом элемешга И 26, на второй вход которого подключеяа цепь сигнала защиты с выхода элемента. И 15 узла 10. Выход элемента НЕ 25 соединен с входом злемента И 27, на второй вход которого подасшбчена также цепь сигнала защиты с выходц элемента И 15, а выход элемента И 27 соединен с входом элемента ИЛИ 28, на второй вход которого подключена цепь сигнала 0 неуспешном АПВ резервного блока АПВ 11. Выход элемента ИЛИ 28 подключен к блоку индикации сигнала Отказ, а элемента И 26 соединен с входом резервного блока АПВ 11. . . / - ;. Процесс переключения управления Преобразователем Иа резервную СИФУ можно рассмотреть с помощь(Ь временной диаграммы, щ едставленной на фиг. 2 (пунктиром показано формирование сигнала Отказ в случае неуспешного переключения на резервную СИФУ). Необходимость в переключении яа резервную СИФУ может возникнуть вследствие неисправности в основной СИФУ или возникновения аварийного процесса в силовой :асти преобразователя. В том. и другом случае прсжсходят защитное отключение и последующее ЛИВ преобразователя. Ёфи неисправность юш ный процесс не проходит и после АПВ при pa6oTie на основной СИФУ снова следует сигнал защиты, то блок АГЯВ формирует сигнал о неуспешном АПВ. По сигналу неуспешного АПВ, формируемому основным блоком АПВ, запускаются элементы задержки 19 и 20 и импульс с выхода элемента задержки 19. переключает триггер Г, выходной нулевой логический уровень на инверсном выходе которого эапрещает прохождение сигналов через лементы з7 4 формирования разрешающего или запрещающего уровней для основной СИФУ. 2, а выходной единичный логический уровень с прямого Bbixojta того же триггера 21 разрешает прохождение сигналов через элементы 13, 14 и 15 к резервному блоку 10 формирования ра:5реша бщего или запрещающего уровней для резервной СИФУ 2. Импульс с выхода эяеме1Йа 315держки 20, проходя через. этемент ИЛИ 22, обеспечивает после совпадения на входе элемента И U формирование на его выходе ямпудьса - команды на включение резервной СИФУ. Этот импульс, проходя через элемент ИЛИ 16, переключает триггер 18, выходной уровень которого и является разрешающим дая работы резервной СИФУ 12. Импульсом сигнала неуспешного АПВ основного блока АПВ 9 запускается также одновибратор 24 и, если в течение существования на входе элемента И импульса одновибратора 24, инвертированного элементом НЕ 25, вновь проходит сигнал защиты через элемент 15, то этот сигнал проходит через элемент ИЛИ 28 к устройству индикации сигнала о неуспешном переключении на резервную СИФУ, Кроме того импульс одновибратора 24 через элемент И 26 осуществляет запрет попЬ1тки АПВ после неуспешного переключения. Применение предлагаемого устройства для систем управления преобразователями обеспечивает существе1шьш положительный эффект, заключающийся в том, что расширяются функциональные возможности логической частя системы управления - переключите на резервную систему происходит как в случае неисправности в системе управления, так и в случае возникновения аварийного процесса в силовой части преобразователя. Таким образом повышается вероятность бесперебойного питания потребителей электроэнергией череэ преобразователь т.е. повышается надежность преобразователя. Формула изобретения 1. Способ управления тиристорным прбобразователём, состоящий в том, что формируют управляющие импульсы для тиристоров с помовдью основной или резервной систем импульсно-фазового Т7равления (СЙФУ), ют сигналы на включение, преобразователя в работу, отключе ше н, автоматическое повторное вк Iючeинe (АПВ) с noMotiaro Boni ieciaix блоков формирования уровней, разрешающих ИЛ запреща101Щ5х работу СИФУ и блоков АПЙ, о f л и ч а 10,щ н и ся тем, что, с целыо по-i вьинения иаде 0юстя преобр рвателя, Фиксируюткймент времени успешного АПВ и фор-: сигналы на взспючешю резервной СИФУ, осуйцествляют контроле усйешиости переключения на резервную .СЙФУ н форйй|зуют ciinian отказ в случае неуспгикного пёреклйчеШш, а такйче неуспешного АЛВ ври работе преобразователя ОТ резервной СИФУ, включают преобразователь после устрзнеймя «stKsaa.

2. Устройство дня осущеетвлеш я способа управления тиристорньил преобразователем ш пЛ, содержащее осиойной и резервный блоки импульсно-фазового -правления (СНФУ), основной и резервный логические блоки формирования уровней, разрешающих, ияи запрещающих работу СИФУ, кажда1й из которых содерйсйт по два лопсчесйта элемента ИЛИ, выходы которых подключены к входу триггера, а выход триггера подключен соответствещю к СИФУ ociiofiiroro или резервного блоков, основной и резервный блоки авточ атдаеского повторного включения (АПВ)„ цепк сигаапоз на включенне, на отключение и , вход основного блока АПВ соединён с входом одного из элементов ИШ-t основного блока формировшшя j-pOBHcE, а выход основного блока АПБ - с входом другого элемента ИЛИ того же блока, выход резервного блока АПВ нодаючен к входу первого лоппеского элемента ИЛИ резервного блока форшгровйшя : о8ней, отличающееся 1ем, 4to с нёльШ повышения надеяшости преобразователи, 6Ш допо лнительно снабжено первым н вторым элементами задержки, триггером Т-тина, логн ёским двухвходовьш зламентом ИЛИ, tge ухйходовглми логическ1шн элементами И иа вхЬдах каждого логического блока фЭрКш сйГаний jpOBHefi раэрешагощегЬ или запре1ша1ощего работу СИФУ я блоком контролй переключения, а основные и резервные блЬкй автоматического повторного включения (АПВ) снабжены цепями сшЦала о неуспешном АПВ, причем входы первого и втр)рог;о злементов задержки соедийены с цепЫб сигнала о неуспешном АПВ основного блока АПВ, выход первого элемента задер-лйкй соединен с входом триггера, выхоДй Которого соединены с первыми входами логических элементов И соответственно основного и резервного блоков формирования уровней;р;аз|зеи1ающих ли 3ianpema ou0fx работу

8

СИФУ, второй вход первого элемента И основного блока формирования уровней подключен к цепи на включение преобразователя, вторые входы BTopbJX злементов И соответветствугогцих блоков подключены-к цепи сигнала на выключение преобразователя, вторые входы третьих злементов И соответствующих блоков - к деп11 сигнала защиты преобразователя; выход второго элемента задержки подключен к однокгу входу логического элемента ИЛИ, второй вход которого подключен к, цепи сигнала на включение преобразователя, а выход соединен с вторым входом первого логического элемента И резервного блока формирования уройней разрешающего или запрещающего работу СИФУ, выходь первых элементов И соединены соответстве1шо каждый с одннм, из входов первых элементов ИЛИ блоков формирования уротей, а выходы вторых и третьих элементов входами вторых элементов ИЛИ указазшых блоков.

3. Устройство по п. 2, от л и ч а ю щ ее с я тем, что, с целью расширения функщ оналы1ых возможностей, блок контроля переключения содержит ощювибратор, первый и второй логические двухвходрвые элементы И лопиеский элемент НЕ и логический двухвходовей элемент ИЛИ, причем вход одновибратора соединен с цепью сигнала о неуспеваемости АПВ основного блока АПВ, выход одновибратора соединен с входом логического элемента НЕ и с одним входом первого логического элемента И. на второй вход которого, соединенного с одним входом второго логического элемента И, подключена Цепь сигнала защит с выхода одного из логических элементов И резервного блока формирования уровней разргя1аюЩ№о иЛй запрещающего работу СИФУ, выход первого логического злемента И соединен с входом резервного блока АПВ, второй вход второго логического элемента И соединен с выходом логического элемента НЕ, выход второго логического элемента И соединен с входом Логи еск6го элемента ИЛИ, на второй вход которого Ньдключена цепь сигнала о неуспеваемости АПВ резервного блока АПВ, а выход Логического элемента ИЛИ соединен сцеп йнднкагдаи ciiniana Отказ

Источники информации, принятые во внимание при экспертизе

1. Авторское свидтельство СССР № 266921, КЛ.Н02Р 13/18, 1969.

2.Патент США № 3821630, кл. Н 02 М 1/18 1973.

3.Патент США N 3760258, кл. Н 02 М 1/18 1973.

D

Камома на ЦПВ

Сиги ,Иеусп АПВ

Сигн защити

КомамЗв на .

ZQ

щ..

Откл.

иП

г

:J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления тиристорным преобразователем | 1985 |

|

SU1259439A2 |

| Устройство для управления тиристорным преобразователем | 1979 |

|

SU942239A1 |

| Устройство автоматического повторного включения тиристорного преобразователя | 1976 |

|

SU564677A1 |

| Регулятор напряжения для преобразователя переменного тока в постоянный | 1974 |

|

SU909787A1 |

| Регулятор напряжения для преобразователя переменного тока в постоянный | 1984 |

|

SU1229913A2 |

| Устройство для защиты тиристорного инвертора напряжения | 1981 |

|

SU1023516A2 |

| Электропривод постоянного тока с реверсором | 1981 |

|

SU1008874A1 |

| Способ трехфазного автоматическогопОВТОРНОгО ВКлючЕНия лиНии элЕКТРО-пЕРЕдАчи и уСТРОйСТВО для ЕгО ОСу-щЕСТВлЕНия | 1979 |

|

SU843074A1 |

| Регулятор напряжения для преобразователя переменного тока в постоянный | 1981 |

|

SU1029384A2 |

| Устройство автоматического повторного включения | 1986 |

|

SU1361667A1 |

Ко1иан8а на П0

Сигн tHtycn.Ang

12

втм.

Sv.

.

гз

21

Яб-CutHM,,Отказ

гь

Авторы

Даты

1979-07-25—Публикация

1976-11-19—Подача