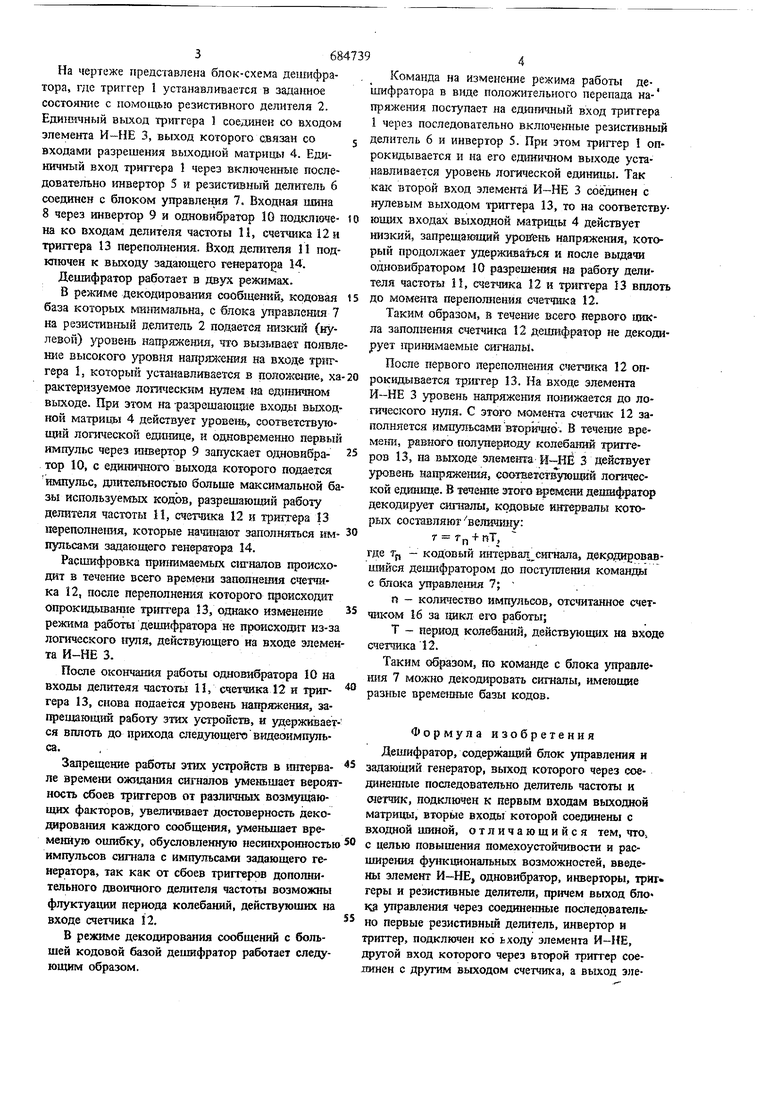

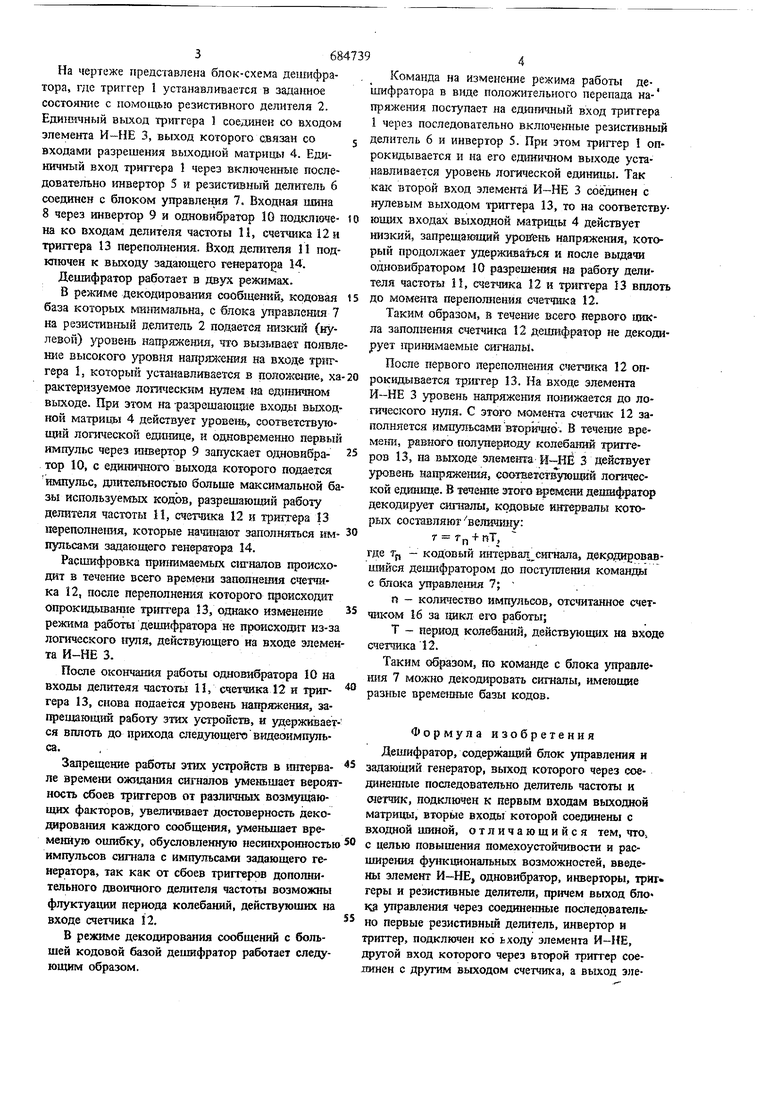

Изобретение относится к области автоматики и телемеханики и может быть использовано для1 преобразования двоичной записи переданного сообщения в команду. Известны, дешифраторы кодовых интервалов времени, содержащие генератор, блок управления и преобразовательный блок 1 . Недостатком этих дешифраторов является HHa кая помехоустойчивость. Кроме того, известны дешифраторы, содержащие источник сообщений, задающий генератор, блок управления и дискретную линию задержки, выполненную на базе счетчика импульсов и делителя частоты и соединенную с выходной матрн цей 2. Недостатками зтих устройств являются низкая помехоустойчивость, вызванная сбоями триггеров Н помехами, действующими в цепях питания и шинах заземления, а также невозможность работы деигафратора, при декодировании сигналов, кодовые интервалы которых составляют разные временные базы. Цель изобретения - повышение помехоустойчивости и расширение функциональных возможностей дешнфратора. Данная цель достигается тем, что в дешифратор, содержащий блок управления и задающий генератор, выход которого через соединенные яоследовательно делитель частоты и счетчик подключен к первым входам выходной матриии, вторые входы которой соединены с входной шиной, введены элемент И-НЕ, одновибратор, инверторы, триггеры и резистивные делители, причем выход блока управления через соединенные последовательно первые резистивный делитель, инвертор и триггер, подключены ко входу злемента И-НЕ, другой вход которого через второй триггер соединен с другим йыходом счетчика, а выход элемента И-НЕ, подключен к третьим входам ВЫХОШ10Й матрицы, при этом входная щииа через второй инвертор и одновнбратор соединена с другикш входами делителя частоты, счетчика и второго триггера, кроме того другой вход первого триггера через второй резистивкый делитель подключен к шине питания. 3684 На чертеже представлена блок-схема деитяфратора, где триггер 1 устанавливается в зада1{ное состояние с помощью резистивкого делителя 2. Едиюетный выход rpinrepa 1 сое динек со входом элемента И-НЕ 3, выход которого со входами разрешения выходной матрицы 4. Единичный вход т ип-ера 1 через включенные последовательно liHBeptop 5 и резистивный делитель б соединен с блоком управления 7. Входная ишна 8 через инвертор 9 и одновибратор 10 подаслютена ко входак делителя частоты 11, счетчика 12 и триггера 13 переполнения. Вход делителя 11 подключен к выходу задающего генератора 14. Деихифратор работает в двух режимах. В режиме декодировагшя сообщений, кодовая база которых ми1шмальна, с блока уирааления 7 на резистианый детггель 2 подается низкий (кулевой) зфовень напряжения, что вызьшает по1тле ние высокого уровня напряжения на входе трнггера 1, который устш1авливается в полойдание, характеризуемое лопиескнм нулем ш едмпршом выходе. При этом на -paspemaroiisie входя выходной матриць 4 действз т уровень, соответствующий логической ед1пшце, и одновременно первый импульс через инвертор 9 запускает одновибратор 10, с единичного выхода которого подается импульс, длителыюстыо больше максимальной ба зы используемых кодов, разрешающий работу целителя частоты И, счетчзжа 12 и триггера 13 переполнения, которые нащщают заполняться импульсаквй задающего генератора 14. Расшифровка пршгамаемых сигналов происходит в течение всего време ш запопнения счетчика 12, после переполнения которого происходит опрокидьшание триггера 13, однако изменение режима работы дешифратора не происходит из-за логаческого нупя, действующего на входе элемен та И-НЕ 3. После окончания работы одновибратора 10 на входы делителя частоты 11, счетчика 12 и триггера 13, снова подается уровень напряжения, запрещающий работу этих устройств, а угзьержнвает ся вплоть до прихода следующего видеоимпульса. Запрещение работы этих устройств в шггервале времени ожидания сигаалов уменьшает вероят ность сбоев триггеров от различных возмущающих факторов, увеличивает достоверность декодирования каждого сообщения, уменышет временную ощибку, обусловленную несиихронностьш

импульсов сигнала с импульсами задающего генератора, так как от сбоев триггеров допожштельвого двоичного делителя частоты возможны флуктуации периода колебаний, действующих на входе счетчика 12.

В режиме декодирования сообщений с 6o;ibщей кодовой базой дещифратор работает следующим образом.

ширешш футсвдональных возможностей, введены элемент И-НЕ, одновибратор, инверторы, триггеры и резистивные делители, nptweM выход бло« ка управления через соединенные последователь.но первые резистивный делитель, инвертор и триггер, подключен ко входу элемента И-НЕ, другой вход которого через второй триггер соелинен с другим выходом счетчика, а выход элеКоманда на изменение режима работы деифратора в виде положительного перепада наряжения поступает на едгашчный вход триггера 1 через последовательно включенные резистивный елитель 6 и инвертор 5. При этом триггер 1 опрокидывается и на его едашичном выходе устанавливается уровень логической единицы. Так как второй вход элемента Й-ИЕ 3 соединен с нулевым выходом триггера 13, то на соответствующих входах выходаой матрицы 4 действует низкий, запрещающий уровгень напряжения, который продолжает удерживаться и после выдачи одновибратором Ш разрешения на работу делителя частоты 11, счетчика 12 и триггера 13 вплоть до момента переполнения счетчика 12. Таким образом, в течение всего первого цикла заполнения счетчика 12 дешифратор не декодирует тринимаемые сигнальь После первого переполнения счетчика 12 опрокидывается триггер 13. На входе элемента И-НЕ 3 уровень напряжештя по1шжается до логического нуля. С этого момента счетчик 12 заполняется импульсамивторишо. В течение времеш5, равного ползшериоду колебаний триггеров 13, на выходе элемента И-НЕ 3 действует уровень напряжения, еоошаегсшузощий логической единице. В течение этого времени дешифратор декодирует сигналы, кодовые интервалы которых coci-аБляюг велйздаху: г Tf, -f пТ, где Гр - кодовый интервал сигнала, декрдировавшнйся дешифратором до поступления команды с блока управле шя 7; п - количество импульсов, отсчитанное счетчиком 16 за цикл его работы; Т - период колебаний, действующее на входе счетчика 12. Таким офазом, по команде с блока управлешш 7 можно декодировать сигналы, имеющие време1пяые базы кодов. Формула изобретения Дешифратор, содержащий блок управления и задающий генератор, выход которого через соединенные последовательно делитель частоты и (нетчик, подключен к первым входам выходной матрищ, вторьш входы которой соединены с входной шиной, отличающийся тем, что, с целью повышения помехоустойчивости и рас56847396

мента И-НЕ, подключен к третьим входам вы-Источники информации, принятые во внимэ

ходной матрицы, при этом входная шина черезние при экспертизе

второй инвертор и одновибратор соединена с-1. Авторское свидетельство СССР V 365039,

другими входалж делителя/ частоты, счетчика и

второго триггера, кроме того другой вход первого .триггера через второй резнстивный делитель подключен к шине питашш.

кл. Н 03 13/24, 04.06.70.

2. Глобус И. А. Двоичное кодирование в синхронных системах - Изд. Связь, М., 1972, с. 75.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор | 1978 |

|

SU748870A1 |

| ЭЛЕКТРОННОЕ КОДОВОЕ УСТРОЙСТВО | 2000 |

|

RU2179223C2 |

| Устройство для стабилизации вакуума | 1983 |

|

SU1149060A1 |

| Самонастраивающееся устройство управления | 1983 |

|

SU1130830A1 |

| КОДОВОЕ УСТРОЙСТВО | 2000 |

|

RU2184825C2 |

| КОДОВОЕ УСТРОЙСТВО | 1991 |

|

RU2016179C1 |

| Цифровое устройство для коммутации симистора | 1982 |

|

SU1039005A1 |

| Формирователь импульсов | 1989 |

|

SU1626353A2 |

| Устройство для генерирования функционально изменяющихся напряжений | 1979 |

|

SU903916A1 |

| МАГНИТОСТРИКЦИОННЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2109399C1 |

Авторы

Даты

1979-09-05—Публикация

1977-04-06—Подача