1

Изобретение относится к импульсной технике и может быть использовано в измерительной технике.

Известен преобразователь, содержащий триггеры, дифференцирующие цепи, элементы И, ИЛИ, формирователь эталонного интервала времени, делитель частоты и генератор образцовой частоты 1.

Наиболее близким техническим решением к изобретению является преобразователь частоты-код, содержащий триггер выделения разностного интервала, один вход которого соединен с выходом счетчика формирователя эталонного интервала времени и одним входом триггера формирователя эталонного интервала времени, другой вход триггера выделения разностного интервала соединен с выходом формирователя интервала времени, соответствующего нескольким периодам следования входной импульсной последовательности, вход которого через входной элемент И соединен с выходом триггера управления входным элементом И, а выход - с входом триггера управления входньм : лементом И и входом триггера выделения интервала времени, соответствующего нескольким

периодамследования входной импульсной последовательности, другой вход которого соединен с входом формирователя интервала времени, соответствующего нескольким периодам следования входной импульсной последовательности, а выход - с входом триггера формирователя эталонного интервала времени, выход которого через

0 элемент И формирователя эталонного интервала времени подключен к счетчику формирователя эталонного интервала времени, другой выход триггера выделения интервала времени, соот5ветствующего нескольким периодам следования входной импульсной последовательности, через первый элемент И подключен к входу первого управляe югo делителя частоты, причем

0 другой вход первого элемента И и элемента И формирователя эталонного интервала времени подключен к выходу генератора образцовой частоты, а выход триггера выделения разност5ного интервала времени подключен к входу управляющего триггера, выход которого через первую дифференцирующую цепь подключен к входу элемента ИЛИ, а другой выход через вторую 0 дифференцирующую цепь соединен с

установочными входами счетчика формирователя эталонного интервала времени, первого управляемого делителя частоты, счетчика измерения периода входной импульсной последовательности и триггера управления входным элементом И и непосредственно - с управляющим входом выходного элемента И, импульсный вход которого подключен к счетчику формирователя эталонного интервала времени а выход - к второму входу элемента ИЛИ, выходы которого через вторые элементы И соединены с установочными входами счетчика формирователя эталонного интервала времени, приче вторые входы вторых элементов И соединены с потенциальными выходами счетчика измерения периода следования входной импульсной последовательности 2 .

Оба эти преобразователя обладают сравнительно невысоким быстродействием.

Цель изобретения - повышение бысродействия преобразователя.

Для этого в преобразватель частота-код, содержащий триггер выделени разностного интервала, один вход которого соединен с выходом счетчика формирователя эталонного интервала времени и с одним входом триггера формирователя эталонного интервала времени, другой вход триггера выделения разностного интервала соединен с выходом формирователя интервала времени, соответствующего нескольким периодам следования входной импульсной последовательности, вход которого через входной элемент И соединен с выходом триггера управл ения входным элементом И, а выход - с входом триггера управления входным Э5рементом И и входом триггера выделения интервала времени, соответствующего нескольким периодам следования входной импульсной последовательности, другой вход которого соединен с входом формирователя интервала времени, соответствующего нескольким периодам следования входной импульсной последовательности, а выход - с входом триггера формирователя эталонного интервала времени, выход которого через элемент Ti формирователя эталонного интервала времени подключен к счетчику формирователя эталонного интервала-времени, другой выход триггера выделения интервала времени, соответствующего нескольким периодам следования входной импульсной последовательности, через первый элемент И подключен к входу первого управляемого делителя частоты, причем другой вход первого элемента И и элемента И формирователя эталонного интервала времени подключен к выходу генератора образцовой частоты, а выход триггера выделения разностного интервала времени подключен к входу управляющего триггера, выход которого через первую дифферениирующую цепь подключен к входу элемента ИЛИ, а другой выход через- вторую дифференцирующую цепь соединен с установочными входами счетчика формирователя эталонного интервала времени, первого управляемого делителя частоты, счетчика измерения периода входной импульсной последовательности и триггера управления входным элементом И и непосредственно - с управляющим входом выходного элемента И, импульсный вход которого подключен к счетчику формирователя эталонного интервала времени, а выход - к второму входу элемента ИЛИ, выходы которого через вторые элементы И соединены с установочными входами формирователя эталонного интервала времени, причем вторые входы вторых элементов И соединены с потенциальными выходами счетчика измерения периода следования входной импульсной последовательности, введены второй управляемый делитель частоты, первый и второй дополнительный элемент И, дешифратор нулевого состояния, две дополнительные дифференцирующие цепи, дополнительный триггер и реверсивный счетчик, входы которого через первый и второй дополнительные элементы И соединены с генератором образцовой частоты, а нулевые выходы - через дешифратор нулевого состояния с одним из входов дополнительного триггера, другой вход которого через первую дополнительную дифференцирующую цепь соединен с выходом триггера вьщеления разностного интервала и вторым входом первого дополнительного элемента И, а выход дополнительного триггера через вторую дополнительную дифференцирующую цепь соединен с вторым входом управляющего триггера и вторым входом второго дополнительного элемента И, выход которого соединен с входом счетчика формирователя эталонного интервала времени, вход второго управляемого делителя частоты соединен с выходом первого управляемого делителя частоты, установочный вход- с входом триггера управления входным элементом И, а выход - с входом счетчика измерения периода следования импульсов входной импульсной последовательности .

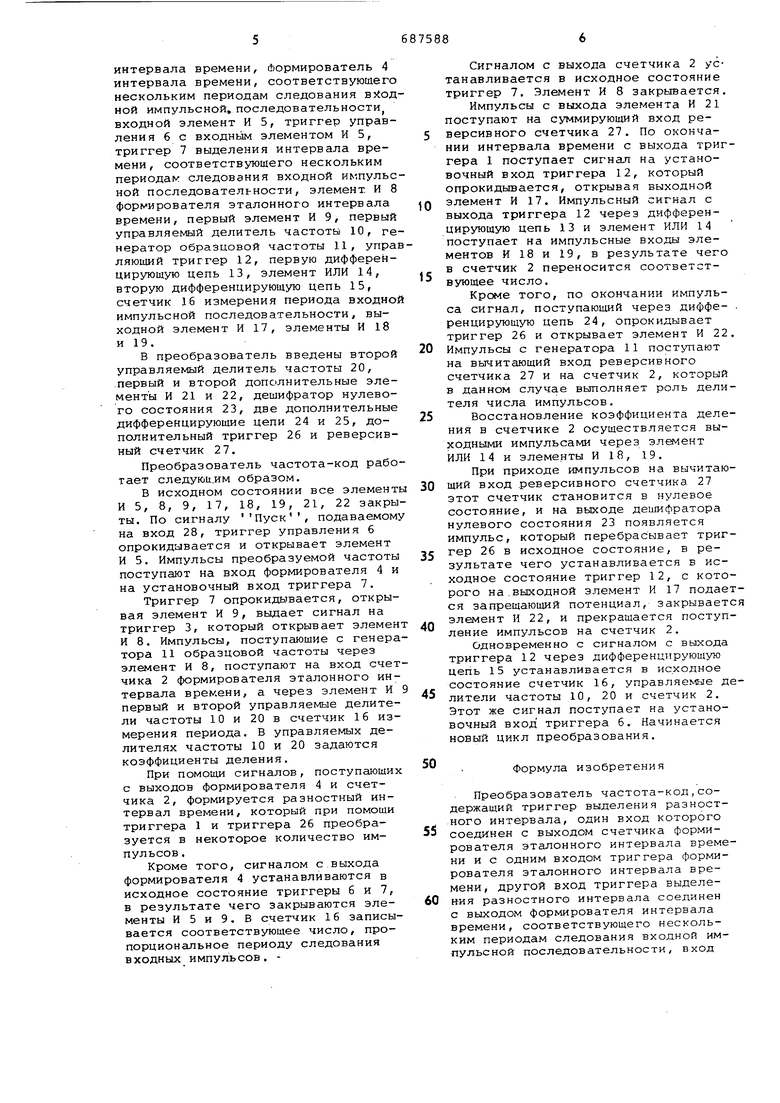

На чертеже приведена структурная электрическая схема преобразователя.

Преобразователь частота-код содержит триггер 1 выделения разностного интервала, счетчик 2 формирователя эталонного интервала времени, триггер 3 формирователя эталонного

интервала времени, Формирователь 4 интервала времени, соответствующего нескольким периодам следования входной импульсной, последовательности входной элемент И 5, триггер управления 6 с входным элементом И 5, триггер 7 выделения интервала времени, соответствующего нескольким периодам следования входной импульсной последовательности, элемент. И 8 формирователя эталонного интервала времени, первый элемент И 9, первый управляемый делитель частоты 10, генератор образцовой частоты 11, управляющий триггер 12, первую дифференцирующую цепь 13, элемент ИЛИ 14, вторую дифференцирующую цепь 15, счетчик 16 измерения периода входной импульсной последовательности, выходной элемент И 17, элементы И 18 и 19.

В преобразователь введены второй управляемый делитель частоты 20, первый и второй дополнительные элементы И 21 и 22, дешифратор нулевого состояния 23, две дополнительные дифференцирующие цепи 24 и 25, дополнительный триггер 26 и реверсивный счетчик 27.

Преобразователь частота-код работает следуюи.им образом.

В исходном состоянии все элементы И 5, 8, 9, 17, 18, 19, 21, 22 закрыПуск

ты. По сигналу

подаваемому

на вход 28, триггер управления б опрокидывается и открывает элемент И 5. Импульсы преобразуемой частоты поступают на вход формирователя 4 и на установочный вход триггера 7.

Триггер 7 опрокидывается, открывая элемент И 9, выдает сигнал на триггер 3, который открывает элемен И 8. Импульсы, поступающие с генератора 11 образцовой частоты через элемент И 8, поступают на вход счетчика 2 формирователя эталонного интервала времени, а через элемент И первый и второй управляемые делители частоты 10 и 20 в счетчик 16 измерения периода. В управляемых делителях частоты 10 и 20 задаются коэффициенты деления.

При помощи сигналов, поступающих с выходов формирователя 4 и счетчика 2, формируется разностный интервал времени, который при помощи триггера 1 и триггера 26 преобразуется в некоторое количество импульсов .

Кроме того, сигналом с выхода формирователя 4 устанавливаются в исходное состояние триггеры 6 и 7, в результате чего закрываются элементы И 5 и 9. В счетчик 16 записывается соответствующее число, пропорциональное периоду следования входных импульсов. Сигналом с выхода счетчика 2 устанавливается в исходное состояние триггер 7. Элемент И 8 закрывается.

Импульсы с вьгхода элемента И 21 поступают на суммирующий вход реверсивного счетчика 27. По окончании интервала времени с выхода триггера 1 поступает сигна.п на установочный вход триггера 12, который опрокидывается, открывая выходной элемент И 17. Импульсный сигнал с

0 выхода триггера 12 через дифференцирующую цепь 13 и элемент ИЛИ 14 поступает на импульсные входы элементов И 18 и 19, в результате чего в счетчик 2 переносится соответст5вующее число.

Кроме того, по окончании импульса сигнал, поступающий через диффе- . ренцирующую цепь 24, опрокидывает триггер 26 и открывает элемент И 22.

0 Импульсы с генератора 11 поступают на вычитающий вход реверсивного счетчика 27 и на счетчик 2, который в данном случае выполняет роль делителя числа импульсов.

5

Восстановление коэффициента деления в счетчике 2 осуществляется выходными импульсами через элемент ИЛИ 14 и элементы И 18, 19.

При приходе импульсов на вычитающий вход реверсивного счетчика 27

0 этот счетчик становится в нулевое состояние, и на выходе дешифратора нулевого состояния 23 появляется импульс, который перебрасывает триггер 26 в исходное состояние, в ре5зультате чего устанавливается в исходное состояние триггер 12, с которого на.выходной элемент И 17 подается запрещающий потенциал, закрывается элемент И 22, и прекращается поступ0ление импульсов на счетчик 2.

Одновременно с сигналом с выхода триггера 12 через дифференцирующую цепь 15 устанавливается в исходное состояние счетчик 16, управляемые де5лители частоты ДО, 20 и счетчик 2. Этот же сигнал поступает на установочный вход триггера 6. Начинается новый цикл преобразования.

0

Формула изобретения

Преобразователь частота-код,содержащий триггер выделения разност.ного интервала, один вход которого

5 соединен с выходом счетчика формирователя эталонного интервала времени и с одним входом триггера формирователя эталонного интервала времени, другой вход триггера выделе0ния разностного интервала соединен с выходом формирователя интервала времени, соответствующего нескольким периодам следования входной импульсной последовательности, вход

которого через входной элемент И соединен с выходом триггера управления входным элементом И, а выход - с входом триггера управления входньом элементом И и входом триггера выделения интервала времени, соответствующего нескольким периодам следования входной импульсной последовательности, другой вход которого соединен с входом формирователя интервала времени, соответствующего нескольким периодам следования входной импульсной последовательности, а выход - с входом триггера формирователя эталонного интервала времени, выход которого через элемент И формирователя эталонного интервала времени подключен к счетчику формирователя эталонного интервала времени , другой выход триггера выделения интервала времени, соответствующего нескольким периодам следования входной импульсной последовательности, через первый элемент И подключен к входу первого управляемого делителя частоты, причем другой вход первого элемента И и элемента И формирователя эталонного интервала времени подключен к выходу генератора образцовой частоты, а выход триггера выделения разностного интервала времени подключен к входу управляющего триггера, выход которого через первую дифференцирующую цепь подключен к входу элемента ИЛИ, а другой выход через вторую дифференцирующую цепь соединен с установочными входами счетчика формирователя эталонного интервала времени, первого управляемого делителя частоты, счетчика измерения периода входной импульсной последовательности и триггера управления входным элементом И и непосредственно - с управляющим входом выходного элемента И, импульсный вход которого подключен к счетчику формирователя эталонного интервала времени, а выход к второму входу элемента ИЛИ, выходы которого через вторые элементы И соединены с установочными входами счетчика формироВателя эталонного интервала времени, причем вторые входы вторых элементов И соединены с потенцигшьными выходами счетчика измерения периода следования входной импульсной последоваотличающийся

тельности.

тем, что, с целью повышения быстродействия, в него введены второй управляющий делитель частоты, первый и

л второй дополнительные элементы И, дешифратор нулевого состояния, две дополнительные дифференцирующие цепи, дополнительный триггер и реверсивный счетчик, входы которого через первый и второй дополнительные элементы И соединены с генератором образцовой частоты, а нулевые выходы - через дешифратор нулевого состояния с одним из входов дополнительного триггера, другой вход которого через первую дополнительную дифференцирующую цепь соединен с выходом триггера выделения разнсстiHoro интервала и вторым входом i epвого дополнительного элемента И,

5 ;а выход дополнительного триггера ;через вторую дополнительную диффе ренцирующую цепь соединен со вторым |входом управляющего триггера и входом второго дополнительного

0 ;элемента И, выход которого соединен .с входом счетчика формирователя эталонного интервала времени, вход вто;рого управляемого делителя частоты . соединен с выходом первого упргшляе5 мого делителя частоты, установочный вход - с входом триггера управления входным элементом И, а выход - с вхо,дом счетчика измерения периода сле.дования импульсов входной импульсной

0 последовательности.

Источники информации, принятые во внимание при экспертизе

1.Шляндин В,М. Цифровые измерительные преобразователи и приборы.

- M.f Высшая школа , 1973, с. 159, рис. 312.

2.Авторское сйидительство СССР № 428548, кл. Н 03 К 13/20, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТА-КОД | 1972 |

|

SU428548A1 |

| Цифровой частотомер | 2019 |

|

RU2730047C1 |

| Образцовый преобразователь мощности в частоту | 1988 |

|

SU1564558A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТА — КОД | 1973 |

|

SU372684A1 |

| УСТРОЙСТВО ТЕРМОКОМПЕНСАЦИИ КВАРЦЕВОГО ГЕНЕРАТОРА | 1990 |

|

RU2007839C1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ЧАСТОТЫ НИЗКОЧАСТОТНЫХ СИГНАЛОВ | 1992 |

|

RU2101714C1 |

| Устройство для цифрового измерения частоты | 1989 |

|

SU1666965A2 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДЕВИАЦИИ ЧАСТОТЫ | 1998 |

|

RU2138828C1 |

| Устройство для цифрового измерения частоты медленно меняющихся процессов | 1987 |

|

SU1413542A1 |

| ИНФРАКРАСНЫЙ РАДИОМЕТР | 1999 |

|

RU2172476C1 |

Авторы

Даты

1979-09-25—Публикация

1976-12-24—Подача