(54) РЕГУЛЯТОР ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой широтно-импульсный модулятор | 1978 |

|

SU752778A1 |

| Цифровой регулятор температуры | 1986 |

|

SU1352470A1 |

| Устройство для извлечения корня | 1980 |

|

SU875380A1 |

| Устройство для регулирования температуры | 1985 |

|

SU1335950A1 |

| СПОСОБ РЕГУЛИРОВАНИЯ ЖИДКОСТНОГО РАКЕТНОГО ДВИГАТЕЛЯ И УСТРОЙСТВА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1993 |

|

RU2085755C1 |

| Устройство для регулирования температуры | 1983 |

|

SU1151932A1 |

| Многоканальный широтно-импульсный регулятор температуры (его варианты) | 1981 |

|

SU962883A1 |

| Устройство для регулирования давления | 1988 |

|

SU1674075A1 |

| РАДИОИЗОТОПНЫЙ ТОЛЩИНОМЕР | 1992 |

|

RU2116620C1 |

| Многоканальный регулятор тепловых процессов (его варианты) | 1980 |

|

SU943667A1 |

1

Изобретение относится к области автоматического регулирования и может быть применено в системах регулирования с частотно-импульсной формой входного сигнала.

Известны регуляторы частоты вращения газотурбинных двигателей 1, 2, построенные на базе струйных элементов и содержащие датчик и задатчик частоты, вычитатель частот и реверсивное исполнительное устройство.

Ближайшим по технической сущности к изобретению является регулятор частоты 3, содержащий датчик и задатчик частоты, подключенные к входам вычитателя частот, первый выход которого соединен с управляющим входном исполнительного блока, выход которого соединен с входом датчика частоты.

Недостатком таких регуляторов является снижение их быстродействия при уменьщении отклонения входных частот от заданных значений.

Это связано с тем, что при изменении отклонения частоты на входе регулятора изменяется разностная частота управляющего воздействия. Диапазон изменения разностной частоты управляющего воздействия

простирается от частоты задатчика при начальных больщих отклонениях входных сигналов до «нулевых частот при малых отклонениях установивщегося состояния. Наиболее сложными для отработки являются крайние участки частотного диапазона. Так при отработке «нулевых или близких к ним частот диапазона снижается быстродействие регулятора, зависимое от частоты управляющего воздействия. При отработке высоких частот имеют место пропуски импульсов в отработке интегрирующего привода исполнительного устройства.

Целью изобретения является расширение диапазона регулирования регулятора.

Эта цель достигается тем, что предложенный регулятор содержит умножитель часто5ты и ограничитель частот, выход которого соединен с первым входом умножителя частоты, второй вход которого подключен к второму выходу вь1читателя частот, первый выход - к входу исполнительного блока, а вторые выходы - к входам ограничителя частот. Кроме того, умножитель частоты, содержит блок управления, элемент И, счетчик, блок памяти, первый и второй делители частоты и генератор опорной частоты, выход которого подключен к входу первого де лйтеля частоты и входу второго делителя , выход которого подключен к входу счетчика, первый выход которого подключен к входу блока памяти, а вторые выходы - к Соответствующим вторым выходам умножиТеля частоты, выход которого соединен с выхОДОТй первого делителя частоты, управляющий вход которого соединен с выходом блока памяти. Управляющий вход блока памяти соединен с выходом элемента И, первый вход KOtoporo соединен с первым входом умножителя частоты, а второй вход - с первым выходом блока управления, второй выход которого подключен к управляющему входу счетчика и соответствующему второму вЫхоДу умножителя частоты, а вход - к второму входу умножителя частоты.

Эта цель достигается также тем, что Ограничитель частот содержит первый эле-, мент И и последовательно соединенные второй э.пемент.. И, элемент ИЛИ и триггер, выход которого подключен к выходу ограничителя, частот, а второй вход - невыходу первого элемента И. Входы элементов И и второй вход элемента ИЛИ соедйНены с со(5№ёТс твую ЦИМи входами ограничителя частот.

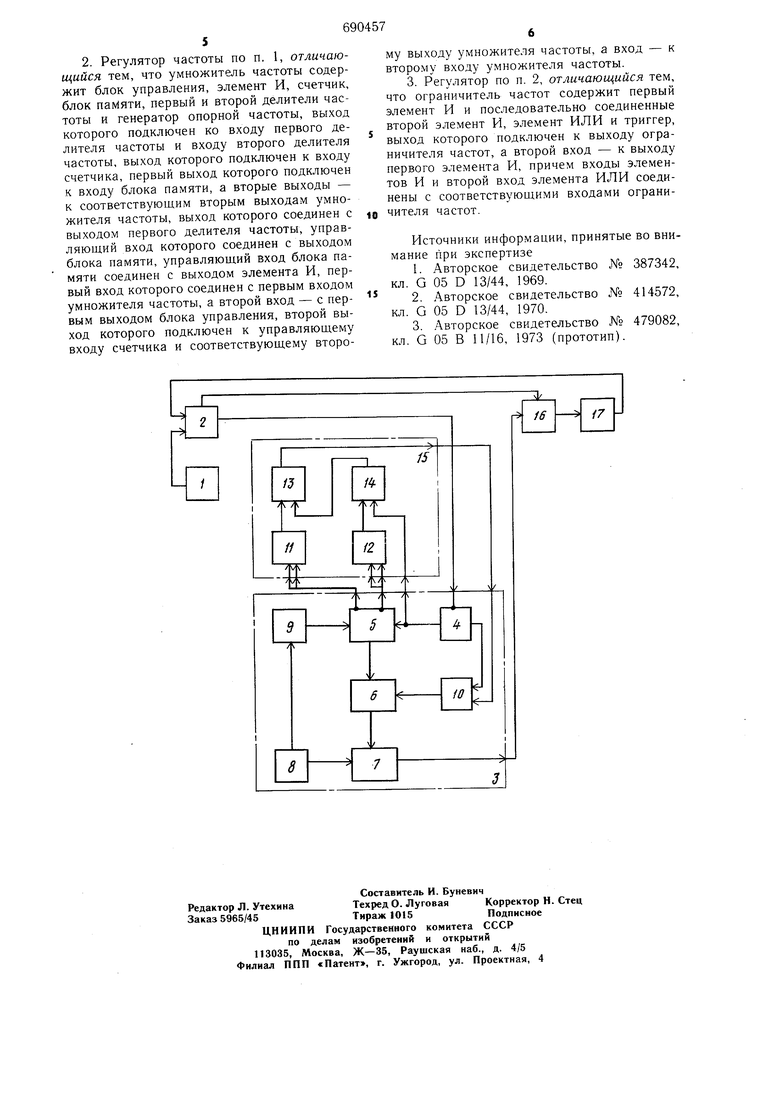

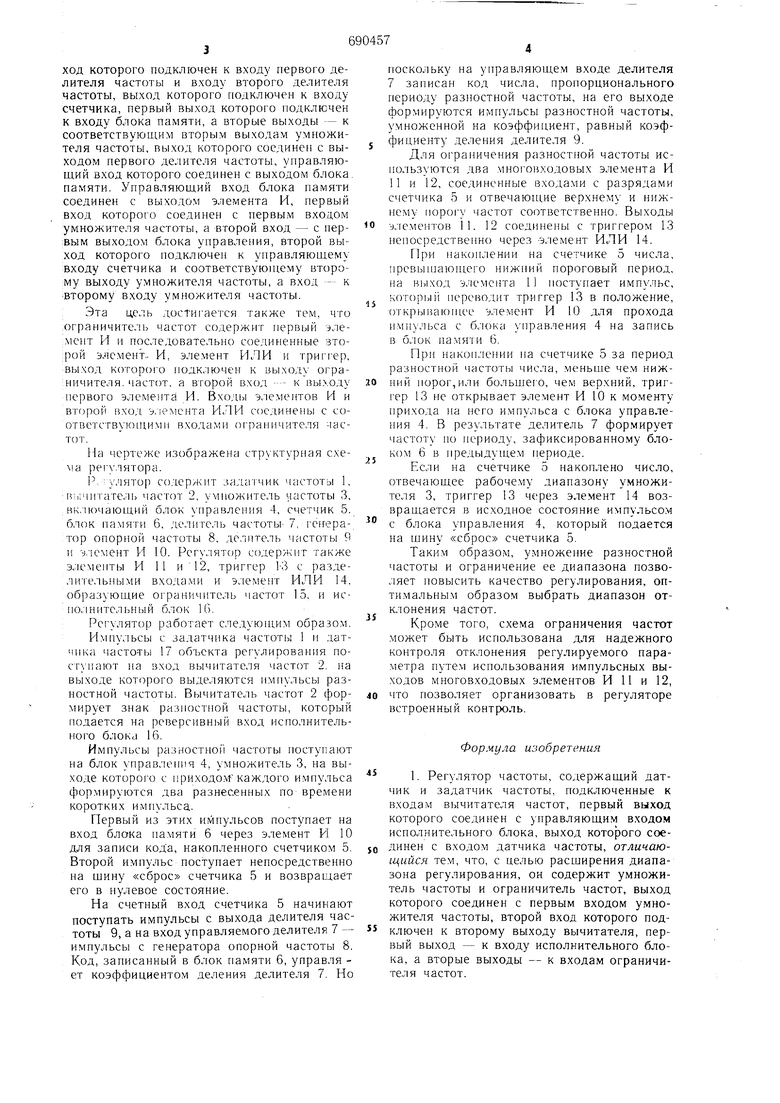

На чертеже изображена структурная схема регулятора.

Регулятор содержит задатчик частоты 1, вычитатель частот 2, умножитель частоты 3, включающий блок управления 4 счетчик 5. блок памяти 6, делитель частоты-7,гёкёратор опорной частоты 8, дёлятель частоты 9 и элемент И 10. Регулятор содержит также элементы И 11 и12, TpHrfep 1-3 с разделительными входами и элемент ИЛИ 14, образующие ограничитель частот 15, и исполнительный блок 16.

Регулятор работает следующим образом.

Импульсы с задатчика частоты 1 и датчика частоты 17 объекта регулирования поступают на вход вычитателя частот 2, .на 1Й бДё коТорого выделяются импульсы разностной частоты. Вычитатель частот 2 формирует знак разностной частоты, который подается на реверсивный вход исполнительного блока 16.

Импульсы разностной частоты поступают на блок управления 4, умножитель 3, на выходе которого с приходо|уг;;каждого импульса формируются два разнесенных по времени коротких импульса. Первый из этих импульсов поступает на вход блока памяти 6 через элемент И 10 для записи коДа, накопленного счетчиком 5. Второй импульс поступает непосредственно на щину «сброс счетчика 5 и возвращает его в нулевое состояние.

На счетный вход счетчика 5 начинают поступать импульсы с выхода делителя частоты 9, а на вход управляемого делителя 7 - импульсы с генератора опорной частоты 8. Код, записанный в блок памяти 6, управля ет коэффициентом деления делителя 7. Но

поскольку на управляющем входе делителя 7 записан код числа, пропорционального периоду разностной частоты, на его выходе формируются импульсы разностной частоты, умноженной на коэффициент, равный коэффициенту деления делителя 9.

Для ограничения разностной частоты используются два многовходовых элемента И 11 и 12, соединенные входами с разрядами счетчика 5 иЬтвёчаЮщие верхнему и нижнему порогу частот соответственно. Выходы

элементов 11, 12 соединены с триггером 13 непосредственно через -элемент ИЛИ 14.

При накоплении на счетчике 5 числа, превышающего нижний пороговый период, на выход элемента 11 поступает импульс, который переводит триггер 13 в положение, открывающее элемент И 10 для прохода импульса с блока управления 4 на запись в блок памяти 6.

При накоплении на счетчике 5 за период разностной частоты числа, меньще чем ниж0 НИИ порог,или больщего, чем верхний, триггер 13 не открывает элемент И 10 к моменту прихода на него импульса с блока управления 4. В результате делитель 7 формирует частоту по периоду, зафиксированному блоком 6 в предыдущем периоде.

Если на счетчике 5 накоплено число, отвечающее рабочему диапазону умножителя 3, триггер 13 через элемент 14 возвращается в исходное состояние импульсом

с блока управления 4, который подается на щину «сброс счетчика 5.

Таким образом, умножение разностной частоты и ограничение ее диапазона позволяет повысить качество регулирования, оптимальным образом выбрать диапазон отклонения частот.

Кроме того, схема ограничения частот может быть использована для надежного контроля отклонения регулируемого параметра путем использования импульсных выходов многовходовых элементов И 11 и 12,

0 что позволяет организовать в регуляторе встроенный контроль.

Формула изобретения

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1979-10-05—Публикация

1977-06-06—Подача