Изобретение относится к технике связи и может использоваться в аппаратуре передачи данных.

Известно устройство .защиты от ошибок телеграфной аппаратуры с решающей обратной связью, содержащее на входе последовательно соединенные динамический запоминающий блок и блок управления, один выход которого подключен к входу динамического запоминающего блока, а другой выходк входу кодера, датчик импульсов, счетчик импульсов с исполнительным блоком, а также последовательно соединенные декодер и дешифратор команд I.

Однако такое устройство имеет большое время вхождения в связь.

Цель изобретения - сокращение времени вхождения в связь.

Для этого в устройство защиты от ошибок телеграфной аппаратуры с решающей обратной связью, содержащее на входе последовательно соединенные динамический запоминающий блок и блок управления, один выход которого подключен к входу динамического запоминающего блока, а другой выход-к входу кодера. Датчик импульсов.

счетчик импульсов с исполнительным блоком а также последовательно соёДитенньге декодер и дешифратор команд, введены блок запрета, элемент-задержки и дешифратор «подтверждения, к его входу подключен

один из выходов декодера, другой выход которого через элемент задержки подключен к запускающему входу датчика импульсов, выход этого датчика подклйчё Нк блокирующему входу динамического запоминающего

блока непосредственно и через блок запрета к другому входу блока управления, третий выход которого подключен к запускающему входу счетчика импульсов с исполнительным блоком, а к третьему входу блока управления, объединенному с запрещающим входом

5 блока запрета, подключен выход дещифратора команд, при этом выход дещифратора «подтверждения подключен к сбрасывающим входам датчика команд и счетчика импульсов с исполнительным блоком, причем

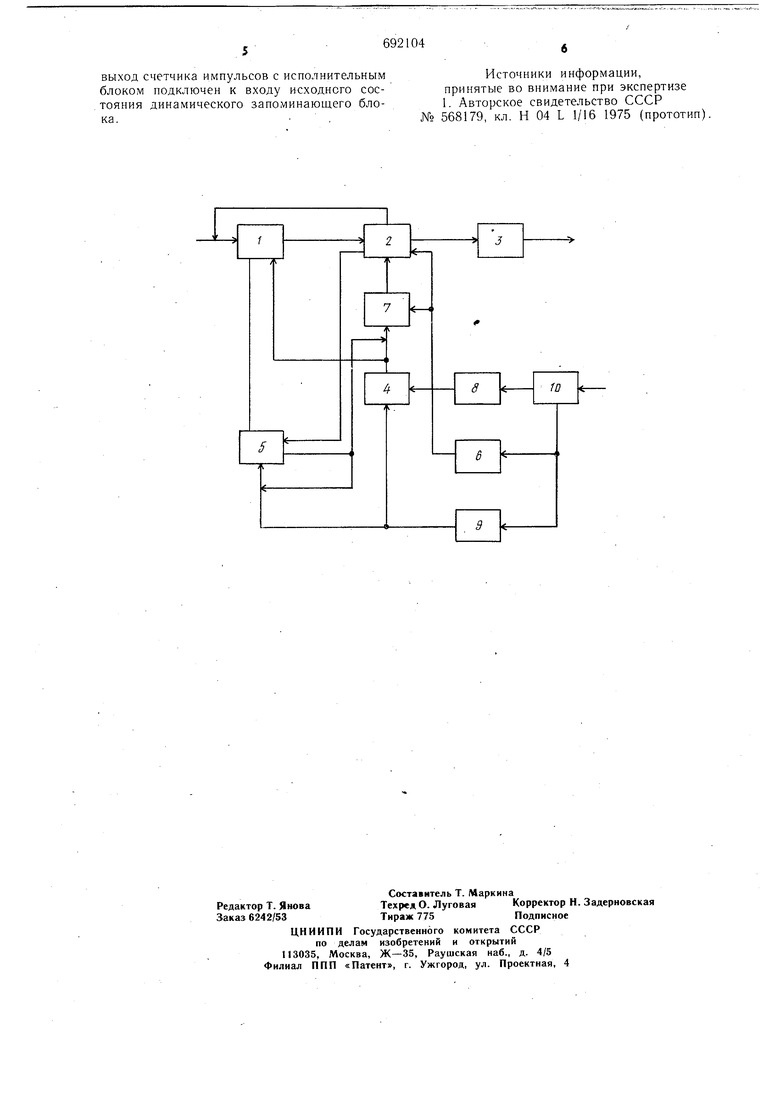

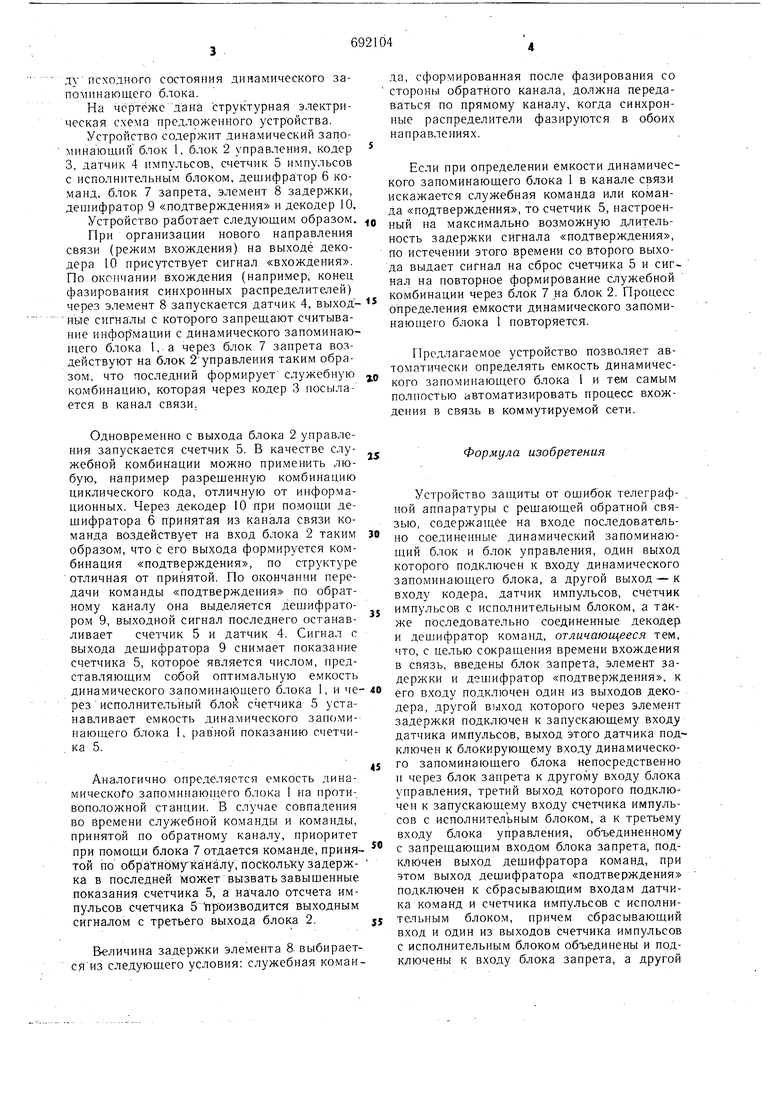

(J сбрасывающий вход и один из выходов счетчика импульсов с исполнительным блоком объединены и подключены к входу блока запрета, а другой выход счетчика импульсов с исполнительным блоком подключен к входу исходного состояния динамического запоминающего блока. На чертеже дана структурная электрическая схема иредложенного устройства. Устройство содержит динамический заиоминающии блок 1, блок 2 управления, кодер 3, датчик 4 импульсов, счетчик 5 импульсов с исполнительным блоком, дешифратор 6 команд, блок 7 запрета, элемент 8 задержки, дешифратор 9 «подтверждения и декодер 10. Устройство работает следуюш,им образом. При организации нового направления связи (режим вхождения) на выходе декодера 10 присутствует сигнал «вхождения. По окончании вхождения (например, конец фазирования синхронных распределителей) через элемент 8 запускается датчик 4, выходные сигналы с которого запрещают считывание информации с динамического запоминающего блока 1, а через блок 7 запрета воздействуют на блок 2управления таким образом, что последний формирует служебную комбинацию, которая через кодер 3 посылается в канал связи. Одновременно с выхода блока 2 управления запускается счетчик 5. В качестве служебной комбинации можно применить любую, например разрешенную комбинацию циклического кода, отличную от информационных. Через декодер 10 при помощи дещифратора 6 принятая из канала связи команда воздействует на вход блока 2 таким образом, что с его выхода формируется комбинация «подтверждения, по структуре отличная от принятой. По окончании передачи команды «подтверждения по обратно.му каналу она выделяется дешифратором 9, выходной сигнал последнего останавливает счетчик 5 и датчик 4. Сигнал с выхода дешифратора 9 снимает показание счетчика 5, которое является числом, представляющим собой оптимальную емкость динамического запоминающего блока 1, и че рез исполнительный блок счетчика 5 устанавливает емкость динамического запоминающего блока 1, равной показанию счетчика 5. Аналогично определяется емкость динамического запо.минающего блока 1 на противоположной станции. В случае совпадения во времени служебной команды и команды, принятой по обратному каналу, приоритет при помощи блока 7 отдается команде, принятой по обратН(, поскольку задержка в последней может вызвать завышенные показания счетчика 5, а начало отсчета импульсов счетчика 5 прЪ зволится выходным сигналом с третьего выхода блока 2. Величина задержки элемента 8. выбираетсяиз следующего условия: служебная команда, сформированная после фазирования со стороны обратного канала, должна передаваться по прямому каналу, когда синхронные распределители фазируются в обоих направлениях. Если при определении емкости динамического запоминающего блока 1 в канале связи искажается служебная команда или команда «подтверждения, то счетчик 5, настроенный на максимально возможную длительность задержки сигнала «подтверждения, по истечении этого времени со второго выхода выдает сигнал на сброс счетчика 5 и сигнал на повторное формирование служебной комбинации через блок 7 на блок 2. Процесс определения емкости динамического запоминающего блока 1 повторяется. Предлагаемое устройство позволяет автоматически определять емкость динамического запоминающего блока 1 и тем самым полиостью автоматизировать процесс вхождения в связь в коммутируемой сети. Формула изобретения Устройство от ошибок телеграфной аппаратуры с решающей обратной связью, содержапхее на входе последовательно соединенные динамический запомкнающий блок и блок управления, один выход которого подключен к входу динамического запоминающего блока, а другой выход - к входу кодера, датчик импульсов, счетчик импульсов с исполнительным блоком, а также последовательно соединенные декодер и дешифратор команд, отличающееся тем, что, с целью сокращения времени вхождения в связь, введены блок запрета, элемент задержки и дешифратор «подтверждения, к его входу подключен один из выходов декодера, другой выход которого через элемент задержки подключен к запускающему входу датчика импульсов, выход этого датчика подключен к блокирующему входу динамического запоминающего блока непосредственно и через блок запрета к другому входу блока управления, третий выход которого подключен к запускающему входу счетчика импульсов с исполнительным блоком, а к третьему входу блока управления, объединенному с запрещающим входом блока запрета, подключен выход дешифратора команд, при этом выход дещифратора «подтверждения подключен к сбрасывающим входам датчика комавд и счетчика импульсов с исполнительным блоком, причем сбрасывающий вход и один из выходов счетчика импульсов с исполнительным блоком объединены и подключены к входу блока запрета, а другой

выход счетчика импульсов с исполнительным блоком подключен к входу исходного состояния динамического запоминающего блока..

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 568179, кл. Н 04 L 1/16 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство защиты от ошибок телеграфной аппаратуры с решающей обратной связью | 1987 |

|

SU1561212A2 |

| Система передачи дискретной информации | 1982 |

|

SU1061277A1 |

| Устройство защиты от ошибок аппаратуры с решающей обратной связью | 1975 |

|

SU568179A1 |

| Стартстопно-синхронный передатчик | 1979 |

|

SU832762A1 |

| Устройство для выделения команд в телеграфной стартстопно-синхронной системе | 1991 |

|

SU1764178A2 |

| Устройство для автоматического переключения телеграфных каналов связи | 1983 |

|

SU1149426A2 |

| Система телемеханики | 1984 |

|

SU1257686A1 |

| Устройство для дистанционного управления двухпозиционными объектами | 1983 |

|

SU1149299A1 |

| Устройство для обнаружения поврежденного участка телеграфного тракта | 1981 |

|

SU1042194A2 |

| Контролируемый пункт системы телемеханики | 1988 |

|

SU1524080A1 |

Авторы

Даты

1979-10-15—Публикация

1978-05-03—Подача