(54) СПОСОБ ФОРСИРОВАННОГО ЗАПИРАНИЯ ТРАНЗИСТОРОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Ключевой преобразователь напряжения | 1986 |

|

SU1403309A1 |

| Ключ постоянного тока | 1988 |

|

SU1624680A1 |

| Двухтактный транзисторный преобразователь постоянного напряжения | 1982 |

|

SU1032569A1 |

| Преобразователь постоянного напряжения | 1990 |

|

SU1778889A1 |

| Коммутирующее устройство | 1987 |

|

SU1480115A1 |

| Выходной блок генератора строчной развертки | 1986 |

|

SU1363532A1 |

| Преобразователь напряжения | 1989 |

|

SU1742955A1 |

| ДВУХТАКТНЫЙ ИНВЕРТОР | 1992 |

|

RU2009609C1 |

| Выходной усилитель генератора строчной развертки | 1988 |

|

SU1626446A1 |

| Полумостовой регулируемый инвертор | 1987 |

|

SU1510058A1 |

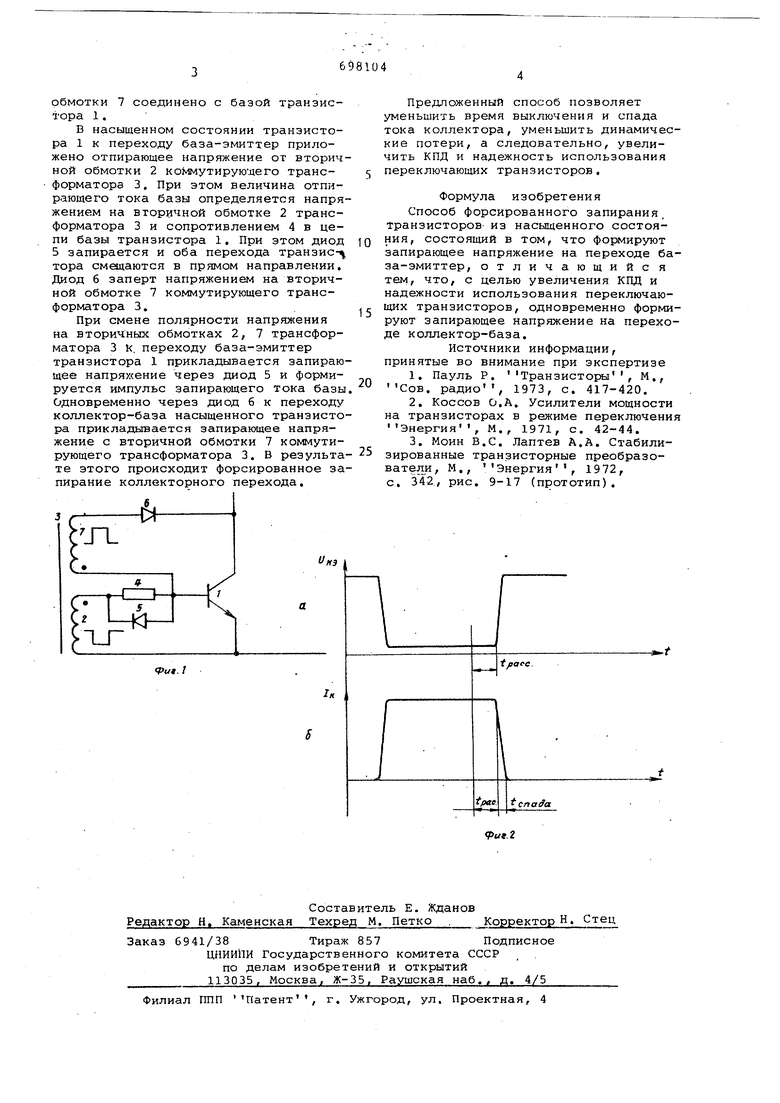

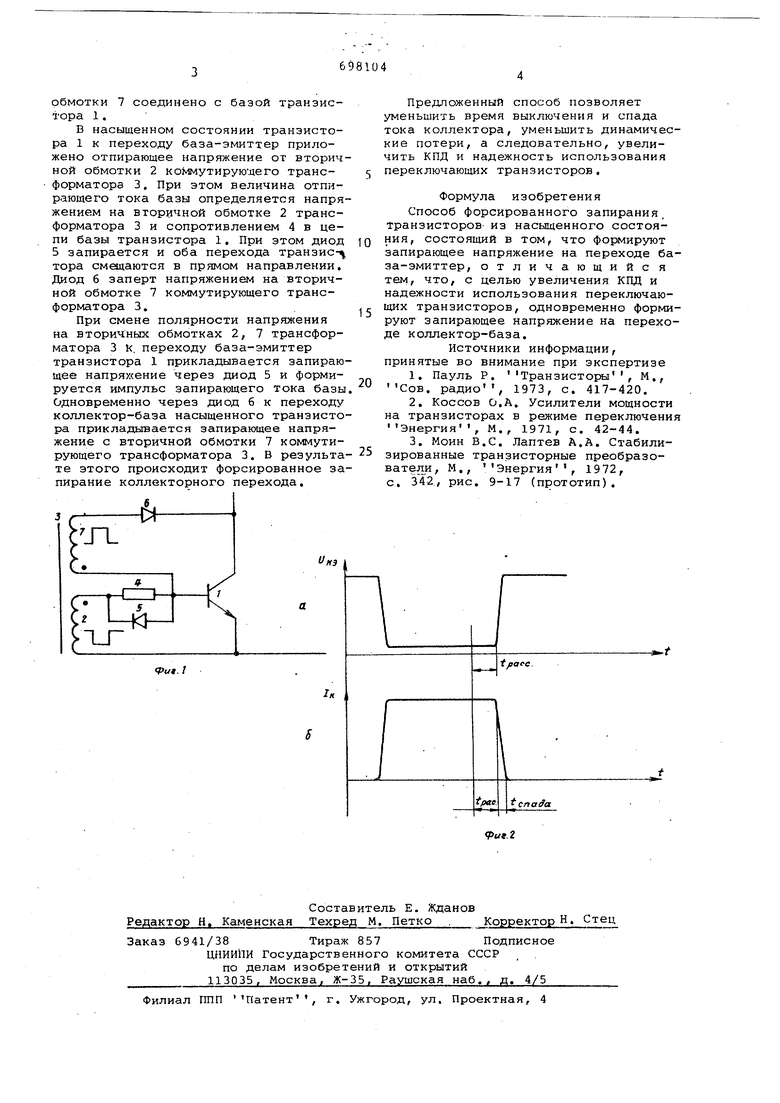

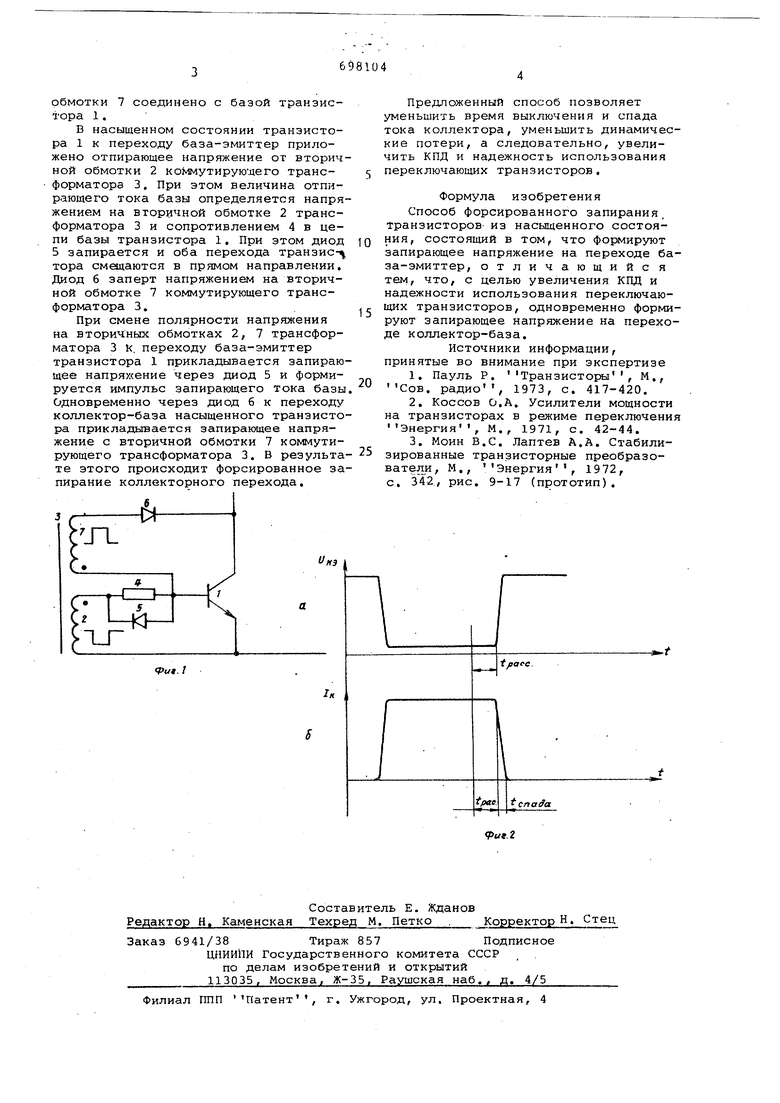

Изобретение относится к области преобразовательной техники и может быть использовано при разработке ис точников питания переключательного типа. Известны способы форсированного запирания транзисторов Ц 2, состоящие в тетл, что подают запирающее напряжение на переход база-эмиттер насыщенного транзистора. Однако эти способы имеют ряд недостатков: значительные времена вык.пючения и спада коллекторного тока большие динамические потери; возможность инверсного режима .транзисто ра при запирании. Наиболее близким техническим решением к данному изобретению по технической сущности и достигаеметлу результату является способ форсированного запирания транзисторов 3 из насыщенного состояния, состоящий в том, что формируют запирающее напряжение на переходе база-эмиттер. Одна ко при кс лмутации транзисторов на частотах/ соизмеримых по длительности импульсов с временами выключения такой способ не обеспечивает достаточно высокий КПД и надежность. Целью изобретения является повышение КПД и надежности использования переключающих транзисторов. Поставленная цель достигается тем, что в способе форсированного запирания транзисторов из насиненного состояния, состоящем в том, что формируют запирающее напряжение на переходе база-эмиттер, одновременно формируют запирающее напряжение на переходе коллектор-база. На фиг. 1 приведена блок-схема устройства, реализующего предлагаемый способ форсированного запирания транзисторов из насыщенного состояния; на фиг. 2 - диаграмма токов и напряжений в различных точках схемы. Устройство (фиг.. 1) содержит транзистор 1, вторичную обмотку 2 коммутирующего трансформатора 3, конец которой соединен с эмиттером транзистора 1 , параллельно соединенные резистор 4 и диод 5, соединенный катодом с началом вторичной обмотки 2, а анодом - с базой транзистора 1, диод 6, соединенный катодом с коллектором транзистора 1, а анодом - с концом вторичной обмотки 7 коммутирующего трансформатора 3. Начало вторичной обмотки 7 соединено с базой транзистора 1. В насыщенном состоянии транзистора 1 к переходу база-эмиттер приложено отпирающее напряжение от вторич ной обмотки 2 коммутирующего трансформатора 3. При этом величина отпирающего тока базы определяется напря жением на вторишой обмотке 2 трансформатора 3 и сопротивлением 4 в цепи базы транзистора 1. При этом диод 5 запирается и оба перехода транзистора смещаются в прямом направлении. Диод 6 заперт напряжением на вторичной обмотке 7 коммутирующего трансформатора 3. При смене полярности напряжения на вторичных обмотках 2, 7 трансформатора 3 к. переходу база-эмиттер транзистора 1 прикладывается запираю щее напряжение через диод 5 и формируется импульс запирающего тока базы Одновременно через диод б к переходу коллектор-база насыщенного транзисто ра прикладывается запирающее напряжение с вторичной обмотки 7 коммутирующего трансформатора 3. В результа те этого происходит форсированное за пирание коллекторного перехода. Предложенный способ позволяет уменьшить время выключения и спада тока коллектора, уменьшить динамические потери, а следовательно, увеличить КПД и надежность использования переключающих транзисторов. Формула изобретения Способ форсированного запирания, транзисторов из насыщенного состояния, состоящий в том, что фор 1ируют запирающее напряжение на переходе база-эмиттер, отличающийс я тем, что, с целью увеличения КПД и надежности использования переключающих транзисторов, одновременно формируют запирающее напряжение на переходе коллектор-база. Источники информации, принятые во внимание при экспертизе 1.Пауль Р. Транзисторы, М., Сов. радио , 1973, с. 417-420. 2.Коссов О,А. Усилители мощности на транзисторах в режиме переключения Энергия, М., 1971, с. 42-44. 3.Моин B.C. Лаптев А.А. Стабилизированные транзисторные преобразователи, М., Энергия, 1972, с. , рис. 9-17 (прототип).

-км

tpae.

t епаЗа

Авторы

Даты

1979-11-15—Публикация

1978-02-20—Подача