Изобретение относится к области автоматической измерительной техники в частности к устройствам анализа ам плитуды импульсных сигналов случайны импульсных последовательностей. Известны амплитудные анализаторы содержащие пороговые каскады с пере страизаемыми пороговыми уровнями. Каждый канал содержит пересчетную схему, которая фиксирует число импульсоа, амплитуда которых превышает некоторый заданный уровень 1. Однако эти устройства имеют недосГцточную достоверность анализа. Известно устройство для анализа амплитуды импульсных сигналов, содержащее пороговые каскады, логические элементы запрет и пересчетные устройства 2. Однако это устройство не позволя работать с импульсами, имеющими пологие передние фронты различной кру тизны. Это обусловлено тем, что при поступлении на вход устройства сигнального импульса с пологим фронтом прсмежутки времени между моментами срабатывания пороговых устройств со седних каналов, зависящие от крутиз ны фронта, могут быть достаточно большими. Поэтс5му импульсы с выходов пороговых каскадов соседних каналов поступают на соответствующие элементы антисовпадения не одновременно, а со сдвигом, соответствующим указанным промежуткам времени. Элементы антисовпадения от 1-ого до (к-1)-ого включительно (где к - нсяиер канала/ соответствующего амплитуде сигнального импульса) срабатывают .два раза и на их выходах появляется по два импульса. Лишний импульс на выходах элементов антисовпадения 4, 2,..(к-1) каналов привсдит к ложному срабатьшанию пересчетных устройств этих каналов, что недопустимо, так как снижается достоверность информации, фиксируемой пересчетными элементами. Цель изобретения - п-овышение достоверности анализа. Для этого в устройство, ссдержащее пороговые каскады по числу каналов т, входы которых подключены к входной клемме устройства, (т-1) логических элементов запрет и п пересчетных устройств, причем выходы логических элементов запрет 1,2,., ,, (т-1) каналов соединены с входами соответствующих пересчетных устройств, а выход порогового каскада т-ого канала соединен с входом соответствующего пересчетного устройства непосредственно, вы-ходы пересчетньах устройств подключены к выходным клеммам устройства, введены m одновибраторов, (т-1) формирователей заднего фронта и (т-2) логических элементов ИЛИ. Выход порогового каскада щ-ого канала соединен дополнительно через соответствующий одновибратор с з.апрещающим входом логического элемента запрет {т-1)-ого канала и через все логические элементы ИЛИ с запрещающими, входами всех остальных логических элементов запрёт. Выход порогового каскада первого канала соединен через соединенные последовательно соответствующий одновибратор и формироватегль заднего фронта с сигнальным вxoдcxvl соответствующего логического элемента запрет, выходы пороговых каскадов 2 ,,.., (т-1)-ого каналов соединены через соединенные последовательно соответствующие одновибраторы и логические элементы ИЛИ с запрещающими входами логических элементов запрет всех каналов с более низкими номерами, при этом выходы однов ибраторов 2, ... , (m-l) -ого кана- лов соединены дополнительно через формирователи заднего фронта с сигнальными входами соответствующих логических элементов запрет.

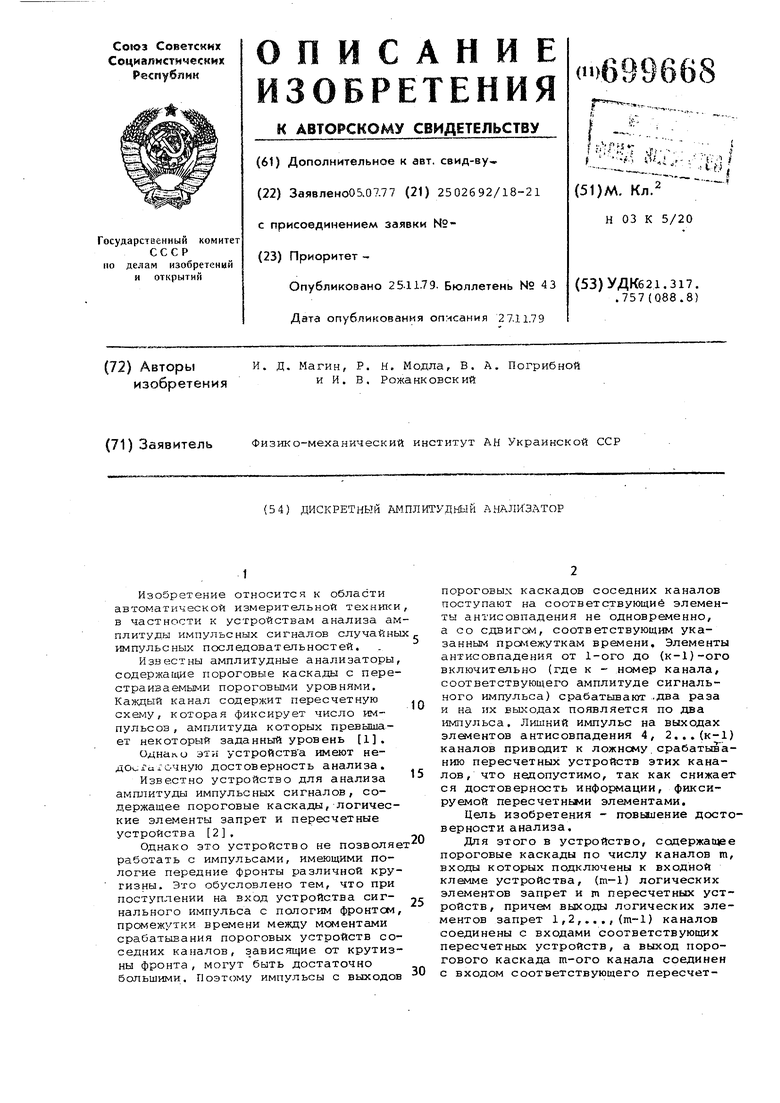

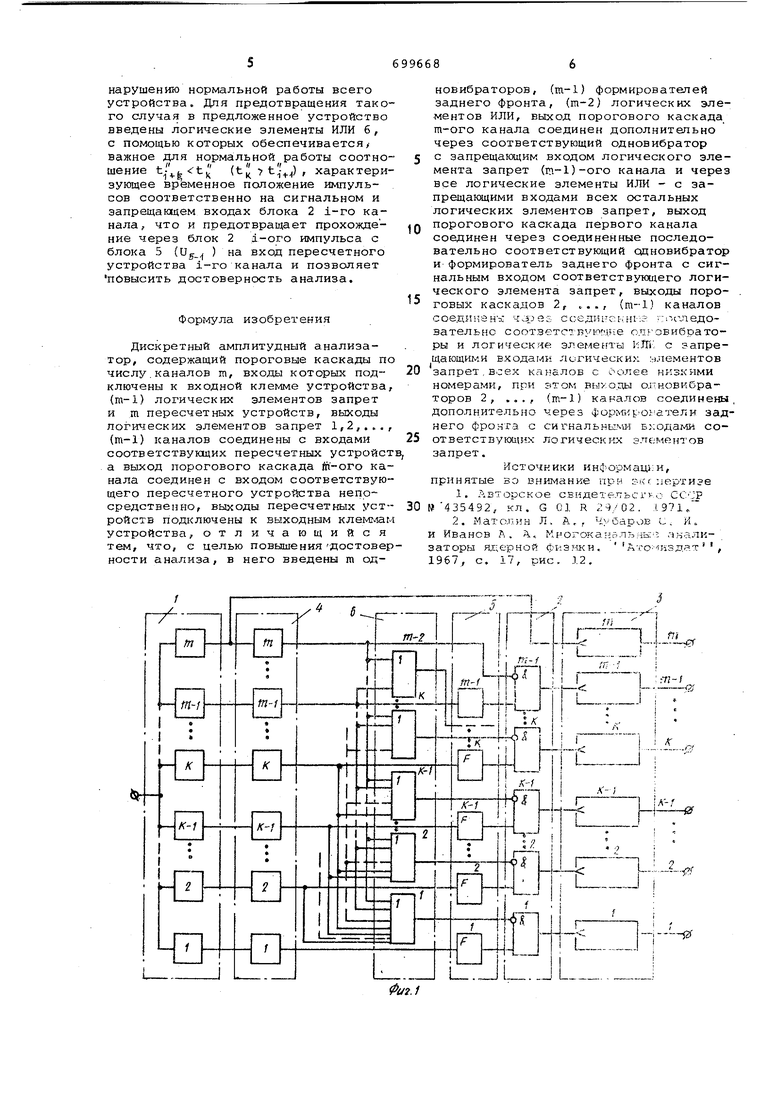

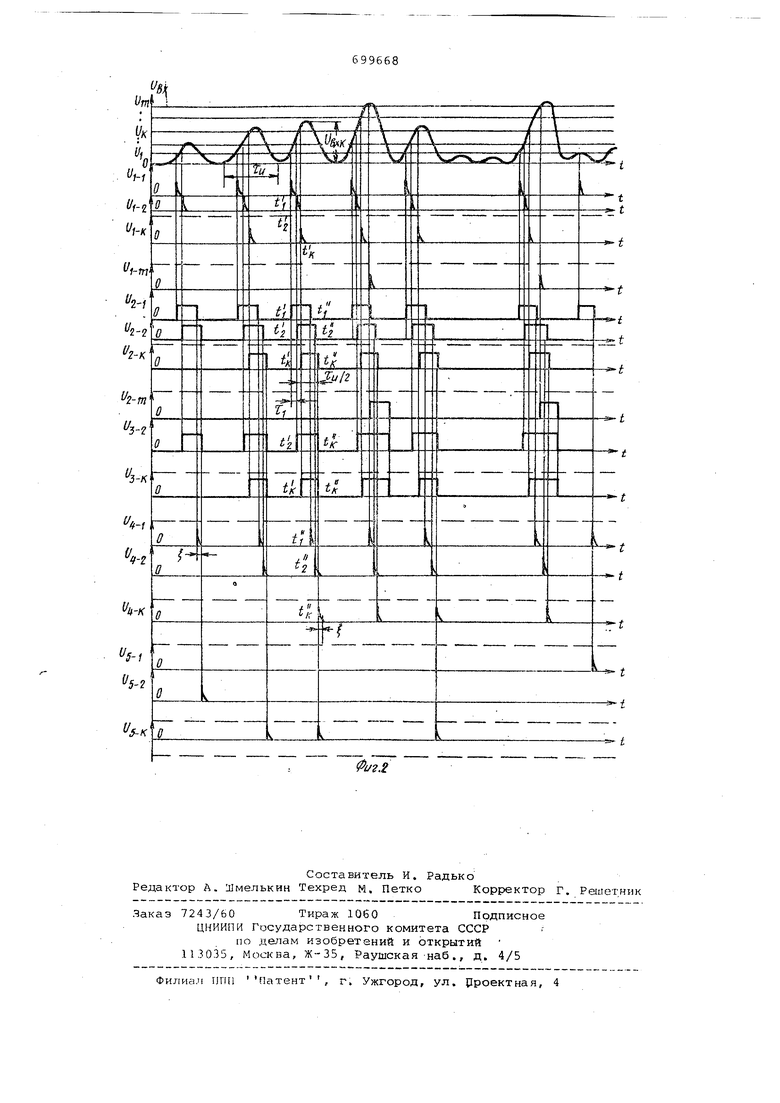

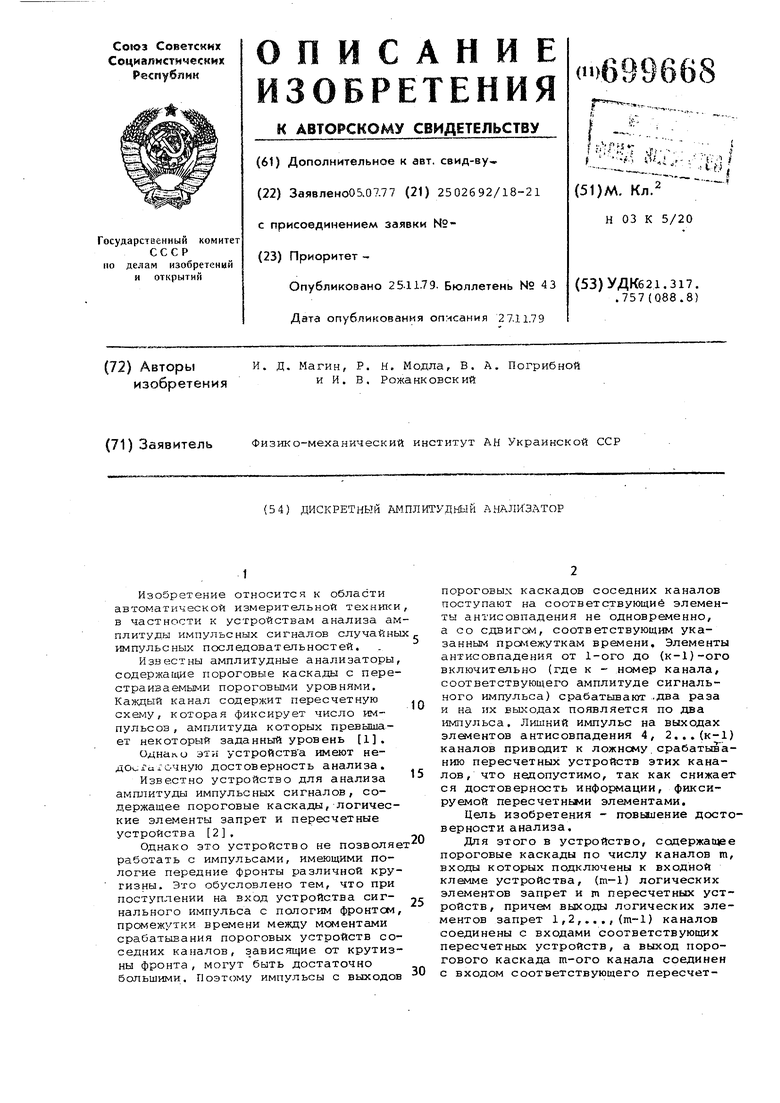

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - временные диаграммы, поясняющие работу устройства.

Устройство содержит пороговые каскады 1(1-1, 1-2,.,.,1-т) по числу ка налов т, т-1 .логических элементов запрет 2(2-1, 2-2,...,2-(т-1), m пересчетных устройств 3(3-1, 3-2,..., 3-т) и одновибраторов 4(4-1,4-2..., 4-т), m-l формирователей 5 заднего фронта (5-1, 5-2,..., 5-(п-1) и .т-2 . логш-геских элементов ИЛИ,б(б-1, 6-2,. ...,б().Уровень срабатывания пороговых каскадов возрастет с во раставнем их номера.

Дискретный амплитудный анализатор работает следующим образом.

Импульсы амплитуды UBX.к. произ водьной крутизной фронтов и постоянной длительности, подлежащие анализу поступают на входы пороговых каскадов неех каналов (1,2, 3,... ,т) . При этом срабатывают тЪлько те пороговые каскады, уровень срабатывания ;Которых fexoдитcя ниже амплитуды анализируемого импульса. Таким образом, в моменты t , t2, ..., tjtна выходах соответствукхцих пороговых каскадов появляются импульсы, сдвинутые относительно друг друга соответственно на , С, .., ,Т.,причем сдвиг по времени между такими импульсами определяется крутизной фронта анализируемого импульса (в случае идеально крзлтого переднего фронта анализируемого

импульса все пороговые каскады в идеальном случае срабатывают в.один и тот же мсмент времени, т.е. t, t2 ... tK) . Импульсы U , и 2 , , ,f , с пороговых каскадов поступают на соответствующие одно.вибраторы 4-1, 4-2, ... 4-К. В результате на выходах этих одновибраторов формируются- прямоугольные импульсы длительностью Т |/2 сдвинутые относительно друг друга на промежутки времени, зависящие от t , Tg, . . . , TI . Каждый из таких импульсов поступает на соответствующие канальные формирователи 5 заднего фронта, а также через логические элементы ИЛИ б на запрещанлцие входы логических эле1иентов запрет с более низкими номерами. На сигнальные входы логических элементов запрет 2-1, 2-2, ..., 2-К в моменты времени , tg, ..., поступают импульсы . U4-i , U4-, ...,U4-k, сформированные соответствугацими формирователями 5 заднего фронта. На запрещающих входах соответствующих логических элементов запрет имеются импульсы и., ..., ид((фиг. 2). При этом для каждого логического элемента 2-1, 2-2-, ..., 2(к-1) справедливо неравенство t . Следовательно, в момент времени t li ,

/ к-н через сигнальные входы

0 t

г

логических элементов 2-1, 2-2, ... ,... 2-(К-1) импульсы и. , Uj, .2 f . . ., U.((;.,) не проходят и соответствующие пересчетные устройства не сраба тывают. Ввиду того, что на запрещаю, щем входе логического элемента 2-К импульс отсутствует, в момент времени t ц этот элемент срабатывает и сигнал поступает на вход пересчетного устройства 3 К-ого канала. Если амплитуда поступающего импульса превышает порог срабатывания порогового каскада 1-т, то импульс, появляющийся при его .срабатывании, непосредственно поступает на вход блока 3-т. При этсм на выходах всех остальных логических элементов запрет 2 импульсы отсутствуют.) При анализе импульсных сигналов с достаточно крутыми передними фронтами промежутки времени т, ..., Тц малы. Вследствие этого задние фронты импульсов на выходах одновибраторов 4 двух соседних каналов (например i и i + 1, причем i + ) практически совпадают во времени..Если не принято необходимых мер указанное, совпадение фронтов, при котором . , можетвызвать нарушение неравенства ,t. , что в свою очередь может привести к прохождению импульса через блок 2 на блок 3, в результате чего пеоесчетное устройство 3-его канала ошибочнб зафиксирует импульс, соответствующий амплитуде входного сигнала, равной порогуСрабатывания блока 1-К. Это приведет к нарушению нормальной работы всего устройства. Для предотвращения тако го случая в предложенное устройство введены логические элементы ИЛИ 6, с помощью которых обеспечивается,важное для нормальной работы соотно шение (t ) , характери зующее временное положение импульсов соответственно на сигнальном и эапрещаквдем входах блока 2 i-ro канала, что и предотвращает прохождение через блок 2 d-oro импульса с блока 5 (и ) на вход пересчетного устройства i-ro канала и позволяет повысить достоверность анализа. Формула изобретения Дискретный амплитудный анализатор, содержащий пороговые каскады п числу.каналов т, входы которых подключены к входной клемме устройства (т-1) логических элементов запрет и m пересчетных устройств, выходы логических элементов запрет 1,2,.,. (т-1) каналов соединены с входами соответствукщих пересчетных устройст а выход порогового каскада й-ого канала соединен с входом соответствующего пересчетного устройства непосредственно, выходы пересчетных устройств подключены к выходным клем.5ам устройства, отличающийся тем, что, с целью повышения Достовер ности анализа, в него введены m одновибраторов, (т-1) формирователей заднего фронта, (т-2) логических элементов ИЛИ, выход порогового каскада га-ого канала соединен дополнительно через соответствующий одновибратор с запрещающим входом логического элемента запрет (ni-l)-oro какала и через все логические элементы ИЛИ - с запрещаквдими входами всех остальных логических элементов запрет, выход порогового каскада первого канала соединен через соединенные последовательно соответствующий сдновибратор и формирователь заднего фронта с сигнальным входом соответствующего логического элемента запрет, выходы пороговых каскадов 2, „.., (m-l) каналов соедш знл -ирез ссед1И-е .:н1-:г ::гл.едовательнс соответс вуюгдме слковибраторы и логические элементы ИТП с запрещающш«:и входами логическим улементов запрет,всех каналов с оолее низкими номерами, при этом ,ды олновкбраторов 2, ..,, (т-1) каналов соединены, дополнительно через форми ю атели заднего фронта с сигнальнЕз1м 1 входами соответствуюацх логическг-ос элементов запрет. Источники информации, принятые Бо внимание при SKC пертиэе 1. Авторское сБидетельс1ч о ССОР 435492, кл. G 01 R . , 2. Матолин Л. А,, чубароЕ С. И. Иванов А. А Мрогокалгалтзяь ; лк-алиаторы ра:;ерной фразики. Аточкздат , 967, с. 17, рис. 12,

Авторы

Даты

1979-11-25—Публикация

1977-07-05—Подача