(54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения цифровой информации с носителя магнитной записи | 1987 |

|

SU1427419A2 |

| Устройство для контроля качества магнитного носителя | 1984 |

|

SU1182576A1 |

| Устройство для синхронизации многоканального воспроизведения с носителя магнитной записи | 1982 |

|

SU1020859A2 |

| Устройство для синхронизации многоканального воспроизведения с носителя магнитной записи | 1981 |

|

SU960924A1 |

| Устройство для воспроизведения двоичных сигналов с носителя магнитной записи | 1986 |

|

SU1377903A1 |

| Устройство для воспроизведения сигналов цифровой информации с носителя магнитной записи | 1982 |

|

SU1040516A1 |

| Устройство для воспроизведения цифровой информации с носителя магнитной записи | 1983 |

|

SU1103283A1 |

| Устройство для воспроизведения цифровой информации с носителя магнитной записи | 1988 |

|

SU1571656A2 |

| Устройство для воспроизведения цифровой информации с носителя магнитной записи | 1985 |

|

SU1275530A1 |

| Устройство для контроля качества магнитного носителя | 1986 |

|

SU1531155A1 |

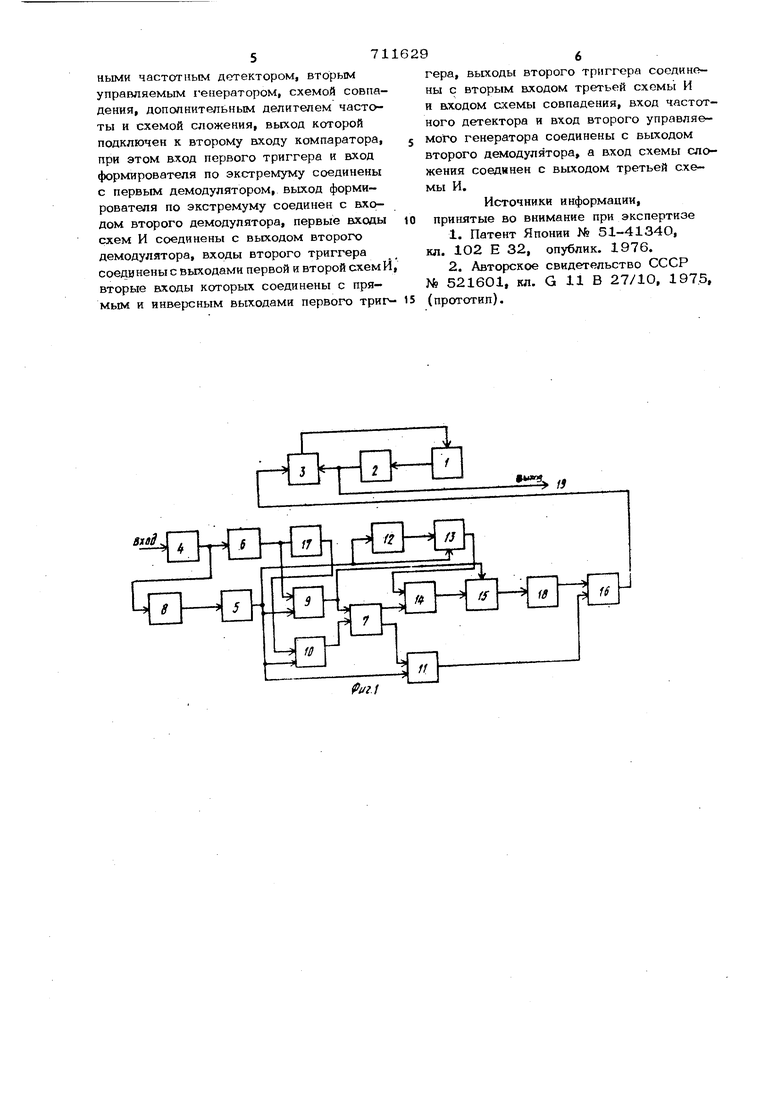

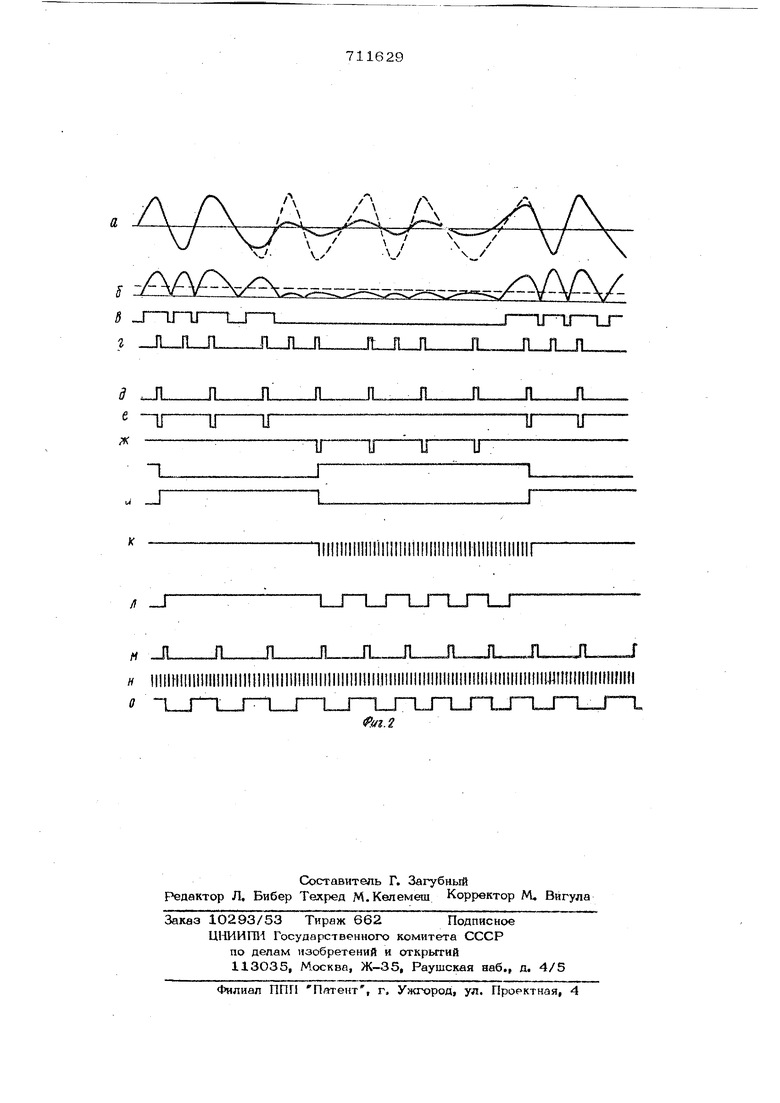

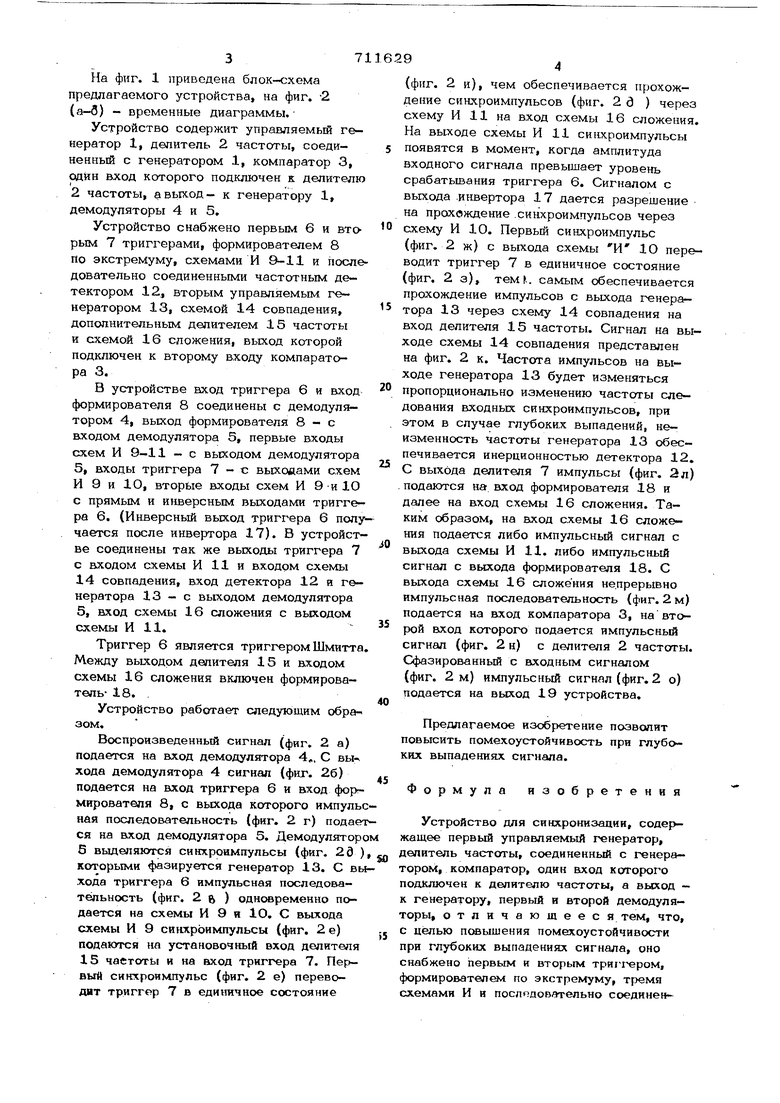

Изобретение относится к технике магнитной записи. Известно устройство, выполненное с линией задержки и коммутатором ll. При выпадении сигнала известное устройство позволяет заменить выпавший сигнал сигналом предшествующей строки Недостатком устройства является то, что оно не обеспечивает замены сигнала при глубоких выпадениях. Наиболее близким по технической сущ ности к изобретению является устройство, содержащее управляемый генератор, соединенный с генератором делитель час тоты и компаратор L2j. Устройство содержит также демодуляторы синхросигна лов. Целью изобретения является повышение помехоустойчивости при глубоких выпадениях сигнала. С этой целью предлагаемое устройство снгзбжено первым и вторым триггером формирователем по экстремуму, тремя схемами И и последовательно соединенными частотным детектором, вторым управляемым генератором, схемой совпадения, дополнительным делителем частоты и схемой сложения, выход которой подключен к второму входу компаратора, при этом вход первого триггера и вход формирователя по экстремуму соединены с первым демодулятором, выход формирователя по экстремуму соединен с входом второго демодулятора, первые входы схем И соединены с выходом второго демодулятора, аходы второго триггера соединены с выходами первой и второй схем И, втррьге входы которых соединены с прямым и инверсным вьсходами первого триггера, выходы второго триггера соединены с вторым аходом третьей схемы И и входом схемы совпадения, вход частотного детектора и вход управляемого генератора соединены с выходом второго демодулятора, а ьход схемы сложения соединен с выходом третьей схемы И. На фиг. 1 приведена блок-схема предлагаемого устройства, на фиг. -2 (а-б) - временные диаграммы. Устройство содержит управляемый генератор 1, делитель 2 частоты, соединенный с генератором 1, компаратор 3, один вход которого подключен к делителю 2 частоты, авьгкод- к генератору 1, демодуляторы 4 и 5, Устройство снабжено первым 6 и вторым 7 триггерами, формирователем 8 по экстремуму, схемами И 9-11 и после довательно соединенными частотным детектором 12, вторым управляемым генератором 13, схемой 14 совпадения, дополнительным делителем 15 частоты и схемой 16 сложения, вькод которой подключен к второму входу компаратора 3. В устройстве вход триггера 6 и вход формирователя 8 соединены с демодулятором 4, выход формирователя 8 - с входом демодулятора 5, первые в.ходы схем И 9-11 - с выходом демодулятора 5, аходы триггера 7 - с выходами схем И 9 и 1О, вторые входы схем И 9 и Ю с прямым и инверсным выходами триггера 6. (Инверсный выход триггера 6 полу чается после инвертора 17). В устройст ве соединены так же выходы триггера 7 с аходом схемы И 11 и входом схемы 14 совпадения, вход детектора 12 и генератора 13 - с выходом демодулятора 5, вход схемы 16 сложения с выходом схемы И 11. Триггер 6 является триггером Шмитта Между выходом делителя 15 и входом схемы 16 сложения включен формирователь- 18. . Устройство работает следующим образом. Воспроизведенный сигнал (фиг. 2 а) подается на вход демодулятора 4,. С вЫ хода демодулятора 4 сигнал (фиг. 26) подается на вход триггера 6 и вход фор мироватепя 8, с выхода которого импуль ная последовательность (фиг. 2 г) пода€ ся на вход демодулятора 5. Демодулятор S вьщеяяются синхроимпульсы (фиг. 23 которьпч1И фазируется генератор 13. С в хода триггера 6 импульсная последовательность (фиг. 2 в ) одновременно подается на схемы И 9 и 1О. С выхода схемы И 9 синхроимпульсы (фиг. 2 е) подаются на установочный вход делителя 15 чаетотьг и на вход триггера 7. Первый синхроимпульс (фиг. 2 е) переводит триггер 7 в единичное состояние (фиг. 2 и), чем обеспечивается прохождение синхроимпульсов (фиг. 2 д ) через схему И 11 на вход схемы 16 сложения. На выходе схемы И 11 синхроимпульсы появятся в момент, когда амплитуда входного сигнала превышает уровень срабатывания триггера 6. Сигналом с выхода .инвертора 17 дается разрешение на прохождение .синхроимпульсов через схему И 10. Первьй синхроимпульс (фиг. 2 ж) с выхода схемы И 10 переводит триггер 7 в единичное состояние (фиг. 2 з), тeм. самым обеспечивается прохождение импульсов с выхода генера- тора 13 через схему 14 совпадения на вход делителя 15 частоты. Сигнал на выходе схемы 14 совпадения представлен на фиг. 2 к. Частота импульсов на выходе генератора 13 будет изменяться пропорционально изменению частоты следования входных синхроимпульсов, при этом в случае глубоких выпадений, неизменность частоты генератора 13 обеспечивается инерционностью детектора 12. С выхода делителя 7 импульсы (фиг. 2л) подаются на вход формирователя 18 и далее на вход схемы 16 сложения. Таким образом, на вход схемы 16 сложения подается либо импульсный сигнал с выхода схемы И 11. либо импульсный сигнал с выхода формирователя 18. С вькода схемы 16 сложения непрерывно импульсная последовательность (фиг. 2 м) подается на вход компаратора 3, на второй вход которого подается импульсный сигнал (фиг. 2 и) с делителя 2 частоты. Сфазированный с входным сигналом (фиг. 2м) импульсньй сигнал (фиг. 2 о) подается на выход 19 устройства. Предлагаемое изобретение позволит повысить помехоустойчивость при глубоких выпадениях сигнала. Формула изобретения Устройство для синхронизации, содернжащее первый управляемый генератор. делитель частоты, соединенный с генератором, компаратор, один вход которого подключен к делителю частоты, а выход - к генератору, первый и второй демодуляторы, отличающееся тем, что, с целью повышения помехоустойчивости при глубоких выпадениях сигнала, оно снабжено первым и вторым , формирователем по экстремуму, тремя схемами И и послпдовательно соединен571

ными частотным детектором, вторым управляемым генератором, схемой совпадения, дополнительным делителем частоты и схемой сложения, выход которой подключен к второму аходу компаратора, при этом вход первого триггера и вход формирователя по экстремуму соединены с первым демодулятором, выход формирователя по экстремуму соединен с ьходом второго демодулятора, первые входы схем И соединены с выходом второго демодулятора, входы второго триггера соединены с выходами первой и второй схем И, вторые входы которых соединены с прямым и инверсным выходами первого триг9

О

гера, выходы второго триггера соединены с вторым входом третьей схемы И и входом схемы совпадения, вход частотного детектора и вход второго управляемого генератора соединены с выходом второго демодулятора, а вход схемы сложения соединен с выходом третьей схемы И.

Источники информации, принятые во внимание при экспертизе

№ 521601, кл. G 11 В 27/10, 1975, (прототип). г

д . П П n лn,,...fL ППn

Л

Л

Л

JL н о

J

Л

J1™JL..JL-..JL.-.A ||И1Н111111111 П1111И 1111 1111111111 11 111ПИ11Ш1 11111 111П111 Ш1ИШ1П11111Ш1Ш1Ш

Авторы

Даты

1980-01-25—Публикация

1977-12-05—Подача