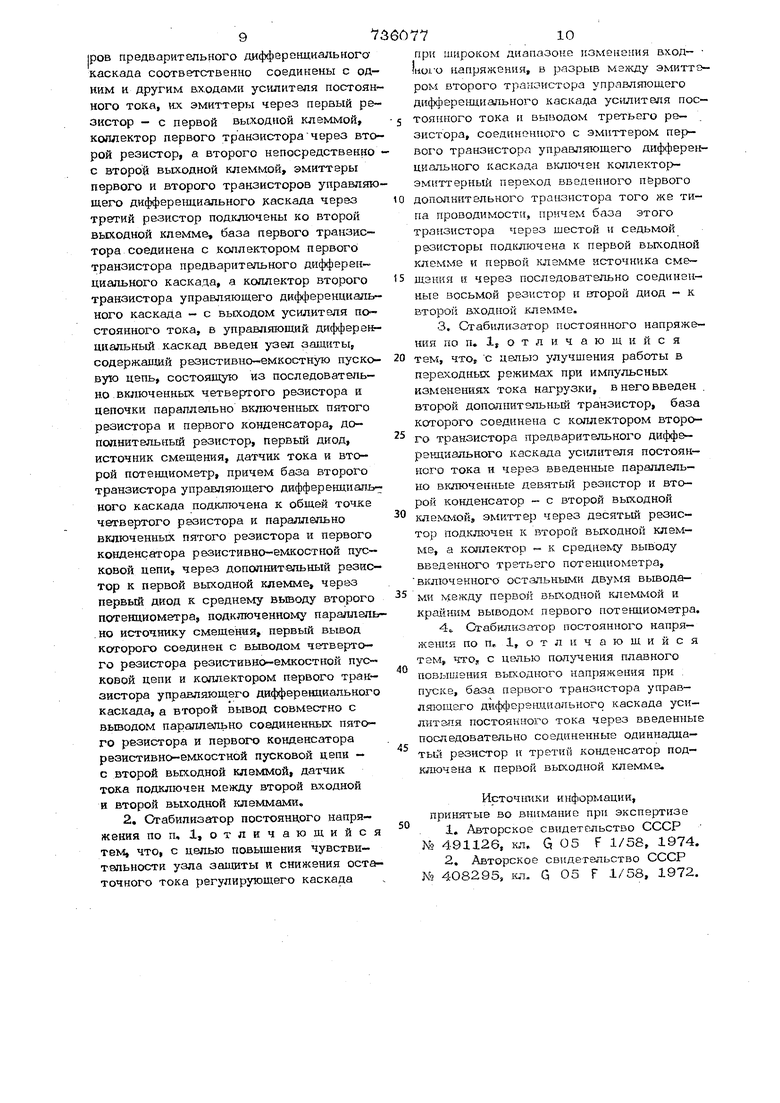

Изобретение относится к электротехнике, в частности к электропитанию радиоэлектронной аппаратуры, и может быть использовано в качестве вторичного источника питания. Известны стабилизаторы постоянного напряжения, содержащие регулирующий элемент, усилитель постоянного тока, схему ср авнения и пусковое устройство, содержащее динистор или однопераходной транзистор, подключенные параллельно регулирующему элементу flj. Недостаток этих стабилизаторов - воз никновение перенапряжений на зажимах нагрузки, вызванных пробоем динистора или двухбазового диода при высоких вход ных напряжениях, что препятствует испол зованию данного стабилизатора для питания интегральных схем, чувствительных к перенапряжениям. TaitHM образом стабилизатор имеет неудовлетворительные импульсные переходные характеристики при значитзльном повыигении в одрюго напряжения. Наиболее близким к изобретению является устройство, которое содержит регулирующий каскад на транзисторах разного типа проводимости, соединенный одним Бьшодом с первой входной, другим - с первой выходной 1шеммами, а управляющим электродом - с выходом усилителя постоянного тока, один вход которого подключен к источнику опорного напряжения, а другой - к среднему выводу первого потенциометра, соединенного двумя остальными вьшодами с первой и второй выходными клрммами 21. Недостаток Дан11ого стаб шизаторя - чрезмерное отпирание транзисторов регулир тощего каскада, большой импульс тока включения, опасный для этих транзисторов. Кроме того, при недостаточной величине емкости коьщенсатора, подключенного параллельно первой и второй : выходным клеммам, в момент пуска происходит кратковременное повышение выходного напряжения- против нормального. Таким образом, стабилизатор имггэт неудовлетворительные пусковые и переходные характеристики и поэтому недостаточно надежен Цель изобретения - .улучшение пусковьге. и импульсных пере.ходньк xapajiTG- ристик стабилизатора постоянного напряжения. Посташшнная цель достигается теМ; что усилитель постоянного тока выполне в виде предварительного и упра&ляющего диффере1щиальньгх каскадов на транзисторах разного типа проводимостИг причем базы первого и второго траязистсров предварительного дифференциального нас- када соответственно соединены с одним и другим входами усилителя: постояннохо тока, Н.Х эмитт&рь. через первьвд оезистор - с первой выходной .ой,, кслле тор первого транзистора через второй резистор, а второго неносредственно - с второй выходной клемм.оЙ8 эмнттэры первого и второго транзисторов управ-ляющего дифференциального каскада чэрез тр етий р езистор Г ош лючены ко 1:;торой в ходной клеммВа база первого транзистора соединена с кетглектором первого транзистора предварительного диффаренциального каскада, а коллектор второго транзистора управляющего дифферандиаль ного каскада - с выходом усилителя пос тоянного тока, в управляющий дигрфврен- циаяьный каскад введен узел заот.итыз, содержащий резистивно-емк.остну1э пусковую цепь, cocTOHiujTo из поелэл.ователь но включенных четвертого резистора и цепочки нарашельно вюноченнью: пятого резистора и первого конден.сгз.тора5 допол нитйльный резистор первый диоД; ясточ ник смещения, датчик тока и второй потенциометр, причем база второго тран™ зистрра управляющего дифференциальног каскада ноД1Шючена к общей точке чет- вертого резистора я параллельно включенных пятого резистора и первого конденсатора резистивно-екжостной пусковой цепил через допопнительньш рззистор к первой выходной через первый диод к среднему выводу зтораго потенциометра подк-ЛЮченноЬГу парал лельно источнику смещения, пер,Е)ый вывод которого соединен с вывoдo i четвертого резистора резистивно-емкост- ной пусковой цепи и коллектором пер-вого транзисаора управляющего дифференциального каскада, а второй вывод совместно с вьшодом паралледько соединенных пятого резистора и пе{)вого 7 4 онденсатора резистивно-емкостной нус овой цепи с второй выходной клеммой, атчик тока подключен между второй входной и второй выходной клеммами. С цепью повышения чувствительности узла заишты к сниж:ения остаточного ока регулирующ.его каскада при щиро- ком диапазоне изменения входного напряжения в разрьш .между эмиттером второго транзистора управляющего дифференциа;1ьно1о каскада усилите ш постоянного тока и выводом третьего резистора, соединенного с эмиттером первого транзистора управляющего ди4х1)ерещ1Иального каскада дзключен коллектор-эмиттерный переход введенного первого дополнительного транзистора того же типа проводи- мости. причем база этого транзистора через шестой и седьмой резисторы подключена к первой вьгходн.ой клемме и первой клемме источника смещения и через последовательно соединенные восьмой резистор и второй диод к второй входной клеьвуШв . С целью улучщения работы в переходнык режимах при импульсных изменениях тока нагрузки в него введен второй дополнительный транзистор, база которого соединена с коллектором второго трав.сзистора предварительного дифференциаль ного каскада усилителя постоянного тока и через введенные параллельно включенные девятый, резистор и второй конденсатор - с второй выходной клеммой эмиттер через десятый резистор подклю--чен к второй выходной кле1 /Оу1е, а коллектор - к среднему выводу введенного третьего потещщометра, подключенного остальньсми двумя вьшодами между первой/выходной клеммой и крайним выводом первого потенциометра. С целью получения плавного повышения выходного напряжения при пуске база первого транзистора управляющего диг зферендиапьного каскада усилителя постоянного тока через введенные после--доватачьно соединенные одиннадцатый резистор и третий ко1Щенсатор подключена к первой выходной клемме, НафиГе 152,3и4 приведены схемы стаб шизатора постоянного напряже1шя с улучшенными пусковыми и импульсными переходными характеристиками. Стабилизатор содержит регулирующий каскад на транзисторах 1 и 2 разного типа проводимости, усилитех/ь постоянн1 го тока, выполненньй в виде предварите.пьного, транзисторы 3 и 4, и управ 5 лшощего, транзисторы 5 и 6, дифферент циальных каскадов, источник опорного напряжения, выполненный на стабилитро не 7 и резисторе 8, подключенных параллельно выходным клеммам, потенцио метр 9 и узел защиты, содержащий рез тивно-емкостную пусковую цепь из резисторов 10 и 11 и конденсатора 12, дополнительный резистор 13, диод 14, потенциометр 15, дополнительный источ ник 16 смешения, и датчик 17 тока. Кроме указанных элементов стабилизато содержит выходной конденсатор 18, под ключенный с нагрузкой 19 к первой 20 и второй 21 выходным KneMJ.iaivi. К первой 22 и второй 23 аходньм клеммам подводится напряжение источни ка энергии, например выпрямителя Устройство работает следующим обра зом. При под1шючении к входным клеммам 22 и 23 источншса энергии транзисторы 1 и 2 регулирующего каскада, а также транзисторы 3,4,5 и 6 закрыты и напря жение на Выходных клеммах 20,21 отсутствует. Одновременно за счет дополнительного источника 16 смещения начи нает заряжаться конденсатор 12 через резистор 10. Когда потенциал базы тра зистора 6 превьшгает пороговое напряжение эмиттерного перехода упомян то- го транзистора последний открывается и включает в работу транзисторы 1 и 2 регулирующего каскада; ток эмиттера транзистора 1 заряжает выходной конденсатор 18, т.е. появляется напряжени на выходньпя 1шеммах 2 О и 21, При этом процесс открывания транзистора 6 и транзисторов 1 и 2 форсируется за Счет тока дополнительного резистора 13 подключенного к базе транзистора 6. Таким образом, на указанной стадии пускового процесса транзисторы 6, 1 и 2 находятся в петле положительной обратной связи, образованной благодаря включению дополнительного резистора 13, что и обеспечивает автоматический запуск схемы, выполненной на транзисторах разного типа проводимости. Вместе с тем характерной особенностью примененного устройства защиты является то, что с появлением выходного напряжения под действием сигнала, поступающего с движка потенциометра 9, всегда первым открывается транзистор 3 предварительного дифферешшального каскада, а -транзисторы 4 и 5 закрыты. Тем самым исшпочается воз77можность запирания в процесса пуска транзистора 6 за счет падения напряжения на резисторе в.обшей цепи транзисторов 5 и 6, которое, зависит от то- ка эмиттера транзистора 5. Лишь тогда, когда выходиоа напряжение достигает номинального уровкяа открываются транзисторы 4 и 5, т.е. на эмиттер транзистора 6 поступает усиленный сигнал рассогласования. словами, вступает в действие контур общей отрицательной обратной связи и переход стаб(шизатора на режима пуска в режим стаб шизации выходного напроЕления не сопровождается. в отличие от известного импульсным выбросом выходного напряжения. В режима нормальной работы CTa6ii- лизатора диод 14 остается почти закрытым что обеспечивается соответствую- щкм подбором положения движка потенциометра 15а При этом изменение тока нагрузки 19 и соответствующее изменение напряжения на датчике 17 тока в мап,ой степени сказывается на режиме работы транзистора 6, При перегрузке или коротком замыкании выхода напряжение на датчике 17 тока существэкио возрастает, вследствие чего диод 14 отпирается и база транзис- тора 6 оказывается подключенной через диод 14 и часть низкоомной рэзистивной цепи делителя к отрицательной аходной клемме 23« Транзистор 6 закрывается, закрываются ц транзисторы 1 н 2 регу- лкрующего каскада, Выхоцноэ напряжение стабилизатора снижается и, когда опорный стабилитрон 7 выходит из режима пробоя, транзисторы 4 и 5 заг рываются, вследствие чего контур общей отрицательной обратной связи оказьшается paзo ыcнy- тым а контур положительной обратной связи создает тендешино к лавинообразному закрыванию транзистора 6 и соот- вэтственно транзисторов 1 и 2. В предлагаемой схеме защиты не возникает импульсных перегрузок по току транзисторов 1 и 2. Стабил1-1трон дополнительно Содержит транзистор 24-5 включенньп последователь™ но в цепь эмиттера транзистора 6 управляющего диффере1щиального каскада усилитачя постоянного тока, причем база допелНЕТачьиого транзистора чефез резисторы 25 и 26 под1шючана к первой вькодной 2О ivqeN-nviG и первой кламме Дополнительного мсточника 16 смйщеккя а через последоватйпьно соединенные резистор 27 и диоды 28j29 к вьь ходной клемме 21,

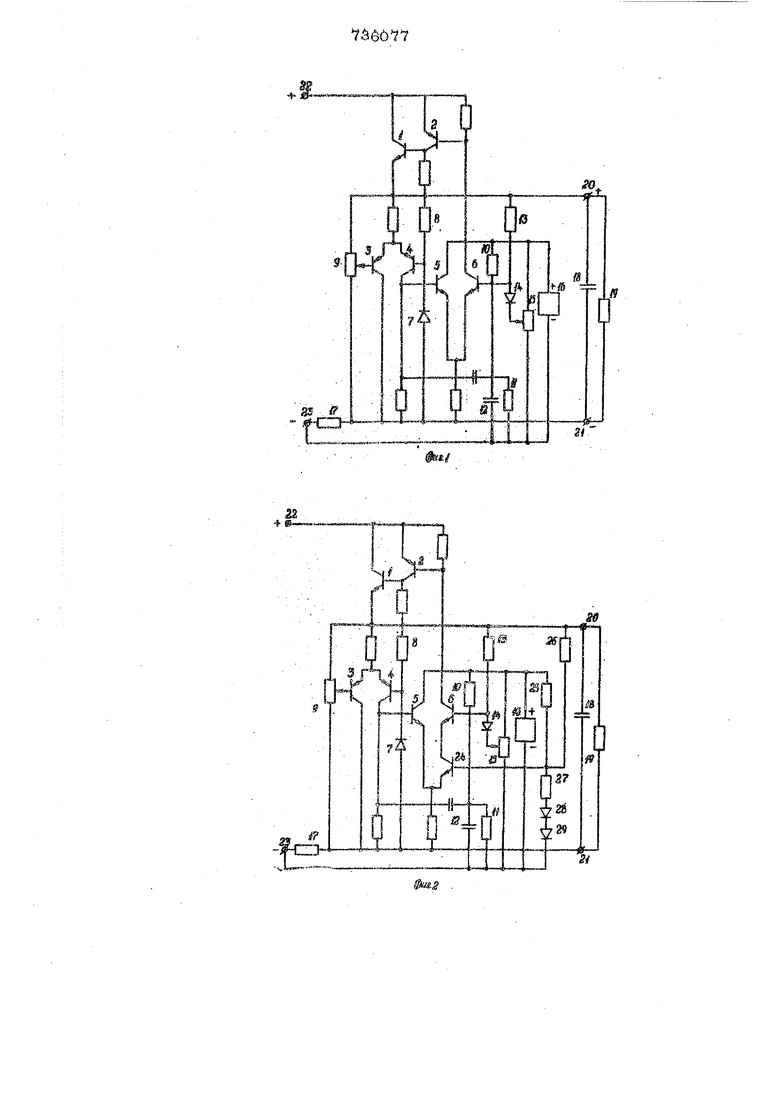

Напряжение смешения на базэ тг1аизи тора 24 выбрано так, чтобь; при пуске и при режиме, стабилизации зтот транзистор находился в режиме насьошэния поэтому в ЭТИ.Х режимах работа стабкли-затора выполне вдого по с. фиг,, 2 не отличается от рабо1ы стабилиза:1-Оэа по схеме фи1 1,

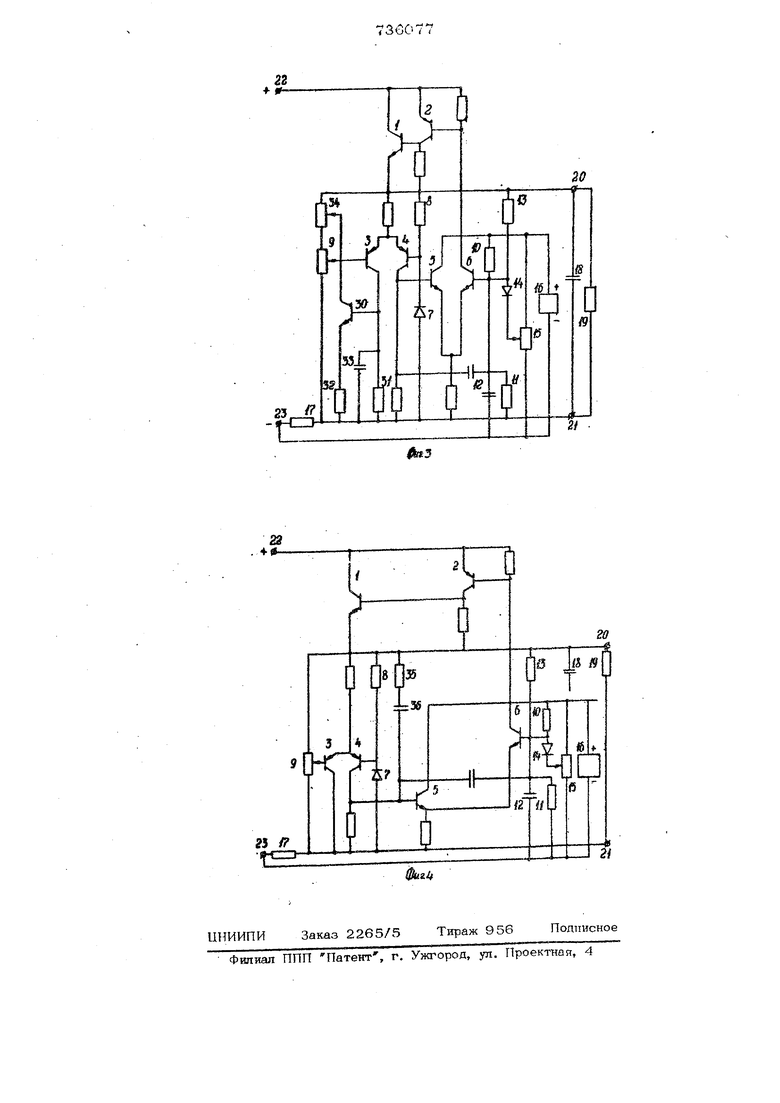

При перегрузке за сче-т действия аепи КЗ резистора 27 и диодов 2.8 и 29 транзистор 24 выходит из режима насыщения и закрывается,, вследстгзиа чего, повышается эффективность запирания транзисторов 6з атакке : 1 к 2, причем остаточный ток тракзисгора 1 оказывается весьма малым при широком дия-пазоне изменений входного напряжения Стабилизатор, показанньи1 на фиг, 3s дополнительно содержит транзистор ЗО, база которого соединена с коллектором транзистора 3 предварительного дигрф-ерепциалыюго каскада усхшитачя постояияого ток.а и через паралл.апьно В1сл.1очег1:н;ыг; ; резистор 31 и конденсатор 32 - с вто ,рой выходной клеммой 21, эмкттпр через резистор 33 .-. с второй выход:юн клеммой 21 а коллектор - с двии-ксм потенциометра 34, подключенного оц.ппы : выводом к первой выходной клемме 2О, а другим - к выводу нотенцнометра 8,

Введение транзистора ЗО создаз-т местную положительную oDpaTijyio с;пязь в предварительном каскаде усилкг зл.я постоянного тока причем козффнцтхент усиления по току транзистора 30 1:;.ыбп рается близким к единкяе за счет иримерного равенства рЕЗисторов 3-1. и 33., Использование транзиртспл ЗО позволяет повысить крутизну измврнтепглюй здепч транзистора 3, увапичйть амш1кту;: irji-ir--нала ошибки на базе транзистора Q л тем самым устранить переходп по iiorpem ность стабилизатора прв ныпупьспът изменениях тока нагрузки. Кроме тсго,, при надлежащем подборе попогксшлг /.ивиж ка потенциометра 34 удается снизить пульсации напряжения на выходе с аоилизегора.

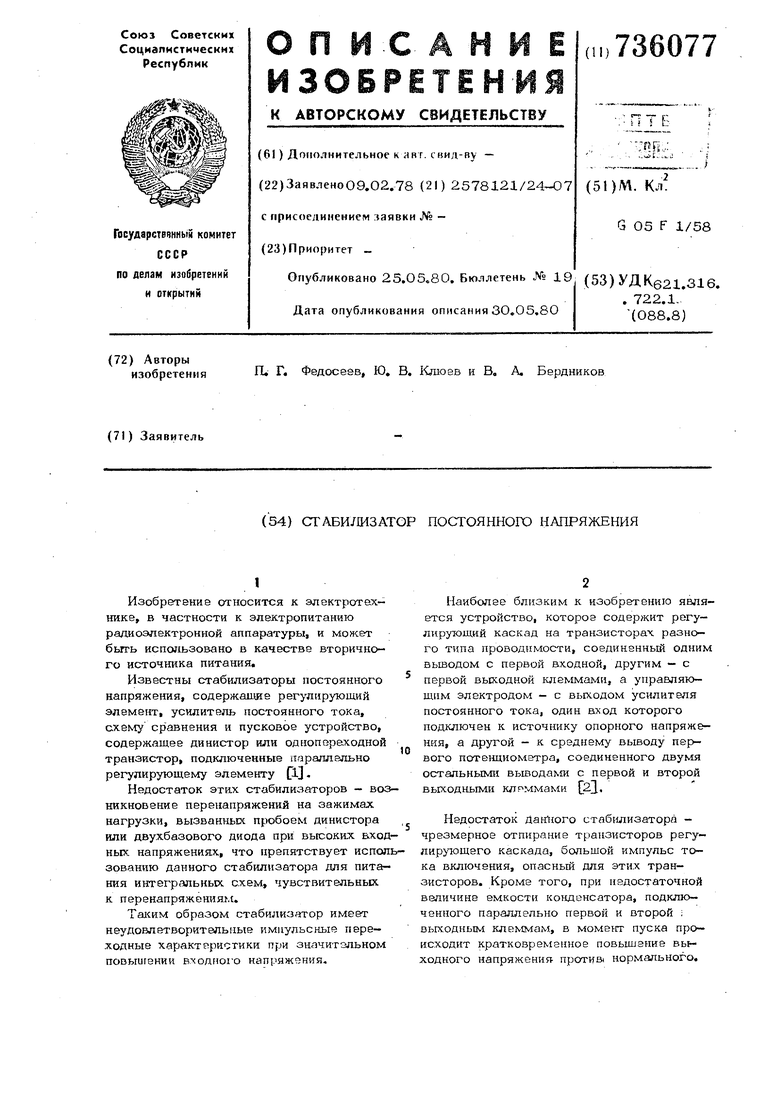

Стабилизатор, показанный на фиг« 4, дополнительно содержит цепочку }ia ио« следовательно соединенных, резистора 3S и конденсатора 36, подключеннукт одним выводом JC. первой выходной клемь е 3,0,, а другим к общей ТОЧКЕ кашектора транзистора 4 предвар-ительного дифц)& рэнциэльного кастсада п база тран-зисто-уTJравляющего диффере1щиального

каскада усилителя постоянно1о тока,

При появлении в режиме пуска вы- .одцо:го нагтряжения зарядный ток ко шенсатора 36 через резистор 35 создает попоисительное смещение на базе транзистора 3. последний приоткрьшается и на эммитер транзистора 6 подается напряжение,, снижающее скорость увеличения тока черэз резистор в цепи коллектора транзистора 6. что и обеспечивает гшав- ное нарастание тока транзисторов 1 и 2g и следовательноэ выходного напряжения от абнлкз ат орас

. образом при включении стабил.чзатора не возникает иеренапряженкй на. выходэ, рагули.ру1ощ 1е транзисторы защи).лен1. от ГЕротекаиия больших токов ари Бкгаочеиии, что обеспечивает более иадежн пю работу самого стабилизатора, обеспечивается более четкое действие aaimribi 1ри перегрузках по току при импульснык. изменения.х тока нагрузки пе всзникаэт рровалов в выходном иа

ПрЯЖЙНИИ,,:

Обеспечивается плавное нарастание амходного напряж.эния при включениях стабилнаатора. представляюш.ее интерес три j-eKOTOpbix режимах работы5 например при ГИтании усилителей мошности от стабЕШИЗИровакных устройств, удается пре дохраинтъ выходные транзисторы усилитепей мощлос1-и от выхода их яз строя в момент включенияв

Фор М- у л а и 3 о б р е т е н и я

1, Стабилизатор постоянного напряжймия,, -:содзржашйй регулирующий каскад на тра :зисторах разного типа проводиKiocTH, соедине)1ный одним выводом с первой входЕоЙЕ, другим - с первой вы

.ходной леммамИз а управляющим электродом - с выходом уСИ,.ПИТСЗЛ.Я noCTOfiHED ГО ТОК-З. один аКОД которого ПОД1€ЛЮЧЭН

к источнику опорного иапрянсенияе а дру-.гой к среднему выводу первого потан.и,иометра| соединенного двумя остальными ВЫВОДШЛИ с ЕТ&рВОЙ и второй ВЫХОДНЫМИ гшеммамк, отличающий-с я TBMj что, с ивлью улучшения пуско- вьЕК i импульсньгл пер)еходньгх .характеристик, усщ1итель постоянного тока выпол--нец в .виде предваритапьного и упраЕ«1Ш(щзго дифференциальных каскадов, на тра№- знсторах разного типа проводимости; причем базы первого и .второгч) тракзисто9ipoB предварительного дифференциадьиога каскада соответственно соединены с од ним и другим входами усилителя постоя ного тока, RX эмиттеры через первый ре зистор - с первой выходной клеммой, коллектор первого транзисторачерез вт рой резистор, а второго непосредственно с второй выходной клеммой, эмиттеры первого и второго транзисторов управляю щего дифференциального каскада через третий резистор подключены ко второй выходной клемме, база первого транзистора соединена с коллектором первого транзистора предварительного дифференциального каскада, а коллектор второго транзистора управляющего дифференциаль ного каскада - с выходом усилителя постоянного тока, в управлдаощий дифферек цкальный каскад введен узЕщ защиты, содержаний резистивно-емкостную пуско вую цепь, состоящую из последовательно включенных четвертого резистора и цепочки параллельно включенных пятого резистора и первого конденсатора, дополнительный резистор, первый диод, источник смещения, датчик тока к второй потенциометр, причем база второго транзистора управляющего дифференциап.ь ного каскада подключена к общей точке четвертого резистора и параллельно включенных пятого резистора и первого конденсатора резистивно-емкостной пусковой цепи, через дополнительный резистор к первой выходной клемме, через первый диод к среднему выводу второго потенциометра, подключенному параллель . но источнику смещения, первый вывод которого соединен с выводом четвертого резистора резистивно-емкостной пусковой цепи и коллектором первого транзистора управляющего дифференциального каскада, а второй вывод совместно с вьтодом параллельно соединенных пятого резистора и первого Конденсатора резистивно-емкостной пусковой цепи с второй выходной клеммой, датчик тока подключен между второй входной и второй выходной ыгеммами, 2. Стабилизатор постоянного напря- «ения поп, 1, отличающийся тем, что, с целью повышения чувствительности узла зашиты и снижения остаточного тока регулирующего каскада 77 при широком диапазоне изменения вход- но1о напряжения, в разрыв мэжду эмиттз- ром второго транзист-ора управляющего дифференциального каскада усилителя постоянного тока и выводом третьего резистора, соединониого с эмиттером первого транзистора управляющего дифференциального каскада включен коллектор- эмиттерньй переход введенного первого дополнительного транзистора того же типа проводимости, причем база этого транзистора через шестой н седьмой резисторы под1шючена к первой выходной клемме и первой клэмме источника сме- щэнкя я через последовательно соединенные восьмой резистор и второй диод - к второй входной клемме, 3, Стабилизатор постоянного напряжения по и, 1, о т л и ч а ю щ и и с я тем, что, С целью улучп1ения работы в переходных режимах при импульсных изменениях тока нагрузки, в него введен . второй дополнительный транзистор, база которого соединена с коллектором второго транзистора предварительного дифференциального каскада усилителя постоянного тока и через введенные параллельно включенные девятый резистор и второй конденсатор - с второй выходной клеммой, эмиттер через десятый резистор подключен к второй выходной клемме, а коллектор к среднему выводу ВБэдекного третьего потенциометра, включенного остальными двумя выводами между первой выходной клеммой и крайним выводом первого потенциометра. 4 Стабилизатор постоянного напряжения поПе, 1, отличающийся тем, что, с целью получения плавного повышения выходного напряжения при пуске, база первого транзистора управляющего дифферэнциапьного каскада усилитапя постоянного тока через введенные последовательно соединенные одиннадцатый резистор и третий конденсатор подключена к первой выходной клемма. Источтши информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР й 49И26, кл. О, 05 F 1/58, 1974. 2,Авторское свидетельство СССР № 4О8295, кл. Q 05 Г 1/58, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизатор повышенного напряжения постоянного тока | 1982 |

|

SU1086415A1 |

| Стабилизатор напряжения с самозащитой | 1982 |

|

SU1046751A1 |

| Стабилизированный источник питания | 1985 |

|

SU1265745A1 |

| Ключевой стабилизатор напряжения постоян-НОгО TOKA | 1978 |

|

SU845146A1 |

| Устройство электронной защиты | 1982 |

|

SU1136133A1 |

| ПОНИЖАЮЩИЙ СТАБИЛИЗАТОР | 2007 |

|

RU2339072C1 |

| СТАБИЛИЗАТОР НАПРЯЖЕНИЯ | 1991 |

|

RU2079871C1 |

| Стабилизатор постоянного напряжения | 1979 |

|

SU943674A1 |

| Стабилизатор постоянного напряжения | 1980 |

|

SU892429A1 |

| Импульсный стабилизатор напряжения постоянного тока | 1986 |

|

SU1410003A1 |

89

Авторы

Даты

1980-05-25—Публикация

1978-02-09—Подача