(54) МАЖОРИТАРНО-РЕЗЕРВИ РОВАННОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное резервированное аналоговое устройство | 1981 |

|

SU1051751A1 |

| Устройство для индикации отказов в трехканальной вычислительной системе | 1989 |

|

SU1721608A1 |

| Трехканальное резервированное устройство | 1976 |

|

SU618875A1 |

| Мажоритарное устройство | 1980 |

|

SU892732A1 |

| Трехканальное резервированное устройство | 1981 |

|

SU957451A1 |

| Многоканальное устройство для резервирования линии связи | 1976 |

|

SU698175A1 |

| Мажоритарно-резервированное устройство | 1989 |

|

SU1633409A1 |

| Многоканальное резервированное аналоговое устройство | 1980 |

|

SU984089A2 |

| Аналоговое мажоритарное устройство | 1983 |

|

SU1203697A1 |

| Мажоритарное устройство | 1981 |

|

SU1096767A1 |

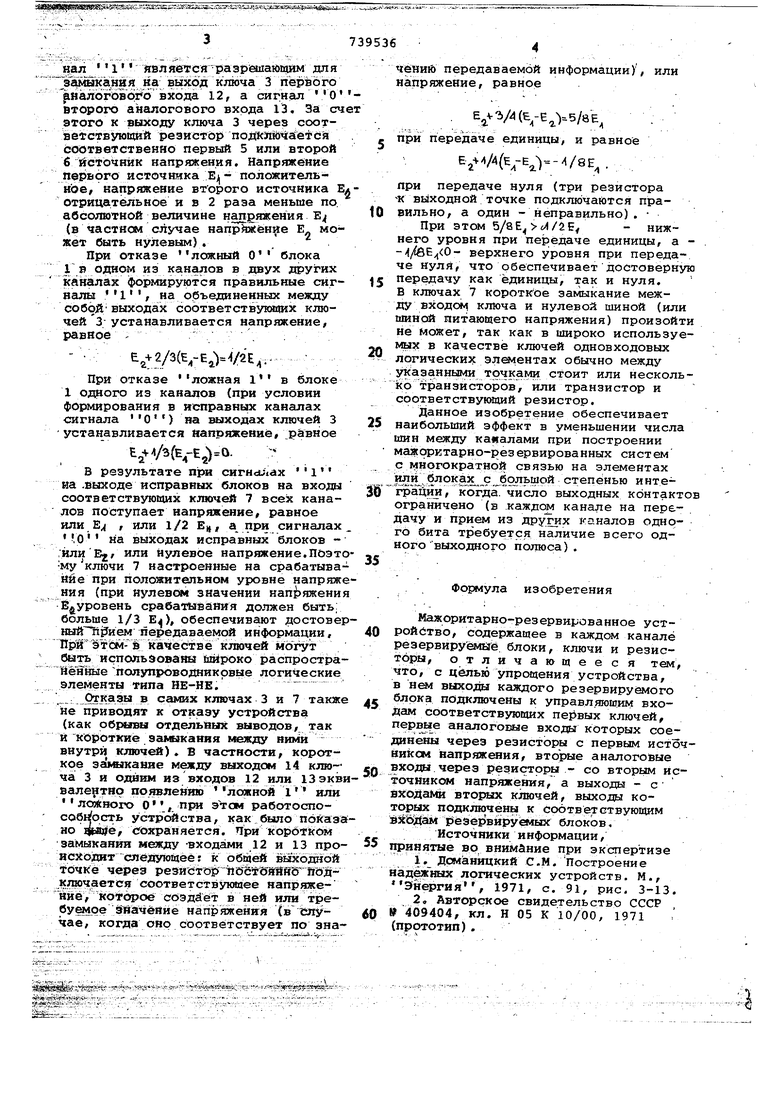

.1 . . . .. Изобретение относится к области .автоматики и вычислительной техники и может быть использовано при построении высоконадежных систем переда ;чи дискретной информации между резервированными логическими блоками. Известно мажрритарно-резервирова:нное устройство, содержащее резер руемые блоки, выходы которых СОёдИнены с соответствующими входами каж из мажоритарных блоков 1. Недостаток устройства - большое число рвязей между выходами резервируемых блоков и входами мажоритарных блоков, в разных каналах. Наиболее близким техническим решением к данному изобретению явля,ется, мажоритарно-резервированное уст{ Ьй :тво, содержащее в каждом канале, рез ёрвируемые блоки, ключи и резисторы 2. Недостаток устройства - сложност реализации, особенно при большом числе выходов у резервируемых блоков. Цель изобретения - упрощение уст ройства. Поставленная цель достигается тем, чтоВ мажоритарно-резервирован устройстве выходы каждогс5 резервируемого блока подключены к управляющим входам соответствующих первых ключей, первые аналоговые входы которых соединены через резисторы с первым источникс напряжения, вторые аналоговые входы через резисторы - со вторым источником напряжения, а выходы С входами вторых ключей, выходы которых подключены к соответствующим входам резервируемых блоков. На чертеже приведена блок-схема мажоритарно-резервированного устройства, . Устройство содержит резервируемые блоки 1, узлы 2, первые ключи 3, резисторы 4, шину первого 5 и шину второго 6 .кс т очников напряжения, вторые ключи 7, первый, второй и третий каналы 8-10 устройства, управляющий вход 11, первый и второй аналоговые входы 12-13 и выход 14 первого ключа. . Мажоритарно-резервированное устройство рабртает следующим образом. При выдаче информации из блоков 1, находящихся в одном узле 2, в блоки 1 следующегоузла 2 в каждом иЗ;, передаваемых двоичных разрядов сигявляетсяразрешайщйм для замыканяя на выход ключа 3 пёраого нал6г6вр1 о входа 12, а сигнал VO второго аналогового входа 13. За сч этого к выходу ключа 3 через соотаетствующий резистор подкию ается соответственно первый 5 или второй 6 источник напряжения. Напряжение первого источника Е положительное, напряжение второго источника Е отрицатёльное и в 2 раза меньше по. абсолютной величине на тряжеиия E (в частном случае нап Йжёние Е может быть нулевым). При отказе ложный О блока 1 в одном из каналов в двух других каналах формируются правильные сигналы , на объединенных между собой; выходах соответствующих ключейЗ; устанавливается напряжение, равное . . . ; , : . V3(,r При отказе ложная 1 в блоке 1 одного из каналов (при условии формирования в исправньпс каналах сигнала О) на выходах ключей 3 устанавливается йапряжение, равное (.О. В результате при сигнси1ах « на .выходе исправных блоков на входы соответствующих ключей 7 всех каналов поступает напряжение, равное или Е , или 1/2 EI,, а при сигналах ,0 на выходах исправных блоков ,нли Ej, или нулевое напряжение.ПОэт му ключи 7 настроенные на срабатыва ние при положительном уровне напряж ния (при нулевом значении напряжени Ё,уровень срабатывания должен быТь; больше 1/3 Е, обеспечивают достове передаваемой информации, качестве ключей могут быть использованы Ыйроко распростра йёнйые полупроводниковые логические элементы типа HE-HE. .: Отказы в самих ключах 3 и 7 такж не приводят к отказу устройства (как обрывы отдельных выводов/ так икороткие заявлкания между ними внутри ключ) . В частности, короткое зг мыкаш1е между выходом 14 ключа 3 и одним из входов 12 или 13ЭКВ появлению ложной 1 или ложного О , при этом работоспособ1 ость устройства, как было показ но щаяё, сохраняется. При коротком замыкании методу -входами 12 и 13 про исходит следутощеё; к обгаей выходной точке через резистор 11еётейНЯе 17бдключается соответствующее напряженйё, которое создаёт в ней или требуетлре этйачёнйё напрйкения (в 15яучае, когда оно соответствует по зна

;s rre-:: 5 : t«s;.

.i;--2-4 - -K; ; ;:

v.4-;-

739536 чений передаваемой информации), или напряжение, равное V / V V-S/BE . при передаче единицы, и равное ,. при передаче нуля (три резистора К выходной точке подключаются праВИЛЬНО/ а один -неправильно). При этом 5/8Е бИ/2Е/ - нижнего уровня при передаче единицы, а - . -4/feE 0- верхнего уровня при передаче нуля, что обеспечивает достоверную передачу как единицы/ так и нуля. В ключах 7 короткое замыкание между входог ключа и нулевой шиной (или шиной питающего напряжения) произойти не Может/ так как в широко используемых в качестве ключей одновходовых логических элементах обычно между указанныкш точками стоит или несколько транзисторов/ или транзистор и соответствукяций резистор. Данное изобретение обеспечивает наибольший эффект в уменьшении числа шин между каналами при построении мажоритарно-резервированных систем с многократной связью на элементах или блоказс с б ольшой степенью и нтеrpaUHji, когда, число выходных контактов ограничено (в кажрО2«1 канале на передачу и прием из других каналов одного бита требуется наличие всего одного выходного полюса). Формула изобретения Мажоритарно-резервированное устройство/ содержащее в каждом канале резервируёмаё блоки, ключи и резистбры/ отличающееся тем, что, с целью упрощения устройства/ в я&л выходы каждого резервируемого блока подключены к управл.яюшим входам соответствующих первых ключей/ аналоговые входы которых соединены через резисторы с первым источником напряжения, вторые аналоговые входы.через резисторы ,- со вторым источнике напряжения, а выходы - с входами вторых ключей, выходы которывс подключены к соответствующим вхойам резервируемых блоков. Источники информации, принятые во. внимание при экспертизе 1. Дсманицкий С.М. построение надежнЕях логических устройств. М./ Энергия / 1971/ с. 91/ рис. 3-13. 2, Авторское свидетельство СССР 409404/ кл. Н 05 К 10/00, 1971 (прототип).

Авторы

Даты

1980-06-05—Публикация

1977-08-17—Подача