(54) СТУПЕНЧАТО-ЛИНЕЙНЫЙ ЭКСТРАПОЛЯТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Ступенчато-линейный экстраполятор второго порядка | 1977 |

|

SU705472A1 |

| Линейный экстраполятор | 1977 |

|

SU691882A1 |

| Цифро-аналоговый экстраполятор | 1978 |

|

SU752380A1 |

| Ступенчато-линейный экстраполятор | 1976 |

|

SU627489A1 |

| Экстраполятор | 1977 |

|

SU696493A1 |

| Линейный экстраполятор | 1981 |

|

SU1024943A1 |

| Линейный экстраполятор | 1976 |

|

SU627490A1 |

| Ступенчато-линейный экстраполятор | 1976 |

|

SU591873A1 |

| Линейный экстрополятор | 1987 |

|

SU1571625A1 |

| Устройство для восстановления непрерывных функций по дискретным отсчетам | 1983 |

|

SU1124338A1 |

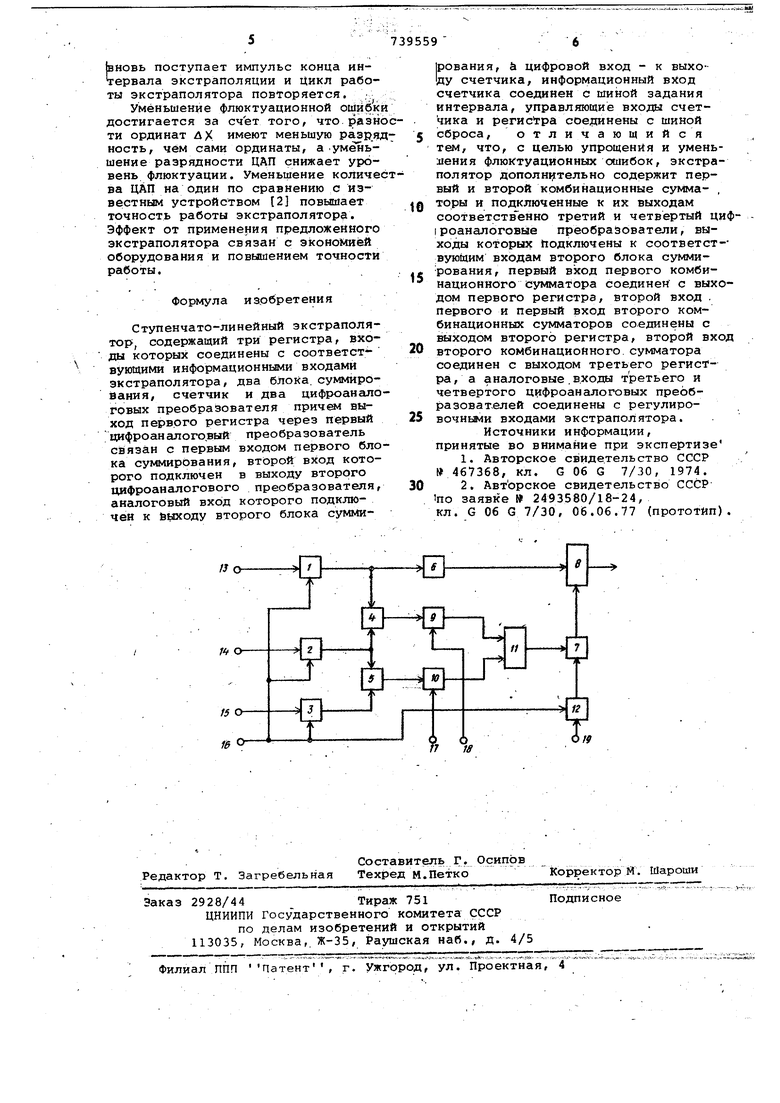

Изобретение относится к вычислительной технике и автоматике и может быть Использовано для экстраполяции функций, задаваемых цифроВ1Я4И кодами ординат, следующих в об щем случае через неравные интервалы изменения аргумента, с представлением результата экстраполяции в аналоговой форме. / Известны аналогичные устройства, вырабатывающие учрежденные значения функции по нескольким зафиксированн значениями 1J и 2. Известен экстрапоЛятор 1, содержащий трехразрядный аналоговый регистр сдвига и три дифференциальных интегрирующих операционных усилителя с разрядными Ключами в цепях обратной связи, подключенных к соответствующим выходам регистра, причем выходы двух усилителей связа .ны.с входом третьего усилителя. Зкс траполятор вырабатывает экстраполирующий полином второго порядка, Такой экстраполятор характеризуется недостаточной точностью из-за наличия аналогового регистра сдайга и аналоговых ключей, а также .невозможностью.работы с неравноотстоящими ординатами функции. ( Наиболее близким к предложенному экстраполятору по технической сущности яв1ляется ступенчато-линейный экстраполятор, содержащий три ячейки памяти на цифровых регистрах с подключенн ;ми к ним цифроаналоговыми преобразователями, выходы ячеек памяти связаны с первым и вторым блоками суммирования, причем выход одного иэ блоков сумкмрования и счетчика, задающего интервал экстраполяции, подключены к соответствующим входам цифроаналогово1го преббразователя, выполняющего роль блока умножения, его выход подключен к входу другого блока суммирования, выход которогоявляется выходом экстраполятора. Кроме того, экстраполятор имеет три регулировочных входа, на которые подаются аналоговые сигналы, характеризующие взаимное расположение на оси времени тройки соседних ординат функции, а также сигнал, задаюьдай маоатаб единищл отсчета времени. Укаэантге сигналы поступают в блок фЬрмЙ рЪванйя коэффициентов, на выходе которого вырабатыва|ются сигналы (весовые коэффициенты) масштабирующие информацию, содержащуюся в ячейках памяти 12J. iHefldd-fatuK этого экстраттЪляторавысокие аппаратурные затраты и сравнительно высокий уровень флюктуации, обуслЬвленный как количеством цифро аналоговых преобразователей, являющи ся источниками флюктуации, как и их сравнительно большой разрядностью, продиктрванной особенностями блоксхемы, Дёль изобретения заключается в Упрощений и уменьшении флюктуационны ошибок. Это достигается тем, что ступен. чато-линейный экстраполятор, содержа щий три регистра, входы которых .соед нены с соответствующими информационн ми входами экстраполятора, два блока суммирования, счетчик и два цифроараЛОгОйых преобразователя, прйчш выход первого регистра через первый цифроаналоговый преобразователь связан с первьЁМ входом пер jBoro BHoka суммировании я, ТШторого подключен к выходу второго цифроаналогового преобразователя, а налоговый вход которого подключен к выходу второго блока суммирования, а - к выходу счётчика, информационный вход счетчика соединен с шиной задания интервала, управляющие входи счетчика и регистр соединены с шиной сброса, дополнительно содержит первыйи второй комб национные сумматоры, и подключенные к их выходам соответственно третий и четвёртый цифроаналоговые преобразоватёл й, выходы которых подключены к соответствующим BxoflaNi второго бло ка с у1Ж1ир6вания, пёрвый вхбй Первого комбинационного сумматора соединен с ByScogtoM nepBdro регистра, второй вход первого и первый вход второго комбинационных сумматоров оединёны т ыходрм второго регистра;, fiToipoiR вхо второго кбибй надйонМо гй суйкЙ Ше соединен с выходом третьез о регйстра а аналоговые входы третьего и четвер тог6 Циф-ро-аналоговых прёоёразователей соединены с регулировоч ншли- вхо дайй экстра1ПОЛятора. Hai чертеже изображена блбк-схёма предложенного экстраполятора. Экстраполятор содержит первый 1, второй 2 и третий 3 регистры, первый-4 и второй 5 комбинационные су1ЛМатр1ры, первый 6 и второй 7 цифро ана 1ог6выё пр ёобраз6ватели (ЦАП) первый блок 8 Суммирования, третий 9 и чёт1вертый 10 цифроаналоговые преобразователи, второй, бло„к 11 , , , суммирования, счетчик 12. При этом на схеме 13-1S - входы ординат фучкции, вход эк ёЧграполяцйй, 17 и 18 - регулировочные входы, 19 вход задания интервала.

-Л--:- - -- , .-.

gBf-y-o fr-j..-.

739559 Экстраполятор работает cлeдyЮщи, образом, В основу работы предлагаемрго устройства положен следующий алгоритм: nVm- .o- n-m к о-ид;/ х -к,-и,,и,,--и„, .S. и,,( в выражениях (1) - (5) приняты следующие обозначения: Х, Х и Х„ цифровые кбды ординат экстрапштируемой функции, причем Х,, соответствует моменту времени t на временной оси, п m моменту времени (t-m-at ) , а XQ - моменту времени i-n В общем случае координаты Х , и Х на равноотстоящие по времени, т. е. , хотя при т#п/2 выражения (1) - (5) не теряют силу. ojK,K весовыеКоэффициенты, значения которых определяются из следующих выражений: .1-«. ..+- . w+ г nU-mV (6) N vn(.n-no И-П1 1-Х-0 -2. , К Обозначения Ug Ц,( соответствуют аналоговым выходам соответствующих блоков экстраполятора, схема которого приведена на чертеже, tj - цифровой код. Пропорциональной времени экстраполяции и содержащийся в счетчике 12. В рабочем режиме очередным импульсом сброса, поступаквдим на вход 16, обнуляются счетчик 12 и регистры с одновременным приемом очередных кодов ордданат экс1 раполИруемой функции: через вход 13 - код Х„ , через вход 14 - код Xj, . и через вход 15 - код Х . По окончании переходных процессов на выходе преобразователя б устанавливается величина, пропорЦЙОнальная коду Х , а на выходе блока 11 величийа, пропорциональная приращению экстраполируемой функции (Xj, - Х) на интервале д1, причем коэффициент пропорциональности в обоих случаях одинаков. После этОгЬ через вход 19 от внетинего устройства в счетчик записывается величина интервала (t . На. выходе ЦАП 7 формируется величина AlJ, (см. вы1гажэн1}е 4) , которая изменяется в соответствии с законом . йзмейёййя величины f . Непрерывно й§1Йёняк 1цаяся величина Ug пропорциональна экстраполированному значению экстраполируемой функции, заданной циф13овЫШ1 кодами неравноотстоящих отсчётов X.. п 6 В момент достижения значения кода в счетчике 12 на вход 16 вновь поступает импульс конца интервала экстраполяции и Цикл работы экстраполятора повторяется. . Уменьшение флюктуационной ошибк достигается за счет того, что. разн ти ординат дХ имеют меньшую разря ность, чем сами ординаты, а .уменьшение разрядности ЦАП снижает уровень флюктуации . Уменьшение количе ва ЦАП на один по сравнению с изве:стным устройством 12 повышает точность работы экстраполятора. Эффект от применения предложенного экстраполятора связан с экономией оборудования и повышением точности работы. Формула изобретения Ступенчато-линейный экстраполятор, содержащий три регистра, входы которых соединены с соответствующими информационными входами экстраполятора, два блока, суммирования, счетчик и два цифроанало говых преобразователя пркчем выход первого регистра через первый цифроаналоговый преобразователь связан с первым входом первого бло ка суммирования, второй вход которого подключен в выходу второго цифроаналогового преобразователя, аналоговый вход которого подключен к ЬЫХОДУ второго блока суммирования, & цифровой вход - к выходу счетчика, информационный вХод счетчика соединен с шиной задания интервала, управляющие входы счетчика и регистра соединены с шиной сброса, отличающийся тем, что, с цепью упрощения и уменьшения флюктуационных ошибок, экстрапол ятор дополн1 тельно содержит первый и второй комбинационные сумматоры и подключенные к их выходам соответственно третий и четвертый циФ Iроаналоговые преобразователи, выходы которых йодключены к соответст-вуюЩим входам второго блока суммирования, первый вход первого комбинационного сумматора соединен с выходом первого регистра, второй вход . первого и первый вход второго комбинационных сумматоров соединены с выходом второго регистра, второй вход второго комбинационного, сумматора соединен с выходом третьего регистра, а аналоговые.входы третьего и четвертого цифроаналоговых преобраэоват,елей соединены с регулировочньвли входами экстраполятора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР №467368, кл. G 06 G 7/30, 1974. 2.Авторское свидетельство СССР по заявке 2493580/18-24, кл. G 06 G 7/30, 06.06.77 (прототип).

/Jo

« О

fS О

«о

Авторы

Даты

1980-06-05—Публикация

1977-06-29—Подача