(54) АНАЛОГОВОЕ ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое делительное устройство | 1979 |

|

SU834712A1 |

| Время-импульсное делительное устройство | 1977 |

|

SU721830A1 |

| Устройство для определения логарифма отношения двух сигналов | 1985 |

|

SU1357981A1 |

| Делительное устройство | 1978 |

|

SU748436A1 |

| Множительно-делительное устройство | 1976 |

|

SU610128A1 |

| Устройство для считывания изображений | 1984 |

|

SU1179394A1 |

| Устройство для деления аналоговых сигналов | 1978 |

|

SU752366A1 |

| Аналоговое делительное устройство | 1975 |

|

SU547780A1 |

| Устройство для определения моментов появления экстремумов | 1989 |

|

SU1661980A2 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПАРАМЕТРОВ ПОДКЛЮЧАЕМЫХ НА ПАРАЛЛЕЛЬНУЮ РАБОТУ ГЕНЕРАТОРОВ | 2014 |

|

RU2557672C1 |

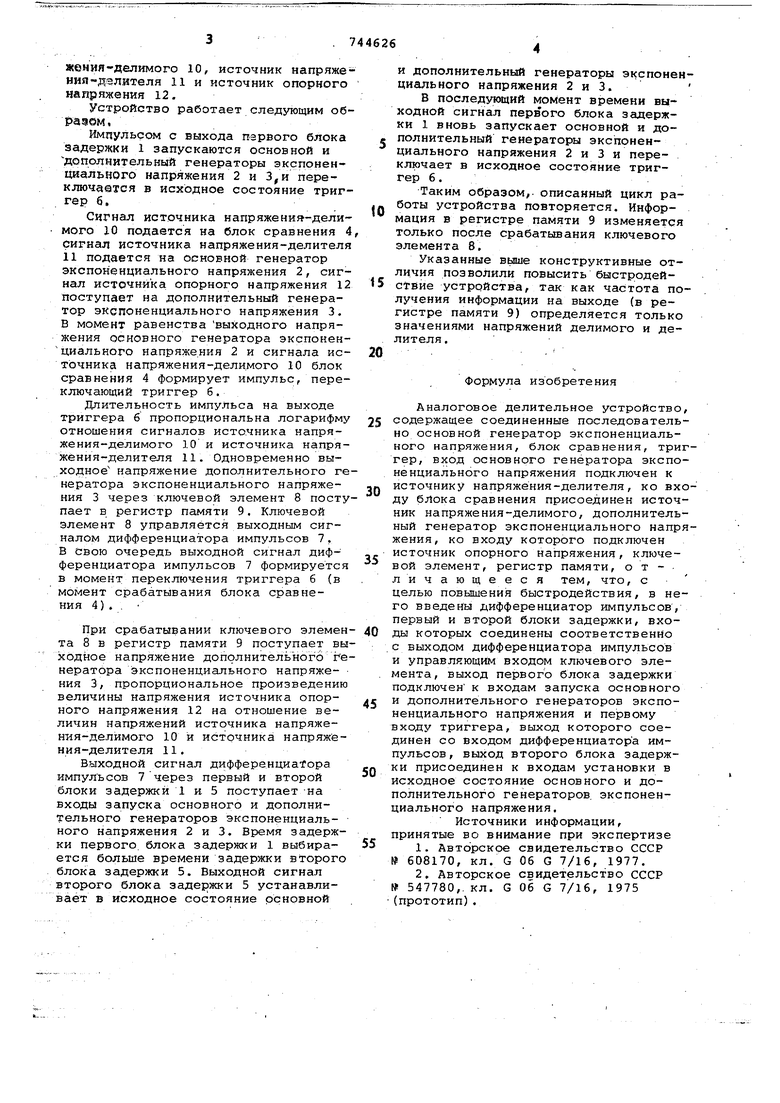

г Изобретение относится к области .электрических вычислительных устройств и может быть использовано в аналоговых вычислительных машинах. Однако из известных устройств для деления содержит блок сравнения, регистр памяти, блок управления 1. , Это устройство обладает сравни тельно низким быстродействием. Из известных устройств аналогично го назначения наиболее близким к пред ложенному является аналоговое делительное устройство,содержащее.соединенные последовательно основной генератор экспоненциального напряжения, б.ток сравнения, триггер, вход основного генератора экспоненциального напряжения подключен к источнику напрЯ1 жения-делителя, второй вход блока сравнения присоединен к источнику на пряжения-делимого, дополнительный генератор экспоненциального напряжения ко входу которого подключен источник опорного напряжения, ключевой элемено регистр пг1мяти 2 . Это устройство характеризуется низким быстродействием вследствие получения результатов деления с частотой, определяемой внешним запуском Целью изобретения является повышение быстродействия. Для достижения указанной цели в предлагаемое делительное устройство введены дифференциатор импульсов, первый и второй блоки задержки, входы которых соединены с выходом дифференциатора импульсов и управляющим входом ключевого элемента, выход первого блока задержки подключен к входам запуска основного и дополнительного генераторов экспоненциального напряжения и второму входу триггера, выход которого соединен со входом дифференциатора импульсов, выход второго блока задержки присоединен к входам установки в исходное состойние основного и дополнительного генераторов экспоненциального напряжения,. На чертеже показана функциональная схема предложенного устройства. Оно содержит первый блок задержки 1, основной и,дополнительный генераторы экспоненциального напряжения 2 и 3, блок сравнения 4, второй блок задержки 5, триггер 6, дифференциатор импульсов 7, ключевой элемент 8, регистр памяти 9, источник напряжения-делимого 10, источник напряже ния-дзлителя 11 и источник опорного напряжения 12. Устройство работает следующим об разом, Импульсном с выхода первого блока задержки 1 запускаются основной и дополнительный генераторы экспоненциального напряжения 2 и 3,и переключается в исходное состояние триг гер б. Сигнал источника напряжения-дели мого JO подается на блок сравнения сигнал источника напряжения-делител 11 подается на основной генератор экспоненциального напряжения 2, сиг нал источника опорного напряжения 1 поступает на дополнительный генератор экспоненциального напряжения 3. В момент равенства выходного напряжения основного генератора экспонен циального напряжения 2 и сигнала ис точника напряжения-делимого 10 блок сравнения 4 формирует импульс, пере ключающий триггер б. Длительность импульса на выходе триггера б пропорциональна логарифм отношения сигналов источника напряжения-делимого 10 и источника напряжения-делителя 11. Одновременно выходное напряжение дополнительного ге нератора экспоненциального напряжения 3 через ключевой элемент 8 посту пает в регистр памяти 9. Ключевой элемент 8 управляется выходным сигналом дифференциатора импульсов 7, В свою очередь выходной сигнал дифференциатора импульсов 7 формируется в момент переключения триггера б (в момент срабатывания блока сравнения 4) . . При срабатывании ключевого элемен та 8 в регистр памяти 9 поступает вы ходное напряжение дополнительного ге нератора экспоненциального напряжения 3, пропорциональное произведению величины напряжения источника опорного напряжения 12 на отношение величин напряжений источника напряжения-делимого 10 и источника напряжения-делителя 11. Выходной сигнал дифференциатора импульсов 7 через первый и второй блоки задержки 1 и 5 поступает-на входы запуска основного и дополнительного генераторов экспоненциального напряжения 2 и 3. Время задержки первого, блока задержки 1 выбирается больше времени задержки второго блока задержки 5, Выходной сигнал второго блока задегэжки 5 устанавливает в исходное состояние основной и дополнительный генераторы экспоненциального напряжения 2 и 3. В последующий момент времени выходной сигнал первого блока задержки 1 вновь запускает основной и дополнительный генераторы экспоненциального напряжения 2 и 3 и переключает в исходное состояние триггер 6.. Таким образом,- описанный цикл работы устройства повторяется. Информация в регистре памяти 9 изменяется только после срабатывания ключевого элемента 8. Указанные вьпие конструктивные отличия позволили повысить быстродейctBHe устройства, так как частота получения информации на выходе (в регистре памяти 9) определяется только значениями напряжений делимого и делителя. Формула изобретения Аналоговое делительное устройство, содержащее соединенные последовательно основной генератор экспоненциального напряжения, блок сравнения, триггер, вход основного генератора экспоненциального напряжения подключен к источнику напряжения-делителя, ко входу блока сравнения присоединен источник напряжения-делимого, дополнительный генератор экспоненциального напряжения, ко входу которого подключен источник опорного напряжения, ключевой элемент, регистр памяти, о т - л и чающееся тем, что, с целью повышения быстродействия, в него введены дифференциатор импульсов, первый и второй блоки задержки, входы которых соединены соответственно с выходом дифференциатора импульсов и управляющим входом ключевого элемента, выход первого блока задержки подключен к входам запуска основного и дополнительного генераторов экспоненциального напряжения и первому входу триггера, выход которого соединен со входом дифференциатора импульсов, выход второго блока задержки присоединен к входам установки в исходное состояние основного и дополнительного генераторов, экспоненциального напряжения. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 608170, кл. G Об G 7/16, 1977. 2,Авторское свидетельство СССР № 547780,. кл. G Об G 7/16, 1975 (прототип).

Авторы

Даты

1980-06-30—Публикация

1978-02-06—Подача