1

Изобретение относится к автоматике энергосистем и может быть использовано, например, для автоматического синхронного включения генераторов или энергосистем на параллельную работу с постоянным временем опережения.

Известны устройства для автоматической синхронизации с достоянным временем опережения, содержащие блоки выделения огибающей напряжения биений и ее первой производной по времени у., 2. .

Недостатком известных устройств является погрешность синхронизации увеличении частоты скольжения.

Наиболее бл азким к предложенному устройству по технической сущности является устройсгбо для автоматической синхронизации ЗЭто устройство содержит блок вьщеления огибающей напряжения биений, дифференцирующий блок, блок разности синзфоннаируемых напряжений, блок запрета, логическую схему И и .блок временя опережения. В устройстве выход дифференцирующего блока, блока вьзделвния огибакнцей напряжения биений и выход блока разности натфяженнй :дацоврвмё но подключены к суммирующим входам блока времени опережения, выход которого подключен к одному из входов логической схемы И, другой вход котор Л подключен к выходу блока за1фвта.

Это устройство имеет ряа недостат10ков, ограничивающих его примевенве. К ним относятся:

1. Время опережения определяется на основании допущения, что

15

t

где круговая, частота огибаю1цей напряжения биений (частота скольжения);

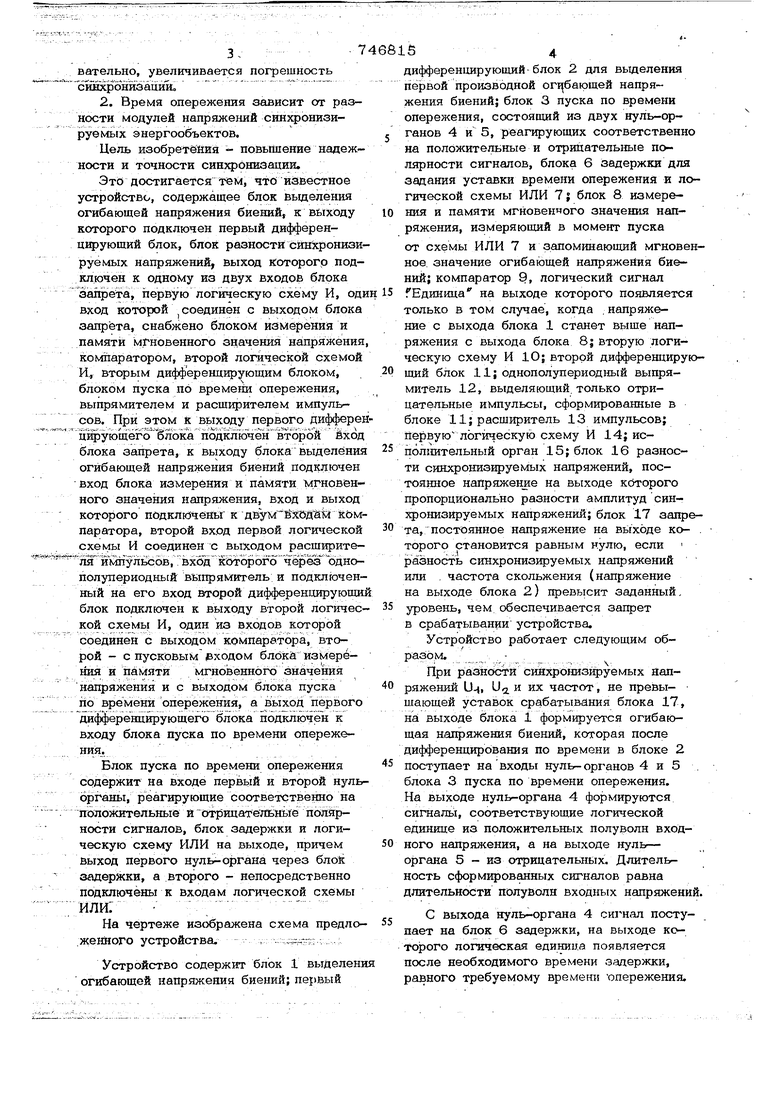

20 fcoj,- время опережения. Отсюда видно, что с увеличением частоты скольжения (О снижается корректность приведенного допуй1ення н, следовательно, увеличивается погрешность сйнхрбнйэациии, 2. Время опережения зависит от разности модулей напряжений синхронизируемых энергообъектов. Цель изобретения - повышение надежности и точности синхронизации. Это достигается тем, что известное устройство, содержащее блок выделения огибающей напряжения биений, к выходу которого подключен первый дифференцирующий блок, блок разности синхронизи руемых напряжений, выход которого подключен к одному из двух входов блока запрета, первую логическую схему И, од вход которой I соединен с выходом блока запрета, снабжено блоком измерения и памяти мгновенного значения напряжения компаратором, второй логической схемой И., вторым дифференцирующим блоком, блоком пуска пО времени опережения, выпрямителем и расширителем импульсов. При этом к вьгходу nejpBoro диффере Ц1фующёг6 6пока подкл(6чён второй ёход блока запрета, к выходу блока выделения огибающей напряжения биений подключен вход блока измерения и памяти мгновенного значения напряжения, вход и выход которого подклйченьг к двум ёхТ5дШ ком паратора, второй вход первой логической схемы И соединен с выходом расширите ля ймпульсов, вход кБторогб через Шнополупериодный выпрямитель и подключенный на его вход второй дифференцирующи блок подключен к выходу второй логической схемы И, один из входов которой соединен с выходом компаратора, второй - спусковым РХОДОМ блОкй измерения и памяти мгновенного значения напряжения и с выходом блока пуска по времени опережения, а выход первого дифференцирующего блока подключен к входу блока пуска по времени опережения. Блок пуска по времени опережения содержит на входе первый и второй нульорганы, реагирующие соответственно на положительные и отрицатежние полйрности сигналов, блок задержки и логическую схему ИЛИ на выходе, причем выход первого нуль-органа через блок задержки, а второго - непосредственно подключены к входам логической схемы На чертеже изображена схема предложенного устройства., . , . Устройство содержнгг блок 1 выделени огибающей напряжения биений; первый 7 54 дифференцирующий-блок 2 для вьщеления первой производной оп бающей напряжения биений; блок 3 пуска по времени опережения, состоящий из двух нуль-органов 4 и 5, реагирующих соответственно на положительные и отрицательные полярности сигналов, блока 6 задержки для задания уставки времени опережения и логической схемы ИЛИ 7; блок 8 измерения и памяти мгновенного значения напряжения, измеряющий в момеиг пуска от схемы ИЛИ 7 и запоминающий мгновенное, значение огибающей напряжения биений; компаратор 9, логический сигнал fЕдиница на выходе которого появляется только в том случае, когда . напряжение с выхода блока 1 станет выше напряжения с выхода блока 8| вторую логическую схему И 10; второй дифференцирующий блок 11; однополупериодный выпрямитель 12, выделяющий, только отрицательные импульсы, сформированные в блоке 11; расширитель 13 импульсов; первую логическую схему И 14; исполнительный орган 15; блок 16 разности синхронизируемых напряжений, постоянное напряжение на выходе которого пропорционально разности амплитуд синхронизируемых напряжений; блок 17 захфе- та, г постоянное напряжение на выходе ко- . торого становится равным нулю, если разность синхронизируемых напряжений или , частота скольжения (напряжение на выходе блока 2) превысит заданный, уровень, чем обеспечивается запрет в срабатывании устройства. Устройство работает следующим образОм., - , При разности синхронизируемых Напряжений UH, (Ji2. и их частот, не преВы- шающей уставок срабатывания блока 17, на выходе блока 1 формируется огибающая напряжения биений, которая после дифференцирования по времени в блоке 2 поступает на входы нуль-органов 4 и 5 блока 3 пуска по времени опережения. На выходе нуль-органа 4 формируются сигналы, соответствующие логической единице из положительных полуволн входного напряжения, а на выходе нуль- органа 5 - из отрицательных. Длительность сформированных сигналов равна длительности полуволн входных напряжений. С выхода нуль-органа 4 сигнал поступает на блок 6 задержки, на выходе коTojporo логическая единица появляется после необходимого времени .задержки, равного требуемому времени опережения. На выходе логической схемы ИЛИ 7 формируется единичный сигнал, длительность которого равна ( Тс t-or, )i где Т - длительность периода биений; tpff время опережения. Этот сигнал поступает на пусковой вход блока 8 измерения и памяти мгновенного значейия напряжения биений. До момента поступления сигнала от схемы ИЛИ 7 блок 8 работает как обычный масштабный усилитель. Сигналом от схемы ИЛИ 7 в блок 8 включается орган памяти и отделяется входная цепь. На выходе компаратора 9 после появления сигнала от схемы ИЛИ 7, т.е. в момент, когда кривая напряжения &f блока 1 превысит уровень сигнала от блока 8, появится логическая единица. Длительность этого сигнала равна Тс, 2bQfj. Сигнал с выхода компаратора 9 поступает во вторую логическую схему И 10, единичный сигнал на выходе которой существует в течение Т -2 -t on от момента появления сигнала с компаратора 9. Схема И 1О необходима для того, чтобы при отсутствии скольжения, когда сигнала от схемы ИЛИ 7 нет, .не происходило срабатывания устройства. .Затем сигнал с выхода схемы И 10 дифференцируется, в блок 11, на выходе которого появляются узкие импульсы положительной по.п ярности в момент появле ния сигнала на выходе схемы 10 и отрицательной - в момент его окончания. Сйнополупериодным выпрямителем 12 вы деляются только отрицательные импульсы соответствующие моменту времени, в ко торый должен подаваться сигнал на исполнительный орган. 15 и далее на управ ление выключателем с учетом требуемог времени опережения. Сигнал с выхода выпрямителя 12 расш ряетйя в расширителе 13 импульсов по длительности до значения, равного ,, и поступает через логическую схему 14 совпадения на исполнительный орган-. 15 Если разность синхронизируемых напряжений с выхода блока 16 или разност частот этих напряжений, пропорциональная напряжению, с выхода блока 2, прев шает уставки срабатывания блока 17 запрета, на его выходе появляется логический нуль, который поступает на второй вход схемы совпадения, запрещая срабатывание устройства в целом. Использование предлагаемого устройства для автоматической, синхронизации обеспечивает по сравнению с известными устройствами следующие преимущества: возможность получения стабильного емени опережения включения выклЕочателя, не зависящего в широких пределах от частоты скольжения и отнсинения синзфониз уемых наЗпряжений; более высокую точность сии}фоиизации;независимость точности сишфоннзации от угла опфежения, определяемого временем опережения. Это позволяет значительно расщирить область применения автоматической син;фонизации как для включения энергообъектов на параллельную работу, так и для .отключения.асинхронного хода. В результате снижается время синхронизации или отключения асинхронного хода, что повьппает устойчивость работы энергосистем и отдельных энергообъектов, а также повьппает срок службы электроэнергетического оборудования., Формула изобретения 1. Устройство для автоматической си хронизации, содержащее блок выделения огибающей напряжения биений, к выходу которого подключен первый дифферен-. цируюший блок, блок разности синхронизируемых напряжений, выход котфого подключен к одному из двух .входов блока запрета, первую логическую схему И, один вход которой соединен с выходом блока запрета, отличающеес я тёй, что, С цё йБйИОКьМёййя надежности и точности синхронизации; устройство снабжено блоком измерения и памяти мгновенного значения напряжения, компаратором, второй :логической схемой И, вторым дифференцирующим блоком, блоком цуска по времени опер1ежения выпрямителем и расщирителем импульсов, причем к выходу первого дифференцирующего блока подключен второй вход блока запрета, к выходу блока вьщелевшя огибающей наНрясжения биений подключен вход блока измерения и памяти мгновенного значения напряжения, выход и вход которого подключены к двум входам компаратора, второй вход первой логической схемы И соединен с выходом рааиирителя импульсов, вход которого через однополупериодный выпрямитель и подключенный на его вход второй дифференцирующий блок подключен к выходу второй логической схемы И, один из входов которой соединен с выходом компаратора, второй - с выходом блока пуо 1Гй ЙЬ врейвнй опёрёзкения и с пусковым входом блока измерения и памяти мгновенного напряжения, а выход первого дифференцирующего блока под ключен к входу блока пуска по времени опережения.

2. Устройство до ш 1, отличающееся тем, что, блок пуска пЬ времени оп ёженнд содержит, не входе первый и второй нуль-органы, реагирующие соответственно на положительные и отрицательные полярности сигналов, блок задержки в логическую

схему ИЛИ на выходе, прячем выход пвого нуль-органа через блок задержки, а - непосоедстВенно подключены к входам логической схемы ИЛИ.

Источники информации, принятые ВО. внимание при эксп(ртизе

1.Авторское свидетельство СССР № 126937 кл. Н 02 Та/42, 1959.

2.Айторское свидетельствб СССР 486419, кл. Н 02 J 3/42, 1973.

3.Авторское свидетельство СССР № 488282, кл. Н 02 J 3/42, 1972,

4.Автбрсков свидетельство СССР N9 471637, кл. Н 02 Тз/42, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отключения электрической цепи при нарушении синхронизма между двумя частями энергосистемы | 1981 |

|

SU983890A1 |

| Устройство для отключения электри-чЕСКОй цЕпи пРи НАРушЕНии СиНХРОНиз-MA МЕжду дВуМя чАСТяМи эНЕРгОСиСТЕМы | 1979 |

|

SU811403A1 |

| Устройство для отключения электрической цепи при нарушении синхронизма между двумя частями энергосистемы | 1980 |

|

SU907693A2 |

| Устройство для синхронизации генераторов | 1971 |

|

SU471637A1 |

| Устройство для точной автоматической синхронизации | 1972 |

|

SU488282A1 |

| Устройство для точной автоматической синхронизации | 1985 |

|

SU1330702A2 |

| Автоматический синхронизатор с постоянным временем опережения | 1979 |

|

SU888269A2 |

| Устройство точной синхронизации | 1987 |

|

SU1561145A1 |

| Автоматический синхронизатор с постоянным временем опережения | 1977 |

|

SU705597A1 |

| Автоматический синхронизатор с постоянным временем опережения | 1961 |

|

SU146838A1 |

-;-- ...-;- .-V

Авторы

Даты

1980-07-05—Публикация

1978-03-28—Подача