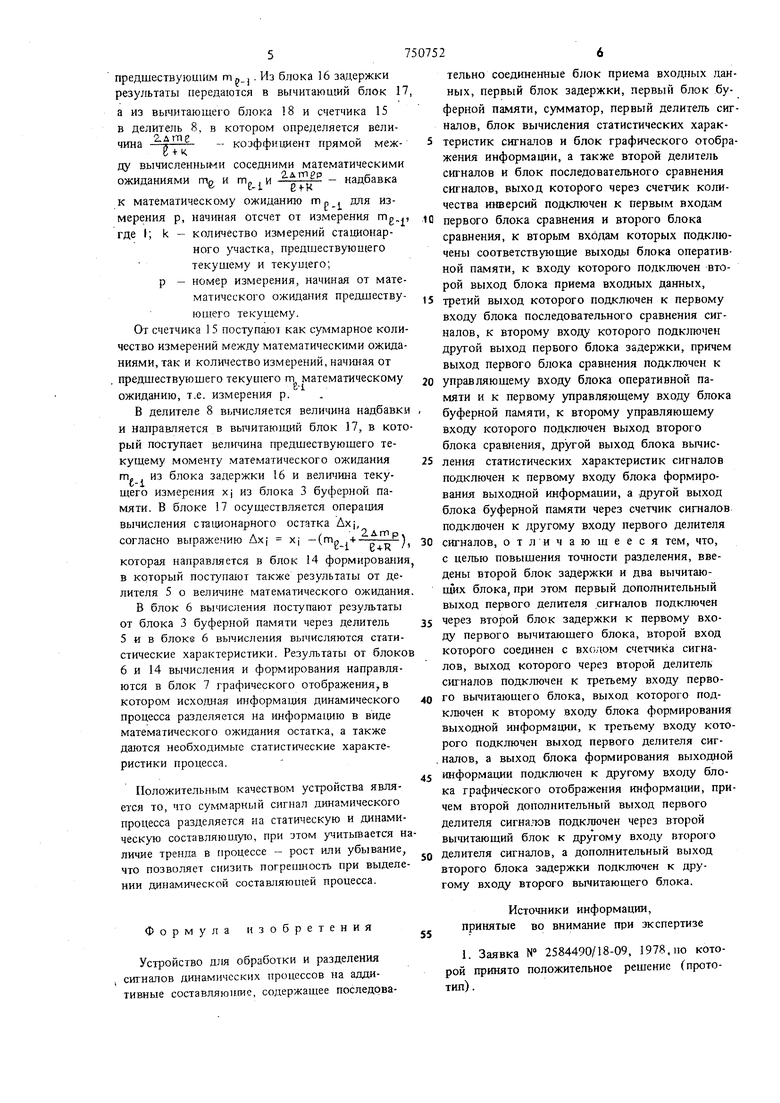

(54) УСТРОЙСТВО ДЛЯ ОБРАБОТКИ И РАЗДЕЛЕНИЯ СИГНАЛОВ ДИНАМИЧЕСКИХ ПРОЦЕССОВ Изобретение относится к радиотехнике и может использоваться для обработки больших потоков информации. Известно устройство для обработки и разделения сигналов динамических процессов на адд тивные составляющие, содержащее последовател но соединенные блок приема входных дшшых, первый блок задержки, первый блок буферной памяти, сумматор, первый делитель сигналов, блок вычисления -статистических характеристик сигналов и блок графического отображения информации, а также второй делитель сигналов и блок последовательного сравнения сигналов, выход которого через счетчик количества инверсий подключен к первым входам первого блока сравнения и второго блока сравнення, к вторым входам которых подключены соответствующие выходы блока оперативной памяти, к входу которого подключен второй выход блока приема входных данных, третий выход которого подключен к первому входу блока последовательного сравнения сигналов, к второму входу которого подключен другой выход первого блока задержки, причем выход первого блока сравнения подключен к управляющему входу блока оперативной памяти Я. к первому управляющему входу блока буферной памяти, к второму управляющему входу которого подключен выход второго блока сравнения, другой выход блока вьпшсления статистических характеристик сигналов подключен к первому входу блока формирования выходной информации, а другой выход блока буферной памяти через счетчик сигналов подключен к другому входу первого делителя сигналов 1. Однако известное устройство не обеспечивает достаточной точности разделения сигналов. Цель изобретения - повыщеиие точности разделения. Для этого в устройство для обработки и разделения сигналов динамических прюцессов на аддитивные составляющие, содержащее последовательно соединенные блок приема входных данных, первый блок задержки, первый блок буферной памяти, сумматор, первый делитель сигналов, блок вычисления статистических характеристик сигналов и блок графичес37кого отображения информации, а также второй делитель сигналов и блок последовательного сравнения сигналов, выход которого через счетчик количества инверсий подключен к первым входам первого блока .сравнения и второго блока сравнения, к вторым входам которых подключены соответствующие выходы блока оперативной памяти, к входу которого подключен второй выход блока приема входных данных, третий выход которого подключен к первому входу блока последовательного сравнения сигналов, к второму входу которого под ключен другой выход первого блока задержки, причем выход первого блока сравнения подключен к управляющему входу блока оператив ной памяти и к первому управляющему входу блока буферной памяти, к второму управляющему входу которого подключен выход второго блока сравнения, другой выход блока вычисления статистических характеристик сигна лов подключен к первому входу блока формирования выходной информации, а другой . выход блока буферной памяти через счетчик сигналов подключен к другому входу первого делителя сигналов, введены второй блок задержки и два вычитающих блока, при этом первый дополнительный выход первого делителя сигналов подключен через второй блок задержки к первому входу первого вычитающего блока, второй вход которого соединен с входом счетчика сигналов, выход которого через второй делитель сигналов подключен к третьему входу первого вычитающего блока выход которого подключен к второму входу блока формирования выходной информации, к третьему входу которого подключен вьь ход первого делителя сигналов, а выход блока формирования выходной информации подключен к другому входу блока графического отображения информации, причем второй дополнительный выход первого делителя сигналов подключен через второй вычитающий блок к другому входу второго делителя сигналов, а дополнительный выход второго блока задержки подключен к другому входу второго вычитающего блока. На чертеже приведена структурная электрическая схема предложенного устройства. Устройство для обработки и разделения си налов динамических процессов содержит блок 1 приема входных данных, блок 2 задержки, блок 3 буферной памяти, сумматор 4, делите 5 сигналов, блок 6 вычисления статистических характеристик сигналов, блок 7 графического отображения информации, делитель 8 сигналов, блок 9 последовательного сравнения сигн лов, счетчик Ш количества инверсий, блоки 10 и 11 сравнения блок 13 оперативной пам блок 14 формирования выходной информации четчик 15 сигналов, блок 16 задержки, два ычитающих блока 17 и 18. Устройство работает следующим образом. Из блока 1 приема результаты измерения XJ поступают в блок 2 задержки, где они задерживаются на время дескретизаиии At и в блок 9 последовательного сравнения, в который поступают результаты, задержанные в блоке 2 задержки. Блок задержки 2 пропускает результаты в блок 3 буферной памяти. В блоке 9 последовательного сравнения последовательно сравниваются измерения текущие со всеми предществую.щими и формируется инверсия Ti . Каждое измерение, получивщее оценку инверсии, равную 1, пропускается в счетчик 10 количества инверсий (для текущего измерения). Результаты из счетчика 10 пропускаются в два блока 11 и 12 сравнения, в которые поступают результаты из блока 13 оперативной памяти. Блок 13 оперативной памяти связан с блоком 1 приема. В блоке 13 оперативной памяти содержатся вставки о величинах допустимого количества инверсий для текущего измерения; ; ТминВ блоке 11 сравнения сравнивается текущее количество инверсий Tj. с максимальным Тмакс поступивщим из блока 13 оперативной памяти, а в блоке 12 сравнения - с минимальным TMHH- Если в результате сравнения Tj будет больще меньше то будет сформирован сигнал Ci или 2. Появление сигнала С или €2 свидетельствует о конце интервала стационарности для заданного диапазона инверсий интервала стационарности. Сигналы С или €2 направляются в блок 3 буферной памяти. В блоке 3 буферной памяти по зтим сигналам открывается память от момента поступления сигнала, и все запоминаемые между сигналами измерения, т.е. измерения продолжительностью стационарного участка передаются в сумматор 4, где они суммируются и передаются в делитель 5, в котором вычисляется величина математического ожидания стационарного участка по информации от сумматора 4 и счетчика 15 о количестве измерений на участке стационарности. В делителе 5 осуществляется операция деления результата от сумматора 4 на результат от счетчика 15 и определяется величина математического ожидания стационарного участка. Этот результат для текущего математического ожидания mg направляется в блок 16 задержки, где задерживается на время в вьпштающий блок 1Я, в котором определяется разность текущего математического ожидания Дт с предшествующим - Из блока 16 задержки результаты передаются в вычитающий блок 17 а из вычитающего блока 18 и счетчика 15 в делитель 8, в котором определяется велич™а коэффициент прямой между вычисленными соседними математическими ожиданиями mg и trip .и надбавка к математическому ожиданию тр., для измерения р, начиная отсчет от измерения mg, где I; k - количество измерений стадаонарного участка, предшествующего текущему и текущего, р - номер измерения, начиная от математического ожидания предшествующего текущему. От счетчика 15 поступают как суммарное количество измерений между математическими ожвданиями, так и количество измерений, начиная от предществующего текущего m математическому ожиданию, т.е. измерения р. В делителе 8 вьиисляется величина надбавки и налравляется в вычитающий блок 17, в кото рый поступает величина предществующего текущему моменту математического ожидания т, из блока задержки 16 и велтина текущего измерения xj из блока 3 буферной памяти. В блоке 17 осуществляется операция вычисления стационарного остатка Axj, согласно выражению Лх; Х| -(), которая направ; яется в блок 14 формирования в который поступают также результаты от делителя 5 о величине математического ожидания В блок 6 вычисления поступают результаты от блока 3 буферной памяти через делитель 5и в блоке 6 вычисления вычисляются статистические характеристики. Резул1)таты от блоков 6и 14 вычисления и формирования направляются в блок 7 графического отображения, в котором исходная информатлдя динамического процесса разделяется на информацию в виде математического ожидания остатка, а также даются необходимые статистические характеристики процесса. Положительным качеством устройства является то, что суммарный сигнал динамического процесса разделяется на статическую и динамическую составляющую, при этом учитывается на личие тренда в процессе рост или убывание, что позволяет снизить погреишость при выделении динамической составляющей процесса.

Формула изобретения

Устройство д;ю обработки и разделения сигналов динамических процессов на аддитивные составляющие, содержащее последова ZAlTip,

Источники информации, принятые во внимание при экспертизе

1. Заявка № 2584490/18-09, 1978.no которой принято положительное решение (прототип). тельно соединенные блок приема вхо;1лых данных, первый блок задержки, первый блок буферной памяти, сумматор, первый делитель сигналов, блок вычисления статистических характеристик сигналов и блок графического отображения информации, а также второй делитель сигналов и блок последовательного сравнения сигналов, выход которого через счегчик количества инверсий подключен к первым входам первого блока сравнения и второго блока сравнения, к вторым входам которых подклю, соответствующие выходы блока оператив памяти, к входу которого подключен второй выход блока приема входных данных, третий выход которого подключен к первому входу блока последовательного сравнения сигналов, к второму входу которого подюпочен другой выход первого блока задержки, причем выход первого блока сравнения подключен к управляющему входу блока оперативной памяти и к первому управляющему входу блока буферной памяти, к второму управляющему входу которого подключен выход второго блока сравнения, другой выход блока вычисления статистических характеристик сигналов подключен к первому входу блока формирования выходной информации, а другой выход блока буферной памяти через счетчик сигналов подключен к другому входу первого делителя сигналов, отличающееся тем, что, с целью повышения точности разделения, введены второй блок задержки и два вычитаюЦЦ1Х блока, при этом первый допо.ггнительный выход первого делителя сигналов подключен через второй блок задержки к первому входу первого вычитающего блока, второй вход которого соединен с входом счетчика сигналов, выход которого через второй делитель сигналов подк;иочен к третьему входу первого вычитающего блока, выход которого подключен к второму входу блока формирования выходной информации, к третьему входу которого подключен выход первого делителя сигналов, а выход блока формирования выходной информации подключен к другому входу блока графического отображения информации, при второй дополнительный выход первого делителя сигналов подключен через второй выштающий блок к другому входу второго делителя сигналов, а дополнительный выход второго блока задержки подключен к другому входу второго Вычитающего блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки и сокращения избыточности данных измерений | 1978 |

|

SU750751A1 |

| Устройство для приема и выделения стационарных и нестационарных участков процессов | 1978 |

|

SU748482A1 |

| Устройство для анализа результатов измерений | 1981 |

|

SU1003363A2 |

| Устройство для выделения стационарной и нестационарной составляющих сигнала воспроизведения | 1984 |

|

SU1171723A2 |

| Устройство для выделения стационарной и нестационарной составляющих сигнала воспроизведения | 1990 |

|

SU1748083A2 |

| Устройство для анализа результатов измерений | 1977 |

|

SU732958A1 |

| Устройство для выделения стационарной и нестационарной составляющих сигнала воспроизведения | 1986 |

|

SU1337803A2 |

| Устройство для оценки достоверности результатов измерений | 1981 |

|

SU970428A2 |

| Статистический анализатор | 1981 |

|

SU1003096A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ ОБРАБОТКИ И СОКРАЩЕНИЯ ИЗБЫТОЧНОСТИ ДАННЫХ ИЗМЕРЕНИЙ | 2004 |

|

RU2271033C1 |

Авторы

Даты

1980-07-23—Публикация

1978-03-17—Подача