;54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ФАЗИРОВАНИЯ ФАКСИМИЛЬНОГО

АППАРАТА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля фазирования факсимильного аппарата | 1976 |

|

SU624380A1 |

| Устройство контроля фазированияпЕРЕдАющЕгО и пРиЕМНОгО фАКСиМиль-НыХ АппАРАТОВ | 1979 |

|

SU832767A2 |

| Устройство двухступенчатого автоматического фазирования факсимильного аппарата | 1984 |

|

SU1238265A2 |

| Устройство для автоматического выбора скорости приемного факсимильного аппарата | 1981 |

|

SU995370A1 |

| Устройство для измерения частоты в каналах радиоприемника | 1980 |

|

SU953582A1 |

| Устройство обработки информации | 1989 |

|

SU1817255A1 |

| Устройство двухступенчатого автоматического фазирования факсимильного аппарата | 1972 |

|

SU450383A1 |

| Устройство для фазирования факсимиль-НОгО АппАРАТА | 1979 |

|

SU849536A1 |

| Устройство контроля регенераторов линейного тракта систем связи с импульсно-кодовой модуляцией | 1980 |

|

SU907826A2 |

| Способ централизованного контроля телетрафика и состояния оборудования автоматической телефонной станции и система для его осуществления | 1979 |

|

SU902307A1 |

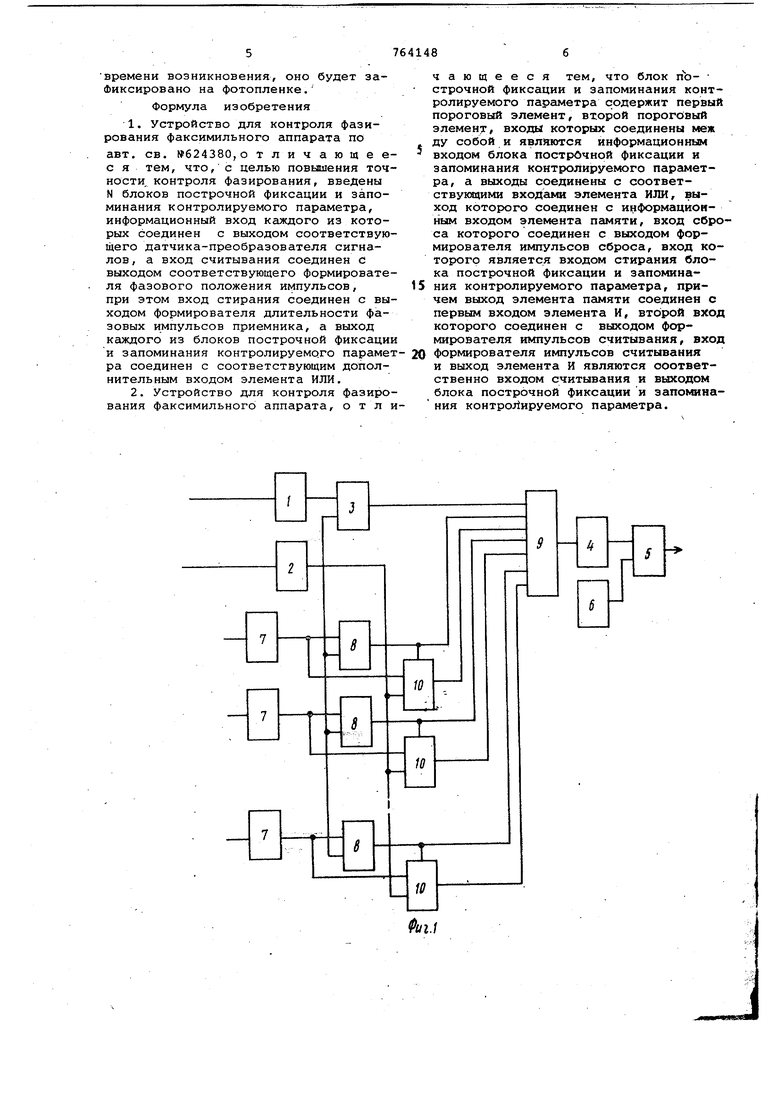

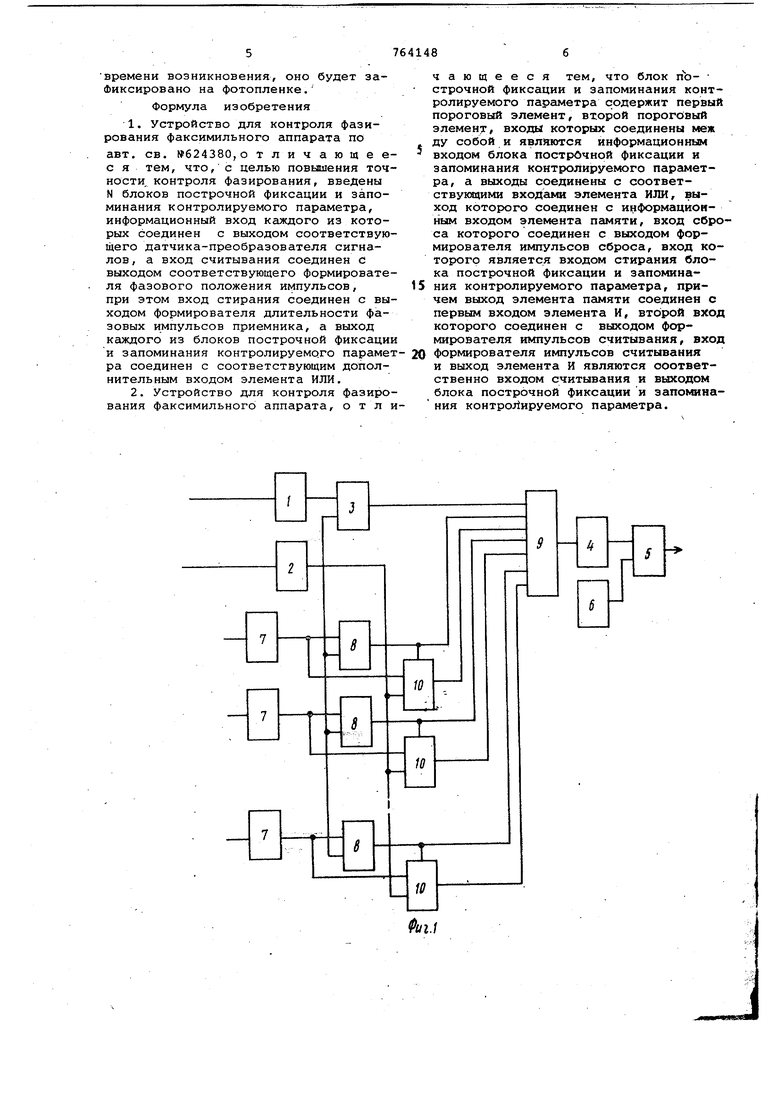

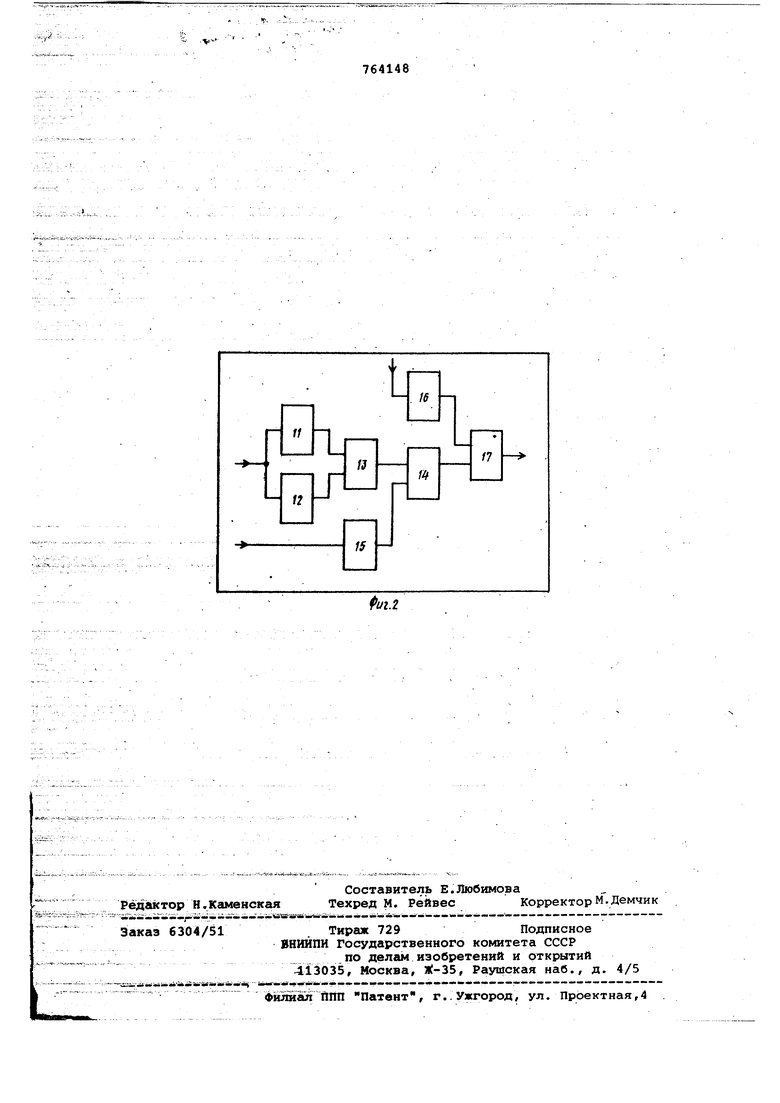

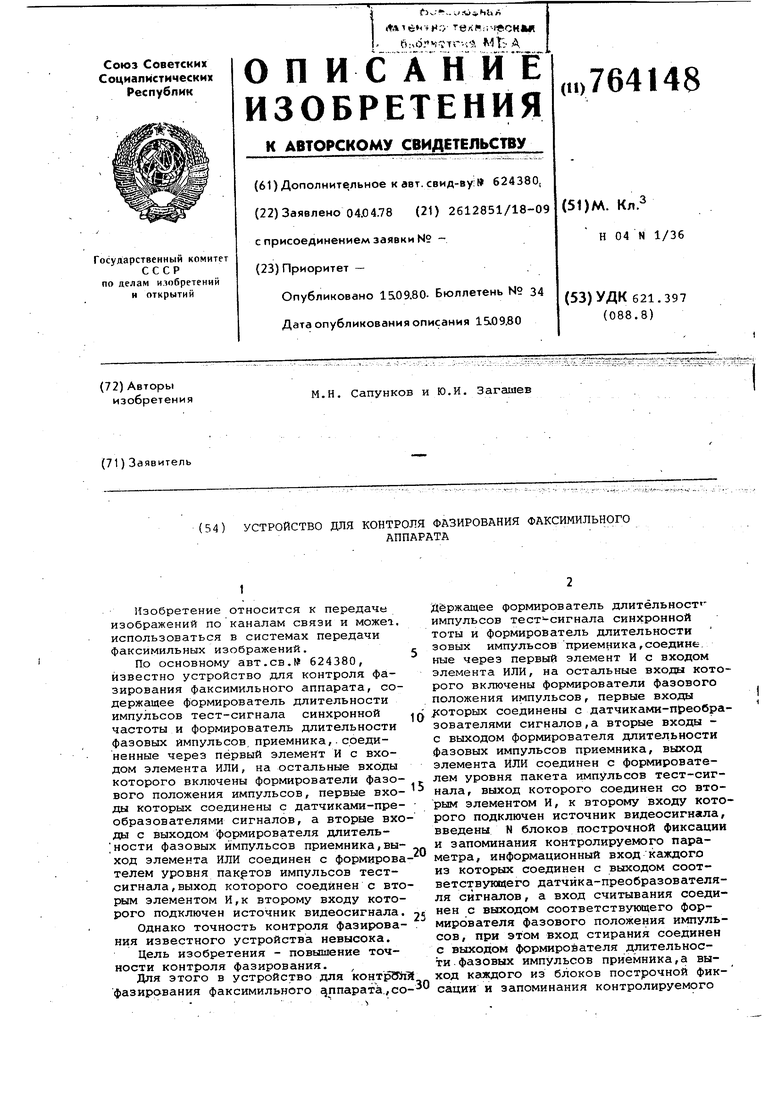

Изобретение относится к передаче изображений по каналам связи и можег. использоваться в системах передачи факсимильных изображений. По основному авт.св.№ 624380, известно устройство для контроля фазирования факсимильного аппарата, содержащее формирователь .длительности импульсов тест-сигнала синхронной частоты и формирователь длительности фазовых импульсов приемника,.соединенные через первый элемент И с входом элемента ИЛИ, на остальные вхбды которого включены формирователи фазового положения импульсов, первые входы которых соединены с датчикс1ми-преобразователями сигналов, а вторые вхо ды с выходом формирователя длитель;ности фазовых импульсов приемника,выход элемента ИЛИ соединен с формирова телем уровня пакетов импульсов тестсигнала , выход которого соединен с вто рым элементом И,к второму входу которого подключен источник видеосигнала. Однако точность контроля фазирования известного устройства невысока. Цель изобретения - повышение точности контроля фазирования. Для этого в устройство для KOHTp Jiia фазирования факсимильного ппарата.,со Держащее формирователь длитёльностимпульсов тест-сигнала синхронной тоты и формирователь длительности зовых импульсов приемника,соедине, ные через первый элемент И с входом элемента ИЛИ, на остальные входы которого включены формирователи фазового положения импульсов, первые входы jcoTopHX соединены с датчиками-преобразователями сигналов,а вторые входы с выходом формирователя длительности фазовых импульсов приемника, выход элемента ИЛИ соединен с формирователем уровня пакета импульсов тест-сигнала, выход которого соединен со вторым элементом И, к второму входу которого подключен источник видеосигнала, введены N блоков построчной фиксации и запоминания контролируе1лого параметра, информационный входкаждого из которых соединен с выходом соответствующего датчика-преобразователяля сигналов, а вход считывания соединен с выходом соответствующего формирователя фазового положения импульсов, при этом вход стирания соединен с выходом формиройателя длительности, фазовых импульсов приемника,а выход каждого из блоков построчной фиксации и запоминания контролируемого параметра соединен с соответствутбщим дополнительным входом элемента ИЛИ, при этом блокпострочной фик сации и запоминания контролируемого параметра содержит первый пороговый элемент, второй порюговый элемент, входы которых соединены между собой и являются информационном входом блока построчной фиксации и запоминания контролируемого параметра, а выходы соединены с соответствующи ми входами элемента ИЛИ, выход которого соединен с информационным входо элемента памяти, вход сброса которо соединен с выходом формирователя им пульсов сброса, вход которого являет ся зходом стирания блока пбстрЬчнЪй фиксации и запоминания контролируемо го параметра, причем выход элемента памяти соединен с первым входом элемента И, второй вход которого сое динен с выходом формирователя импуль сов считывания, вход формирователя импульсов считывания и выход элемента И являются соответственно входом считывания и выходом блока постр ной фиксации и запоминания контроли руемого параметра. На фиг. 1 представлена структурна электрическая схема предложенного устройства; на фиг. 2 - то же, блока построчной фиксации и запоминания контролируемого параметра. Предложенное устройство содержит формирователь 1 длительности импульсов тест-сигнала синхронной частоты формирователь 2 длительности фазовых импульсов приемника, первый элемент И 3, формирователь 4 уровня пакетов импульсов тест-сигнала, второй элемент И 5, источник видеосигнала 6, датЧйки-преобразователи 7 сигналов, формирователи 8 фазового положения импульсов, элемент ИЛИ 9 и блоки 10 построчной фиксации и запоминания контролируемого параметра, при этом блок 10 построчной фиксации и запоминания контролируемого параметра содержит первый и второй пороговые элементы 11, 12, элемент ИЛИ 13, эле мент памяти 14, формирователь 15 импульсов сброса, формирователь 16 импульсов считывания, элемент И 17. Устройство для контроля фазирования фиксимильного аппарата работает следующим образом. Если контролируемые сигналы не из меняют «своих параметров, на выходе соответствующих датчиков-преобразова телей 7 образуется постоянное напряжение , которое подается на формирова тели 8. На выходах формирователей 8 образуются импульсы, фазовое положение которых равномерно распределено по отношению к первому импульсу синх ронной частоты, выделяемому формирователем 2 и первым элементом И 3. Импульсы с формирователей 8 поступают на п входов элемента ИЛИ 9, а на его п+1 вход поступает импульс тест-сигнала синхронной частоты. На дополнительные входы элемента ИЛИ 9 сигналы не поступают;, поскольку первый и второй пороговые элементы 11, 12 не срабатывают и сигналов для фиксации и запоминания не вырабатывают. На выходе элемента ИЛИ 9 образуется последовательность импульсов. Если хотя бы у одного из сигналов определенного участка тракта синхронизации изменится контролируемый параметр, причем длительность изменения больше длительности развертки строки, то изменится напряжение соответствующего датчика-преобразователя 7 и изменится фазовое положение импульса, вырабатываемого соответствующим формирователем 8. При построчной записи эти фазовые изменения проявятся в виде искривления или дрожания соответствующей линии тест-сигнала. При этом также сработает первый и второй пороговый элемент 11, 12 соответствующего блока. Когда хотя бы у одногоиз сигналов определенного участка тракта синхронизации изменится контролируемый параметр, причем длительность изменения меньше длительности развертки строки, и произошло это изменение между двумя фазовыми импульсами, изменится напряжение на выходе соответствукляего .датчика-преобразователя 7. При изменении напряжения в промежутке между двумя фазовыми импульсами в ту или другую сторону, срабатывает первый пороговый элемент 11 или второй пороговый элемент 12 блока 10, Сигналы которых через элемент ИЛИ 13 воздействуют на элемент памяти 14, на выходе которого образуется сигнал, поступающий на вход элемента И 17. При поступлении импульса фазирования формирователь 8 вырабатывает импульс контроля, который, не изменяя своего фазового положения, поступает на соответствующий вход элемента ИЛИ 9 и на вход формирователя 16. С выхода формирователя 16 импульс считывания: поступает на второй вход элемента И 17 и осуществляется считывание информации об изменении параметра контролируемого сигнала. Эт.а информация в виде импульса с выхода элемента И 17 поступает на соответствующий дополнительный вход элемента ИЛИ 9 и вместе с импульсом тест-сигнала и импульсами от формирователей 8 с выхода элемента ИЛИ 9 поступает на вход формирователя 4 и далее через второй элемент И 5 вместе с видеосигналом от его источника следует на записывающее устройство. Таким образом, независимо от соотношения длительностей возникшего из- менения и развертки строки, а также

времени возникновения, оно будет зафиксировано на фотопленке. Формула изобретения

N блоков построчной фиксации и запоминания контролируемого параметра, информационный вход каждого из которых соединен с выходом соответствующего датчика-преобразователя сигналов, а вход считывания соединен с выходом соответствующего Формирователя фазового положения импульсов, при этом вход стирания соединен с выходом формирователя длительности фазовых импульсов приемника, а выход каждого из блоков построчной фиксации и запоминания контролируемого параметра соединен с соответствующим дополнительным входом элемента ИЛИ.

0 формирователя импульсов считывания и выход элемента И являются соответственно входом считывания и выходом блока построчной фиксации и запоминания кoнтpo iиpyeмoгo параметра.

Ln

I IK .

Авторы

Даты

1980-09-15—Публикация

1978-04-04—Подача