1

Изобретение относится к импульсной технике и предназначено для использования в частотомерах, счетчиках импульсов и других цифровых устройствах.5

Известен накопительный делитель частоты, содержащий тиристор на транзисторах различной проводимости, накопительный конденсатор и разрядный транзистор l.10

Недостатком известного делителя частоты является недостаточная стабильность коэффициента деления.

Наиболее близким техническим решением к изобретению является дели- 5 тель частоты импульсов, содержащий накопительный конденсатор, резисторы, диод и пороговый элемент, выполненный на однопереходном транзисторе 2 .20

В таком делителе частоты импульсов постоянная времени заряда накопительного конденсатора больше, чем длительность входных импульсов, благодаря чему конденсатор заряжается 25 ступенчато. Коэффициент деления определяется номиналами времязадающей цепи и пороговым значением включения разрядного ключа. При большом коэффициемте деления амплитуда ступеньки, 30

вызванная очередным входным импульсом, становится малой и ее величина соизмерима с флуктуациями питающего напряжения. Так как пороговое значение включения разрядного ключа неизменное, то встретиться пороговое значение и ступенчатое напряжение на конденсаторе при большом коэффициенте деления могут только под очень острым углом. Это вызывает нестабильность коэффициента деления.

Целью изобретения является повыиение стабильности коэффициента деления.

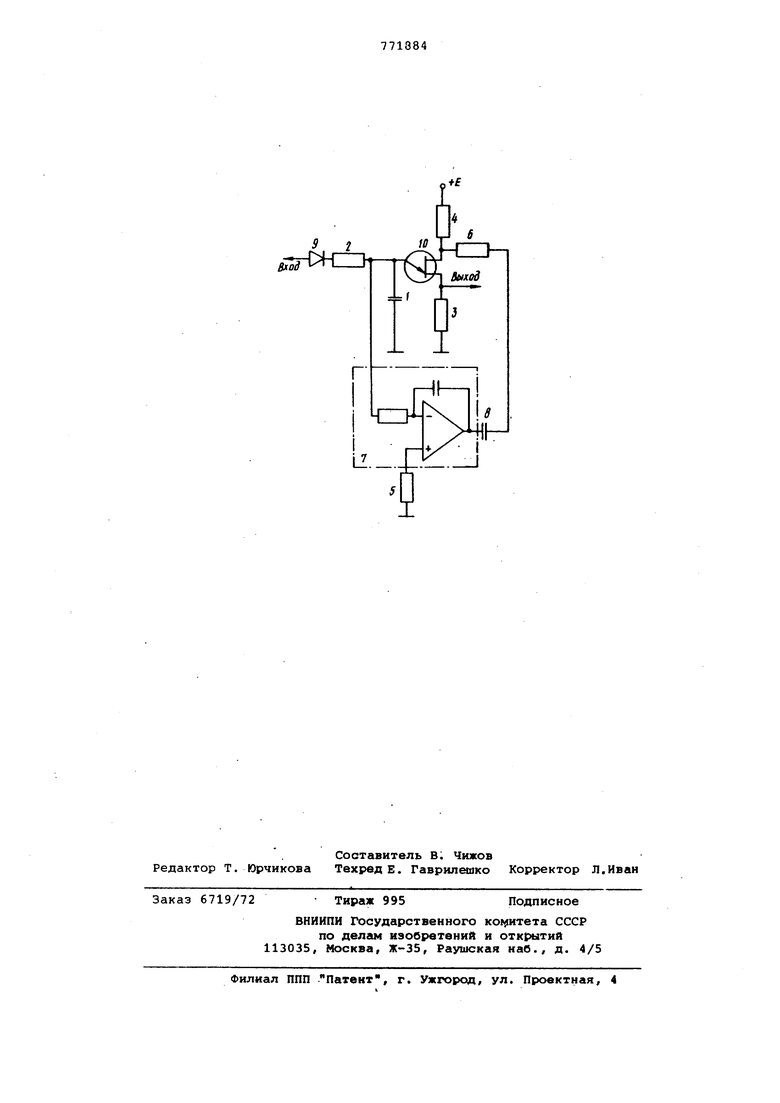

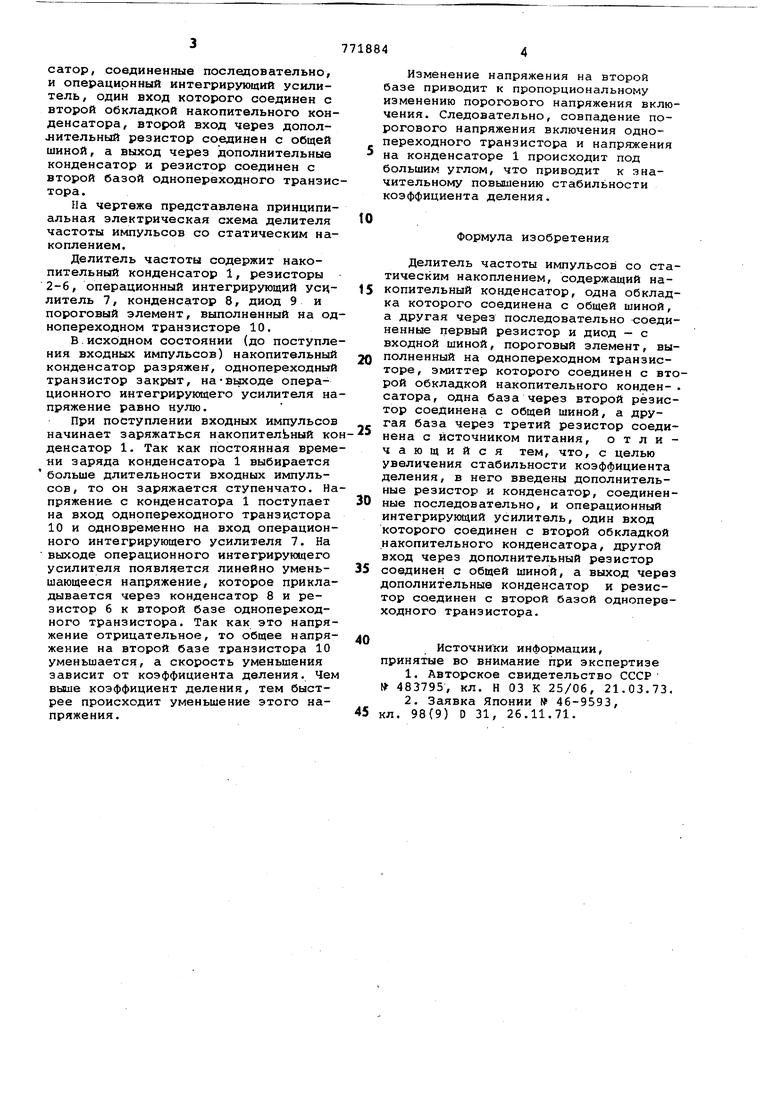

Цель достигается тем, что в делитель частоты импульсов со статическим накоплением, содержащий накопительный- конденсатор, одна обкладка которого соединена с общей шиной, а другая через последовательно соединенные первый резистор и диод - с входной шиной, пороговый элемент, выполненный на однопереходном транзисторе , эмиттер которого соединен с второй обкладкой накопительного конденсатора, одна база через второй резистор соединена с общей шиной, а другая база через третий резистор соединена с источником питания, введены дополнительные резистор и конленсатор, соединенные последовательно, и операционный интегрирующий усилитель, один вход которого соединен с второй обкладкой накопительного конденсатора, второй вход через дополнительный резистор соединен с общей шиной, а выход через дополнительные конденсатор и резистор соединен с второй базой однопереходного транзис тора. На чертеже представлена принципиальная электрическая схема делителя частоты импульсов со статическим накоплением. Делитель частоты содержит накопительный конденсатор 1, резисторы 2-6, операционный интегрирующий усчлитель 7, конденсатор 8, диод 9 и пороговый элемент, выполненный на од нопереходном транзисторе 10. В исходном состоянии (до поступле ния входных импульсов) накопительный конденсатор разряжен, однопереходный транзистор закрыт, на-выходе операционного интегрирующего усилителя на пряжение равно нулю. При поступлении входных импульсов начинает заряжаться накопительный ко денсатор 1. Так как постоянная време ни заряда конденсатора 1 выбирается больше длительности входных импульсов, то он заряжается ступенчато. На пряжение с конденсатора 1 поступает на вход однопереходного транзистора 10 и одновременно на вход операционного интегрирующего усилителя 7. На выходе операционного интегрирующего усилителя появляется линейно уменьшающееся напряжение, которое прикладывается через конденсатор 8 и резистор 6 к второй базе однопереходного транзистора. Так как это напряжение отрицательное, то общее напряжение на второй базе транзистора 10 уменьшается, а скорость уменьшения зависит от коэффициента деления. Чем выше коэффициент деления, тем быстрее происходит уменьшение этого напряжения. Изменение напряжения на второй базе приводит к пропорциональному изменению порогового напряжения включения. Следовательно, совпадение порогового напряжения включения однопереходного транзистора и напряжения на конденсаторе 1 происходит под большим углом, что приводит к значительному повышению стабильности коэффициента деления. Формула изобретения Делитель частоты импульсов со статическим накоплением, содержащий накопительный конденсатор, одна обкладка которого соединена с общей шиной, а другая через последовательно соединенные первый резистор и диод - с входной шиной, пороговый элемент, выполненный на однопереходном транзисторе, эмиттер которого соединен с второй обкладкой накопительного конден- . сатора, одна база через второй резистор соединена с общей шиной, а другая база через третий резистор соединена с источником питания, отличающийся тем, что, с целью увеличения стабильности коэффициента деления, в него введены дополнительные резистор и конденсатор, соединенные последовательно, и операционный интегрирующий усилитель, один вход которого соединен с второй обкладкой накопительного конденсатора, другой вход через дополнительный резистор соединен с общей шиной, а выход через дополнительные конденсатор и резистор соединен с второй базой однопереходного транзистора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 483795, кл. Н 03 К 25/06, 21.03.73. 2.Заявка Японии № 46-9593, кл. 98(9) D 31, 26.11.71.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты | 1977 |

|

SU739745A1 |

| Стабилизирующий преобразователь напряжения с защитой | 1989 |

|

SU1682990A1 |

| Генератор пилообразного напряжения | 1976 |

|

SU571888A1 |

| Регулируемый преобразователь переменного напряжения | 1986 |

|

SU1387144A1 |

| Устройство для определения средневзвешенного значения функции | 1976 |

|

SU636626A1 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ЭЛЕКТРОДВИГАТЕЛЯ | 1991 |

|

RU2015596C1 |

| Генератор импульсов | 1989 |

|

SU1661970A1 |

| Делитель частоты | 1981 |

|

SU997258A1 |

| Преобразователь заряд-число | 1979 |

|

SU819960A1 |

| Импульсный регулятор | 1980 |

|

SU934456A1 |

Авторы

Даты

1980-10-15—Публикация

1978-11-09—Подача