;54) ГЕНЕРАТОР ИМПУЛЬСНЫХ СИГНАЛОВ Генератор импульсных сигналов к импульсной технике, может быть использован в качестве задающего гене ратооа в цифровых устройствах. Известен генератор импульсных сигналов/ содержащий два логических элемента НЕ, кварц, резистивный делитель напряжения и формирователь на логическом элементе НЕ 1. Известные генераторы импульсных сигналов обладают ограниченными функ циональными возможностями генерирова ния импульсных сигналов по частоте. В приведенном прототипе для генерирования импульсных сигналов низкой частоты необходимо увеличить емкость времязадающего элемента (конденсатора) , а для генерирования импульсных сигналов высокой частоты уменьшать емкость конденсатора. Сопротивление второй половины делителя напряжения и внутреннее сопротивление открытого второгл ЛЪгического элемента И-НЕ по ключены параллельно. Поэтому, общее сопротивление эк.е, выходе второго логического элемента И-НЕ будет мень ше наименьшего. Исходя из того, что постоянная времени в этой цепи , - 34%.. то генерирование импульсных сигналов

.,эиввв «ЯвЛлг«ж а егЛ

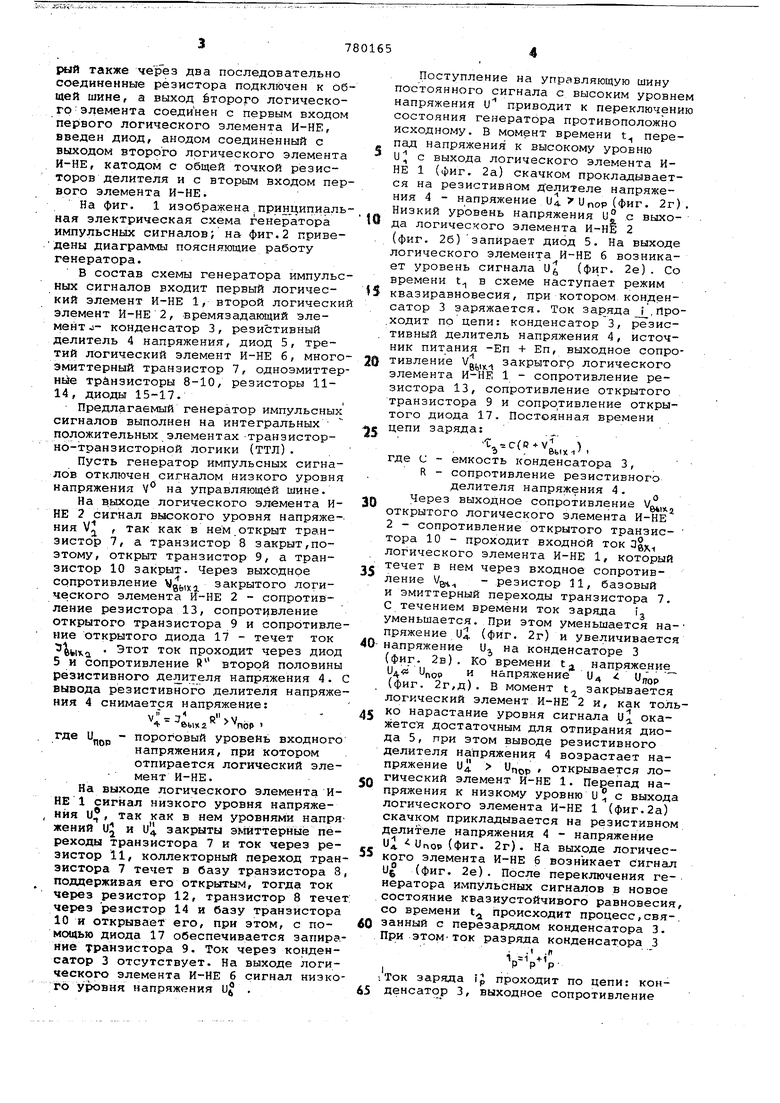

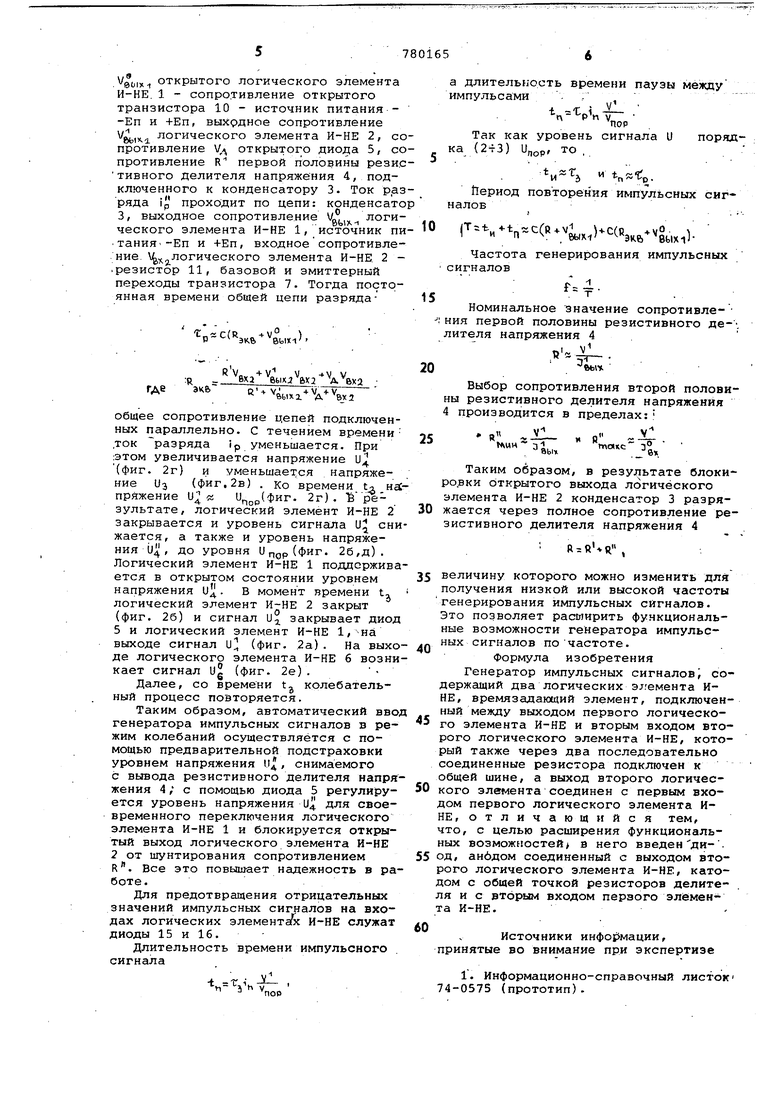

HTS J. . 19 f..it f-. ffv-j./ Т . 4 с низкой частотой или с высокой частотой невозможно. Так как в первом случае увеличение сопротивления второй половины .резистивного делителя напряжения приводит к обратному деистВИЮ - к уменьшению постоянной времени Т , а во втором случае к шунтированию выхода второго логического элемента И-НБ. Непосредственное подключение открытого выхода второго логического элемента И-НЕ к выводу резистивного делителя напряжения приводит к искажению формы импульса, которое наблюдается на выходе формирователя в виде излома и возможен срыв генерирования импульсных сигналов, -т.е. режим жесткого возбуждения генератора. Это приводит к уменьшению надежности в работе. Целью изобретения является расширение функциональных возможностей. Для достижения указанной цели в генератор импульсных сигналов, содержащий два логических элемента И-НЕ, времязадающий элемент, подключенный между выходом первого логического элемента И-НЕ и вторым входом второго логического элемента И-НЕ, который также через два последовательно соединенные резистора подключен к об щей шине, а выход ёторого логического элемента соединен с первым входом первого логического элемента И-НЕ, введен диод, анодом соединенный с выходом второго логического элемента И-НЕ, катодом с общей точкой резисторов делителя и с вторым входом пер вого элемента И-НЕ. На фиг. 1 изображена .прин ципиаль ная электрическая схема генератора импульсных сигналов; на фиг,2 приведены диаграммы поясняющие работу генератора. В состав схемы генератора импульс ных сигналов входит первый логический элемент И-НЕ 1, второй логически элемент И-НЕ 2, времязадающий элемент - конденсатор 3, резистивный делитель 4 напряжения, диод 5, третий логический элемент И-НЕ б, много эмиттерный транзистор 7, одноэмиттер ные транзисторы 8-10, резисторы 1114, диоды 15-17. Предлагаемый генератор импульсных сигналов выполнен на интегральных положительных элементах транзисторно-транзисторной логики (ТТЛ). Пусть генератор импульсных сигналов отключен сигналом низкого уровня напряжения на управляющей шине. На выходе логического элемента ИНЕ 2 сигнал высокого уровня напряжения V , так как в нем открыт транзистор 7, а транзистор 8 закрыт,поэтому, открыт транзистор 9, а транзистор 10 закрыт. Через выходное сопротивление д;,, закрытого логического элемента И-НЕ 2 - сопротивление резистора 13, сопротивление открытого транзистора 9 и сопротивле ние открытого диода 17 - течет ток Iwxu. Этот ток проходит через диод 5 и сопротивление к второй половины резистивного делителя напряжения 4. вывода резистивного делителя напряже ния 4 снимается напряжение: вЫЧ2 пороговый уровень входного напряжения, при котором отпирается логический элемент И-НЕ. На выходе логического элемента ИНЕ 1 сигнал низкого уровня напряже, нйя и, так как в нем уровнями напря жений Uj и и закрыты экшттерныё переходы транзистора 7 и ток через резистор 11, коллекторный переход тран зистора 7 течет в базу транзистора 8 поддерживая его открытым, тогда ток через резистор 12, транзистор 8 тече через резистор 14 и базу транзистора 10 и открывает его, при этом, с помощью диода 17 обеспечивается запира ние транзистора 9. Ток через конденсатор 3 отсутствует. На выходе логического элемента И-НЕ б сигнал низко го уровня напряжения U . Поступление на управляющую шину постоянного сигнала с высоким уровнем напряжения U приводит к переключению состояния генератора противоположно исходному. В момент времени t перепад напряжения к высокому уровню и с выхода логического элемента ИНЕ 1 (фиг. 2а) скачком прокладывается на резистивном делителе напряжения 4 - напряжение ui и ПОР (фиг. 2г). Низкий уровень напряжения U° с выхода логического элемента И-НЕ 2 (фиг. 26)запирает диод 5. На выходе логического элемента И-НЕ б возникает уровень сигнала U (фиг. 2е). Со времени t в схеме наступает режим квазиравновесия, при котором конденсатор 3 заряжается. Ток заряда J, Проходит по цепи: конденсатор 3, резистивный делитель напряжения 4, источник питания -Еп + Еп, выходное сопротивление vl, закрытого логического элемента И-НЕ 1 - сопротивление резистора 13, сопротивление открытого транзистора 9 и сопротивление открытого диода 17. Постоянная времени цепи заряда: . ,). где (J - емкость конденсатора 3, R - сопротивление резистивного делителя напряжения 4. Через выходное сопротивление V, открытого логического элемента И-НЕ 2 - сопротивление открытого транзистора 10 - проходит входной ток Зв;, логического элемента И-НЕ 1, который течет в нем через входное сопротивление Vg - резистор 11, базовый и змиттерный переходы транзистора 7. С течением времени ток заряда ij уменьшается. При этом уменьшается напряжение ui (фиг. 2г) и увеличивается напряжение Uj на конденсаторе 3 (фиг. 2в). Ко времени t напряжение напряжение U U -тMVf- llOP (фиг. 2г,д). В момент t закрывается логический элемент И-НЕ 2 и, как только нарастание уровня сигнала U окажется достаточным для отпирания диода 5, при этом выводе резистивного делителя напряжения 4 возрастает напряжение Цд ЦПОР , открывается логический элемент И-НЕ 1. Перепад напряжения к низкому уровню и 5 с выхода логического элемента И-НЕ 1 (фиг.2а) скачком прикладывается на резистивном делителе напряжения 4 - напряжение и. Unop (фиг. 2г). На выходе логического элемента И-НЕ б возникает сигнал и (фиг. 2е). После переключения генератора импульсных сигналов в новое состояние квазиустойчивого равновесия, со времени t происходит процесс,свя-. занный с перезарядом конденсатора 3. При ЭТОМток разряда конденсатора 3 VVV; Ток заряда ip проходит по цепи: конденсатор 3, выходное сопротивление

.801X1 открытого логического элемента И-НЕ.1 - сопротивление открытого транзистора 10 - источник питания -Еп и +ЕП, выходное сопротивление

логического элемента И-НЕ 2, соV,

6bl.i п от ивление Уд открытого диода 5, сопротивление R первой половины резистивного делителя напряжения 4, подключенного к конденсатору 3. Ток р,азряда ip проходит по цепи: конденсатор 3, выходное сопротивление Vg логического элемента И-НЕ 1, источник питаниЯ-Еп и +ЕП, входное сопротивление. V логического элемента И-НЕ. 2 -

.резистор 11, базовой и эмиттерный переходы транзистора 7. Тогда постоянная времени общей цепи разряда,0 ВЫ«1

(,«.)R У„ + V V -tV V :R Вха вЫХД ЙУ2

экь

V -4- V 4- V

А ВХ2

Общее сопротивление цепей подключенных параллельно. С течением времени ,ток разряда ip уменьшается. При этом увеличивается напряжение U (фиг. 2г) и уменьшается напряжение УЗ (фиг,2в) . Ко времени to на:пряжение U « (фиг. 2г) . Врезультате, логический элемент И-НЕ 2 закрывается и уровень сигнала U; снижается, а также и уровень напряжения и , до уровня иг,др(фиг. 26,д) . Логический элемент И-НЕ 1 поддерживается в открытом состоянии уровнем напряжения u(. В момент времени t логический элемент И-НЕ 2 закрыт (фиг. 2б) и сигнал U закрывает диод 5 и логический элемент И-НЕ 1, на выходе сигнал U (фиг. 2а). На выходе логического элемента И-НЕ б возникает сигнал Ug (фиг. 2е).

Далее, со времени t колебательный процесс повторяется.

Таким образом, автоматический ввод генератора импульсных сигналов в режим колебаний осуществляется с помощью предварительной подстраховки уровнем напряжения Ид, снимаемого с вывода резистивного делителя напряжения 4; с помощью диода 5 регулируется уровень напряжения U для своевременного переключения логического элемента И-НЕ 1 и блокируется открытый выход логического элемента И-НЕ 2 от шунтирования сопротивлением R. Все это повышает надежность в работе.

Для предотвращения отрицательных значений импульсных сигналов на входах логических элемента1х И-НЕ служат диоды 15 и 1б.

Длительность времени импульсного сигнала

,op

а длительность времени паузы между импульсами

t -С i ,,

Так как уровень сигнала U

поряяка (2-гЗ) и„ор, то ,

t т

Ь

ГТериод повторения импульсных сигналов

10 jT t 4-t 7iCCR+V Uc(0 +w° 1 и n быт ЭК6 ВЫХ11Частота генерирования импульсных сигналов

f - -1. . т

15

Номинальное значение сопротивле. ния первой половины резистивного делителя напряжения 4

ftWH

20

Выбор сопротивления второй половины резистивного делителя напряжения 4 производится в пределах: у- .. 1/

«;c,.c-i55NSMH

аыт

Ъ

Таким образом, в результате блокировки открытого выхода логического элемента И-НЕ 2 конденсатор 3 разряжается через полное сопротивление резистивного делителя напряжения 4

R ftUft,

35 величину которого можно изменить для получения низкой или высокой частоты генерирования импульсных сигналов. Это позволяет расширить функциональные возможности генератора импульсных сигналов почастоте.

40

Формула изобретения Генератор импульсных сигналовj содержащий два логических эдгемента ИНЕ, времязадающий элемент, подключенный между выходом первого логическо 5 го элемента И-НЕ и вторым входом второго логического элемента И-НЕ, который также через два последовательно соединенные резистора подключен к общей шине, а выход второго логического элемента соединен с первым входом первого логического элемента ИНЕ, отличающийся тем, что, с целью расширения функциональных возможностей в него введенди-.

55 од, анбдом соединенный с выходом второго логического элемента И-НЕ, катодом с общей точкой резисторов делителя и с вторым входом первого эл1емента И-НЕ.

60

Источники инфо1 мации, принятые во внимание при экспертизе

1. Информационно-справочный листок 74-0573 (прототип).

fltfSuu ивгический

Второй логический менент И-М злеиент и-не

Tptmuu /roit/i/ecfi/u элемент n-Hf

| название | год | авторы | номер документа |

|---|---|---|---|

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР ИМПУЛЬСОВ | 2003 |

|

RU2254670C1 |

| Стабилизатор напряжения с защитой от перегрузок | 1985 |

|

SU1298728A1 |

| Генератор пилообразного напряжения | 1983 |

|

SU1127080A2 |

| Мультивибратор | 1979 |

|

SU790122A1 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ ИЗБЫТОЧНОЙ МОЩНОСТИ СОЛНЕЧНОЙ БАТАРЕИ | 2000 |

|

RU2199808C2 |

| УСТРОЙСТВО ДЛЯ ДВУХПОЗИЦИОННОГО РЕГУЛИРОВАНИЯ ТЕМПЕРАТУРЫ | 2002 |

|

RU2233467C1 |

| УПРАВЛЯЕМЫЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 2004 |

|

RU2257003C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИМПУЛЬСОВ | 2004 |

|

RU2256288C1 |

| Импульсный стабилизатор напряжения с защитой от перегрузок по току | 2019 |

|

RU2711138C1 |

| РЕГУЛЯТОР НАПРЯЖЕНИЯ ГЕНЕРАТОРА | 1997 |

|

RU2118040C1 |

Авторы

Даты

1980-11-15—Публикация

1978-06-14—Подача