1

Изобретение относится к области автоматической сигнализации, в частности к устройствам обнаружения неисправности в системах сигнал изации, и может быть применено в различных отраслях промышленности,

Известны устройства для обнаружения неисправности в системах сигнализации, содержащие два логически элемента И-НЕ, генератор импульсов, логический элемент ИЛИ-НЕ, схему неравнозначности, лампочку обнаружения неисправности. Выход генератора соединен с соответствующими входами систем сиг-нализации и одним из входов логического элемента И-НЕ, выход которого подключен к одному из входов логического.элемента ИЛИ-НЕ, другие входы этого элемента соединены с соответствующими выходами систем сигнализации, а выход его - с одним из входов логической схемы неравнозначности, другой вход которой связан с другим входом первого логического элемента И-НЕ и через второй логический элемент И-НЕ с датчиками, а выход логической схемы неравнозначности соединен с индикато ром Ij .

К недостаткам известных устройств относится требование одновременного

срабатываниявсех датчиков. К тому же известные устройства не контролируют правильность работы систем сигнализации с памятью, т. е, таких, у которых при исчезновении сигнала от датчика на входе на выходе системы сигнал не исчезает до момента квитирования.

Наиболее близким по технической сущности к предложенному устройству является устройство для обнаружения неисправного канала сигнализации, содержащее блок управления, выполненtS ный на генераторе импульсов, элементах ИЛИ, блок памяти, блок индикации, элементы ИЛИ-НЕ и И. Одни из входов элементов ИЛИ соединены с входными шинами устройства и .с входами элеменМ та ИЛИ-НЕ, выход которого подключен к входу блока управления, один из выходов которого соединен с другими входами элементов ИЛИ, другой выход - с управляющим входом блока памяти, другие входы которого соединены с выходами элементов ИЛИ, а выходы блока :Памяти связаны с соответствующими входами блока индикации и элемента и,выход которого соединен с входом блока

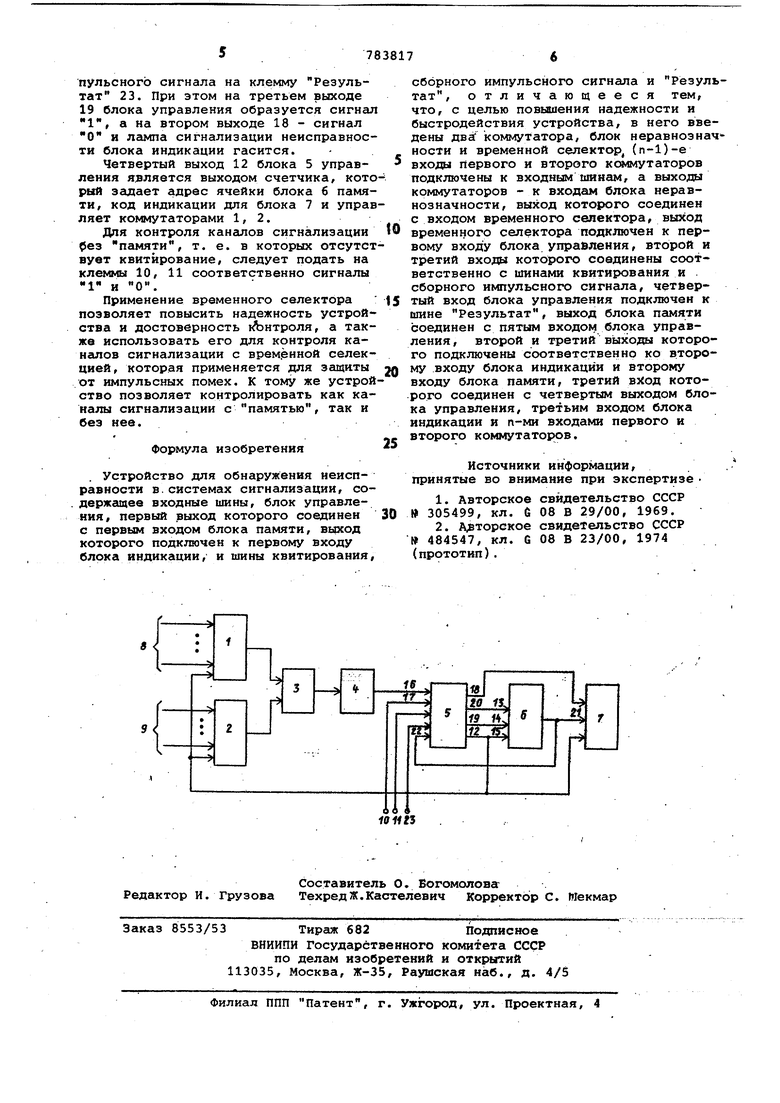

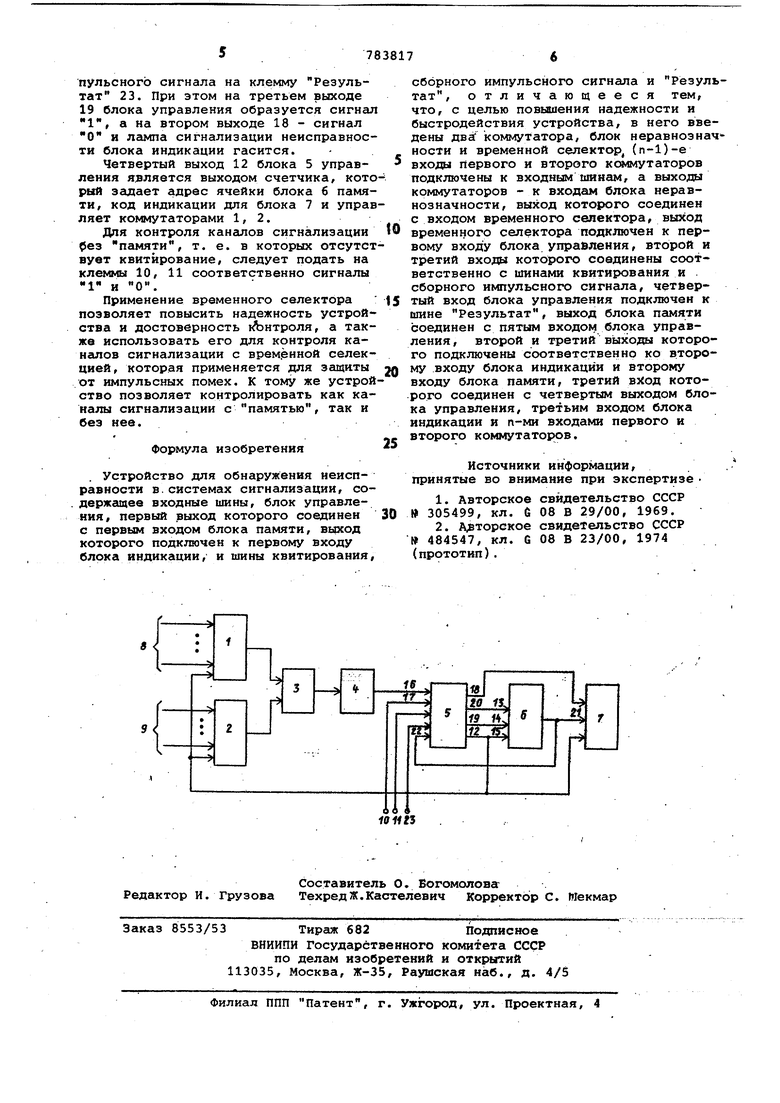

30 .индикации И . 378 Недостатком устройства-прототипа влягется относительно малая надежность работы, а при контроле каналов сигна.лйзации с памятью После кйЖдб гб цикла контроля требуется установка каналов в исходное со тОйнйё, -vtfef fipiliiSaKt к дополнительным затратам времени, а также может вызвать потерю полезной инфсэрмаций импульсного харак е ра Тзо время установки каНалов в исходное состояние/ что иногда недопустимо. Цель и-зобретения - повышение надежности работы и быстродействия yctjpdftcTBa. Поставленная задача достигается тем, что в устройство введены два ком мутатора, блок неравнозначности мённоЙ селектор. (п-ГТ-е взсо да ПбрвОгби второго коммутаторов ; подключены к входным шинам, а 1выхб; №1 коммутаторов подключены к входам блока неравнозначности, выход которого соединен с входом временного селектора. Выходврёменного селектора подклю чён к первому 1входублока управления, второй и третийвходы которого соёди;J MHM соответственно с шинами квитирования и сборного импульсного сигнала. Четвертый вход блока управления подключен к шине Результат. Выход блока памяти соединен с пятым входом бло - K1rTffpllШWШГЗт r lтШПI ttШ KOTOporjp подключены соответственно ко второму входу индикации и второ му входу блока памяти) трётийвход ко Tcfjporo соединен с четвертьпч выходом блоки управления, TjpeTbHM входом блок индикации и п-ми входами первого и вт рого коммутаторов. Блок-схема устройства приведена на чертеже. . Устройство содержит два коммутатора 1, 2, схему 3 неравнозначности, временной селектор 4, блок 5 управления, блок 6 памяти и блок 7 индикации Входные шины 8, 9 устройства подключе ны соответственно к входам и вьКодам KfatHaJiOB или систем сигнализации, клеммы 10, 11 соединены с шинами квитйрования и сборного и myльcнoгo сйгйала, идущего от кана:лЬв или сигналйЭ1ации. - ,.--...-:-«.-..Работает устройство следующим образом.. Под действием управляк)щего Сйг11ала с четвертогб выхода 12 блока 5 управления с помощью коммутатО юв 1, 2 по входным шинам 8, 9 бЙрЁвшйШтся сбсто яния входов и выходов каналов или си -cr6W сигйалйзаций. Входы 13, 14, 15 блока Памйти соединены с блоком управ леиия. Сигналы состояний с выходов KONB yxaTopoB 1, 2 поступают на входы схемы 3 йёравноэйаЧности, на вьосодё . которой, при нерЖйёЖ1ёг вё сйгнсШсай на её входах при наличии неисправности, образуется сигнал 1, поступающий на входBpejuieHHoro селектора 4. Если Длительмоеть этогб Ш1 На1йа йё мейёё заданной, то на выходе временного селектора 4 образуется импульсный сигНал, поступающий на первый вход 16 блока 5 управления. При этом, если до этого момента времени не было сигнаМ7 вй йрб &йния, который поступает на второй вход 17 блока управления, то запоминания этого сигнала неисправности не происходит, на втором выходе 18блока управления образуется сигнал О и лймпа блока 7 индикации, сигнализирующая наличие неисправности, не сйёТится. При этом на третьем выходе 19блока управления образуется сигнал О, Что соответствует команде чтения информации из блока 6 памяти, но так как в блок памяти ничего не записано, то на выходе появляется сигнал О и цифровые индикаторы блока 7 индикации не светятся. После прихода импульсного сигнала квитирования на клемму 10 сигнал неисправности (при наличии неисправноети) с выхода временного селектора 4 поступает на первый вход 16 блока 5 Управления. При этом на третьем выходе 19 блока управления образуется сигнал 1, это соответствует команде записи в блок б памяти, а на первом выходе 20 блока управления появляется jCH THaLn 1 jjJiи О в 3 а ви симос т и от тсГг-о, есть неисправность или нет, т.е. имеется сигнал на выходе временного селектора 4 или нет. Таким образом, осуществляется последовательная запись в блок 6 памяти сигналов неисправности каналов сигнализации. Причем первый же сигнал неисправности инициирует образование сигнала 1 на втором выходе 18 блока 5 управления и лампа сигнализации неисправности блока 7 индикации светится. При приходе сборного импульса сигнала от каналов сигнализации на клемму 11, KOTOt Hfl появляется в случае поступления ни вход хотя бы одного канала сигнала от датчика, сигнал с выхода временного селектора 4 не прохоДит на первый выход 20 блока 5 управления, на третьем выходе 19 блока управленияобразуется сигнал О, что СЬртвётсТвуёт команде чтения информации из блока 6 памяти. Информация р наличии неисправностей ndcTynaeT на первый вход 21 блока индикации. Если при этом на вьйсоде блока 6 памяти появится сигнал 1, гово рящий 6 наличии неисправности в каком-либо канале, то этот Сигнал поступает на пятый вход 22 блока 5 управления и запрещает счет счетчика блока управления, а на цифровом индикаторе блока 7 индикации высвечиваётЬя номер неисправного канала. Режим чтения информации из блока 6 Пс1мяти продйлжа(е( момента прихода импульсного сигнала квитирования на (Клемму 10.. Реж1ш чтения может быть также осуществлен путем подачи импульсного сигнала на клевлму Результат 23. При этом на третьем выходе 19 блока управления образуется сигнал 1, а на втором выходе 18 - сигнал О и лампа сигнализации неисправности блока индикации гасится. Четвертый выход 12 блока 5 управления является выходом счетчика, кото рый Зсщает адрес ячейки блока 6 памяти, код индикации для блока 7 и управ ляет коммутаторами 1, 2. Для контроля каналов сигнализации 5ез памяти, т. е. в которых отсутст вует квитирование, следует подать на клеммы 10, 11 соответственно сигналы 1 и О. Применение временного селектора позволяет повысить надежность устройства и достоверность |Лэнтроля, а также использовать его для контроля кангшов сигнализации с врем.ённой селекцией, которая применяется для защиты от импульсных помех. К тому же устрой ство позволяет контролировать как каналы сигнализации с памятью без нее. Формула изобретения Устройство для обнаружения неисправности в. системах сигнализации, содержащее входные шины, блок управления, первый выход которого соединен с первым входом блока памяти, выход которого подключен к первому входу блока индикации, и шины квитирования сборного импульсного сигнала и Результат, отличающееся тем, что, с целью повышения надежности и быстродействия устройства, в него введены два: коммутатора, блок неравнозначности и временной селектор, (n-l)-e входы первого и второго кслимутаторов подключены к входным шинам, а выходы коммутаторов - к входам блока неравнозначности, выход которого соединен с входом временного селектора, выход временного селектора подключен к первому входу блока управления, второй и третий входы которого соединены соответственно с шинами квитирования и сборного импульсного сигнала, четвертый вход блока управления подключен к шине Результат, выход блока Пс1мяти соединен с пятым входом блока управления, второй и третий выходы которого подключены соответственно ко второму входу блока индикации и второму входу блока памяти, третий вход кото.рого соединен с четвертым выходом блока управления, третьим входом блока индикации и п-ми входами первого и второго коммутаторов. Источники информации, , . принятые во внимание при экспертизе 1.Авторское свидетельство СССР 305499, кл. С 08 В 29/00, 1969. 2.Авторское свидетельство СССР 484547, кл. G 08 В 23/00, 1974 (прототип).