(54) АНАЛОГбИ Й КОМПАРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизатор напряжения с самозащитой | 1982 |

|

SU1046751A1 |

| Коммутатор вентильного электродвигателя | 1988 |

|

SU1582290A1 |

| Компенсационный стабилизатор постоянного напряжения | 1981 |

|

SU922698A1 |

| Стабилизатор постоянного напряжения | 1979 |

|

SU943674A1 |

| Стабилизатор постоянного напряжения с защитой от перегрузки по току | 1981 |

|

SU978129A1 |

| Устройство для измерения параметров рассеяния транзисторов | 1982 |

|

SU1084709A1 |

| Усилитель мощности | 1982 |

|

SU1131021A1 |

| ШИРОКОПОЛОСНЫЙ УСИЛИТЕЛЬ ВЫСОКОЙ ЧАСТОТЫ | 1992 |

|

RU2074507C1 |

| Усилитель мощности | 1984 |

|

SU1224964A1 |

| Низковольтный стабилизатор напряжения | 1980 |

|

SU868725A1 |

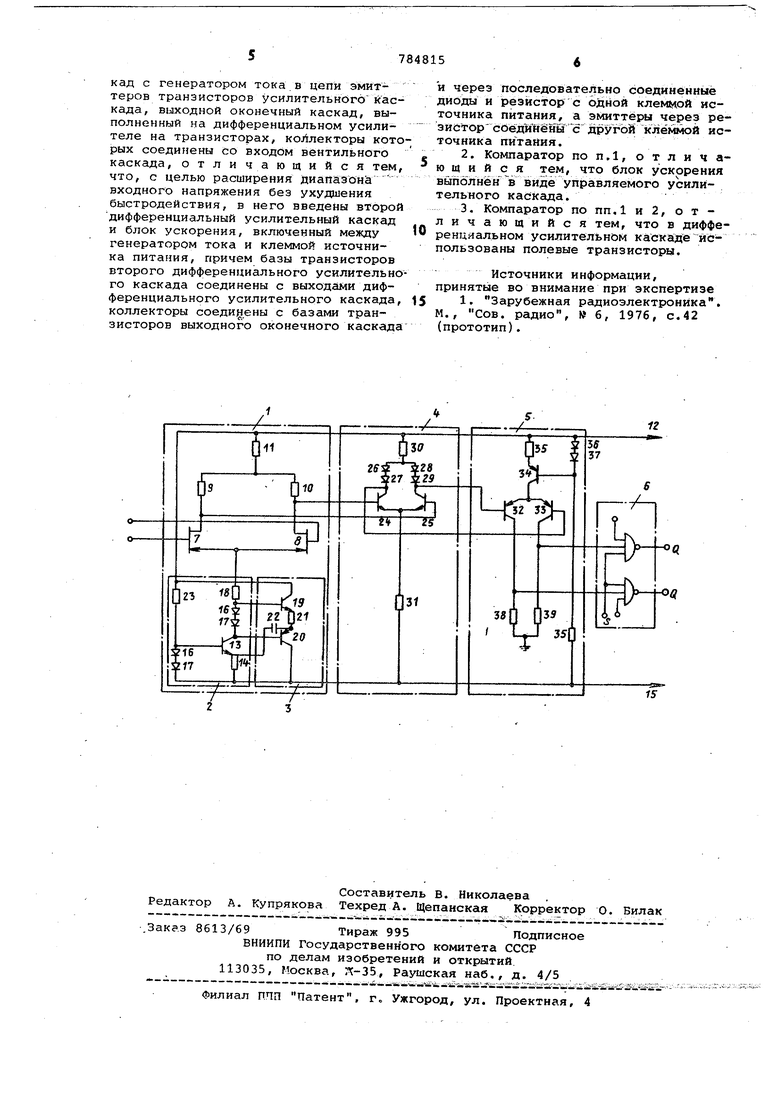

Изобретение относится к измеритель ной технике и найдет применение в электронных устройствах, преимуществе но в приборах техники связи. Известен аналоговый компаратор, сЪдержащий дифференциальный усилитель ный каскад с генератором тока в цепи эмиттеров транзисторов усилит ельного каскада, выходной оконечный каскад, выполненный на дифференциальном усили теле на транзисторах, коллекторы кото рых соединены с входом вентильного каскада l . .Недостатком такого компаратора является то, что он может применяться в сравнительно узком диапазоне входно го напряжения. Цель изобретения - расширение диапазона входного напряжения без ухудшения быстродействия компаратора. Указанная цель достигается тем, что в аналоговый компаратор, содержащий дифференциальный усилительный каскад с генератором тока в цепи эмит теров транзисторов усилительного каскада, выходной оконечный .каскад, выполненный на дифференциальном усилителе на транзисторах, коллекторы которых соединены со входом вентильного каскада, введены второй дифференциальный усилительный каскад и блок, ускорения, включенный -между генератором тока и клеммой источника питаиия, причем база транзисторов второго дифференциальногю усилительного каскада соединены с выходами дифференцигшьного усилительного каскгща, коллекторы соединены с е$ааами транзисторов выходного оконечного каскада и через прследовательно Соединенные диоды и резистор - с одной клеммой источника питания, а эмиттеры через резистор соединены с другой клеммой источника питания , при этом блок ускорения выполнен в виде управляемого усилительного каскада, а в дифференциальном усйлительиом каскаде использованы полете транзисторы, На чертеже изображена принципиальная схема аналогового компаратора. Компаратор содержит снабженный полевыми транзисторами.входной дифференциальный усилительный каскад 1г причем дифференциальный усилитель имеет генератор 2 тока и блок 3 ускорения. Затворы полевых транзисторов, осуществляющих функции управляемое элементов, образуют входы входного дифференцисшьного усилительного ijacxaда 1. На выходе дифференциального усялитёльногб каскада 1 включен дифферен циальный усилительный каскад 4. Выход дифференциального усилительного каскада 4 через оконечный каскад 5 соединен с вентильным каскадом б для передачи нагрузки на выходе. Входы компаратора образованы затвс.ами полевых транзисторов 7 и 8, расположенных во входном дифференциал ном усилительном каскаде. Стоки полевых транзисторов 7 и 8 образуют с одной стороны выход этого каскада, а с друго стороны они соединены через резистор 9 или резистор 10 и через общий резистор Не первой 12 источника напряжения. Совместно включенные истоки полевых транзисторов 7 и 8 присоединены к выходу генератора 2тока. Генератор 2 тока содержит транзистор 13 с разомкнутым коллектором. Эмиттер транзистора 13 соединен через резистор 14 со второй клеммой 15 источника напряжения. Коллектор транзистора 13 через последовательно включенные вторые диоды 16 и 17, а также через резистор 18 выполняет функцию входа генератора 2 тока. Генератор 2 тока соединен с блоком 3у скорения, выполненным как управляемый усилигельный каскад. Управляемый усилительный каскад содержит транзистор 19 типа п-р-п и транзистор 20типа р-п-р, включенные между двумя клеймами 15 и 12 источника напряжения Тран зйстор 20 соединен через резистор 21с эмиттером транзистора 19. База транзистора 20 присоединена к коллектору транзистора 13, расположенному в генераторе 2 тока. Эмиттер транзистора 20 через конденсатор 22 соединен с эмиттером транзистора 13. База транзистор 21 соединена с общей точкой диода 16 и резистора 18. База транзистора 13, помещенного в генераторе 2 тока, соединена с выходом первого делителя, причем первый делитель состоит из первого резистора 23, включенного между обеими клеммами 15 и 12 источника напряжения й соёдйненных друг с другом последовательно диодов 16 и 17. Нижнее звено кег(ЙТёУ1ЯГ содержащее диоды, параллель но соединено с диодами база - эмиттер транзистора 13. , ..- v Второй ступенью компаратора является дифференциальный усилительный Лйскад 4, состоящий из дифференциаль ного усилителя высокого быстродействия. .....„, ,. .,, ,.,.-,. -. Вход .дифференциального усилительного каскада 4 образо1в н ба.зами транзисторов 24 и 25 типа п-р-п дифференциального усилителя, а выход каскада соединен с коллекторами транзисторов 24 и 25. Включенные последовательно диоды 26-29 образуют коллекторные согтротивления транзисторов 24 и 25. Аноды диодов 26 и 27 или диодов 28 и 29 соединены через общий резистор 30 с первой клеммой 12 источника напряжения. Резистор 31 представляет собой генератор тока дифференциального усилительного каскада 4, он помещён между второй клеммой 15 источника напряжения и общими эмиттерами шестого и седьмого транзисторов 24 и 25. Также и оконечный усилительный каскад 5 содержит дифференциальный усилитель. Вход этого каскада образован базами помещенных в дифференциальном усилителе транзисторов 32 и 33 типа р-п-р, а выход каскада соединен с коллекторами транзисторов 32 и 33. Оконечный усилительный каскад 5 имеет генератор тока с разомкнутым коллектором, причем эмиттертранзистора 34 соединен через резистор 35 с первой клеммой 12 источника напряжения. База транзистора 34 присоединена к выходу второго делителя. Второй делитель состоит из резистора 35, включенного между клеммами 15 и 12, и соединенных между собой последовательно диодов 36 и 37. Делитель выполнен так, что диоды 36 и 37 делителя включаются параллельно с диодом база - эмиттер транзистора 34. Дифференциальный усилитель снабжен симметричным выходом. Резисторы 38 и 39, соединенные с корпусом, являются коллекторными сопротивлениями дифференциального усилителя. Вентильный каскад 6, передающий выходную нагрузку, соединен одним своим входом с выходом оконечного каскада, а другие входы предназначаются для селектирующих импульсов. Принцип работы данного компаратора и известных компараторов аналогичен. Различие входных сигналов усиливается входным каскадом 1. Полученный сигнал управляет дифференциальным усилительным каскадом 4 или оконечным усилительным каскадом 5. Все каскады выполнены таким образом или коллекторные нагрузки выбраны так, что рабочие точки активных элементов во всей области регулирования находятся S пределах линейной зоны, в результате чего не возникает перевозбуждения ИЛИ насыщения. При перерегулировании компаратбра переходный сигнал, поступающий на резистор 18, управляет через конденсатор блока ускорения транзистором 13 генератора тока, благодаря чему обеспечивается ускоренное переключение в обоих направлениях. Расположенные в делителях диоды компенсируют температурную зависимость генераторов тока. формула изобретения 1. Аналоговый компаратор, содержащий дифференциальный усилительный каскад с генератором тока в цепи эмиттеров транзисторов усилительного каскада, выходной оконечный каскад, выполненный на дифференциальном усилителе на транзисторах, коллекторы которых соединены со входом вентильного каскада, отличающийся тем,

что, с целью расширения йиапазона

входного напряжения без ухудшения быстродействия, в него введены второй дифференциальный усилительный каскад и блок ускорения, включенный между генератором тока и клеммой источника питания, причем базы транзисторов второго дифференциального усилительного каскада соединены с выходами дифференциального усилительного каскада, коллекторы соединены с базами транзисторов выходного оконечного каскада

и через последовательно соединенные диоды и резистор с оййой клеммой источника питания, а эмиттеры через резистор соёдинёШ с другой клеммой источника питания.

Источники информации, принятые во внимание при экспертизе 1. Зарубежная радиоэлектроника.

5 М., Сов. радио, 6, 1976, с.42 (прототип).

Авторы

Даты

1980-11-30—Публикация

1978-02-21—Подача